# Migrating S08 to Kinetis E MCU using KDS.

by: David Diaz Marin

# 1 Introduction

The migration between devices involves a lot of changes, one of these changes is the software.

The purpose of this document is to create a new KDS application and to mention the differences between S08 and Kinetis E devices.

Sample code and comparisons are shown along this document in order to know the main software considerations between the family devices mentioned.

|        | Content                                              |     |

|--------|------------------------------------------------------|-----|

| 1      | Introduction                                         | . 1 |

| 2      | Overview                                             | . 1 |

|        | 2.1 KDS                                              | . 1 |

| 3      | Creating a new Project using KDS                     | . 2 |

| 4<br>K | Differences between the S08 and the inetis E devices | . 4 |

|        | 3.1 HCS08 MCU Core vs Cortex M0+                     | . 4 |

|        | 3.2 Set of instructions                              | . 5 |

|        | 3.3 Memory Map                                       | . 5 |

|        | 3.4 Interrupt Controller                             | . 6 |

|        | 3.4.1 Nested Vectored Interrupt Controlle (NVIC)     |     |

|        | 3.5 Peripherals Differences                          | .8  |

|        | 3.5.1 Clock gate                                     | . 9 |

| 5      | References                                           | 10  |

Contant

# 2 Overview

#### **2.1 KDS**

The **Kinetis Design Studio** software development tool is a GNU/Eclipse-based development environment for Freescale Kinetis devices. It supports Cortex-M based Kinetis devices and integrates with Processor Expert and Kinetis Software Development Kit. KDS supports SEGGER J-Link/J-Trace, P&E USB Multilink Universal/USB Multilink Universal FX and CMSIS-DAP debug adapters and uses the newlib-nano C runtime library. This runtime library helps reduce the memory footprint of an embedded application.

In order to get more information about the IDE mentioned, please refer to the following link:

http://www.freescale.com/kds

# 3 Creating a new Project using KDS

The Kinetis Project wizard help you to quickly create new projects. The wizard generates a project with placeholder files and default settings (build and launch configurations) specific targets. After the project has been created, you can easily change any default setting to suit your needs.

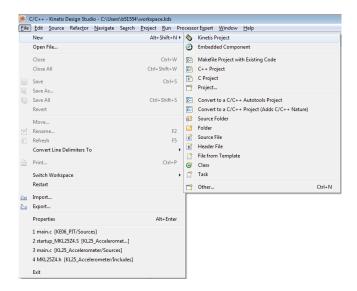

To create a Kinetis project using the New Kinetis Project wizard:

- 1. Launch the KDS.

- 2. Select **File > New > Kinetis Project**, from the IDE menu bar.

The Create a Kinetis Project page of the New Kinetis Project wizard appears.

- 3. Specify a name for the new project. For example, enter the project name as *Project1*.

- 4. Click Next.

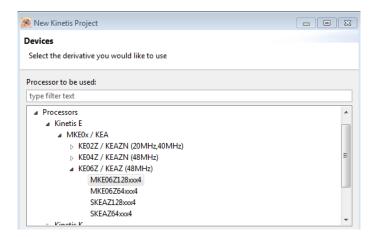

The Devices page appears.

5. Expand the desired tree control and select the derivative or board you would like to use. For example, select **Processors** > **Kinetis K** > **MKE0x** / **KEA** > **MKE06** / **KEAZ** (48 MHz) > **MKE06Z128xxx4**

#### Freescale Semiconductor

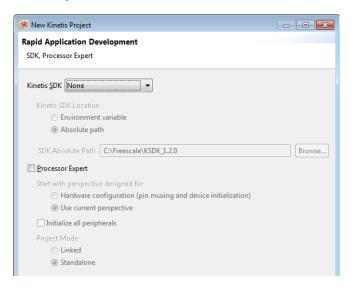

#### 6. Click Next.

The Rapid Application Development page appears. This page helps you to configure use Processor Expert for configuration and KSDK.

7. Select the default Kinetis SDK option to **None**.

#### 8. Click Finish

# 4 Differences between the S08 and the Kinetis E devices.

The comparison topics will reside in the most relevant differences between the devices. Sample code is included in some topics.

The discussed topics are:

- Core (HCS08 MCU Core vs. Cortex M0+).

- Set of Instructions (Number of instructions and clock cycles).

- Memory Map.

- Interrupt Controller.

- Peripherals Differences.

## 3.1 HCS08 MCU Core vs Cortex M0+

The following table show the difference regarding the corresponding Cores on the devices mentioned:

|           | HCS08 MCU                                                                                                                                                                                                                      | Cortex M0+                                                                                                                                                                                                                                             |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CPU       | <ul> <li>8-bit processor core</li> <li>68HC08 instruction set</li> <li>Up to 40 MHz Core Clock</li> </ul>                                                                                                                      | <ul> <li>32-bit embedded processor</li> <li>Thumb 2 instruction set</li> <li>Up to 48 MHz (today)</li> </ul>                                                                                                                                           |

| DEBUG     | <ul> <li>Background debug controller</li> <li>Non- intrusive software debugging</li> <li>Allow a user to read or write MCU memory locations or access status and control registers</li> <li>One hardware breakpoint</li> </ul> | <ul> <li>CoreSight debug and trace</li> <li>Non-intrusive – trace information</li> <li>Allows the user to read or write MCU memory locations or access status and control registers</li> <li>Up to 4 hardware breakpoints and 2 Watchpoints</li> </ul> |

| Interrupt | <ul> <li>Up to 39 Interrupt vectors</li> <li>Fixed vector priority. Highest priority at the bottom of the table</li> </ul>                                                                                                     | <ul> <li>16 system interrupts + up to 32 peripheral interrupts (KE06)</li> <li>Selectable 4 priority levels for peripheral interrupts</li> </ul>                                                                                                       |

## 3.2 Set of instructions

|                 | HCS08 MCU             | Cortex M0+                    |

|-----------------|-----------------------|-------------------------------|

| Instruction Set | HCS08 instruction set | ARMv6-M Thumb instruction set |

Example of instructions and clock cycles:

| Instruction        | HCS08 MCU                            | Cortex M0+ |

|--------------------|--------------------------------------|------------|

| Add with carry     | Immediate access mode                | • 1 cycle  |

|                    | 2 cycles                             |            |

| Jump to Subroutine | <ul> <li>Dir, with offset</li> </ul> | • Any      |

|                    | • 5 cycles                           | • 2 cycles |

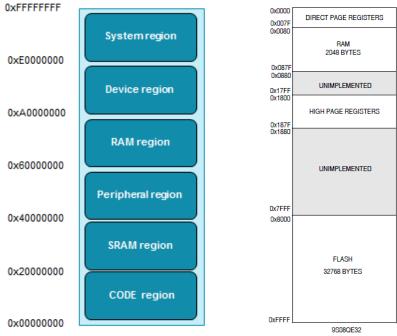

# 3.3 Memory Map

The main difference in the memory model is the way the addresses are accessed.

Kinetis vs S08 memory map

# 3.4 Interrupt Controller

|                           | HCS08 MCU                                                                                                                                             | Cortex M0+                                                                                                                                                                                    |

|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Exceptions and Interrupts | <ul> <li>Up to 39 maskable interrupts<br/>and 1 non-maskable.</li> <li>Fixed interrupt priority. Lowest<br/>vector number highest priority</li> </ul> | <ul> <li>Nested Vector interrupt controller.</li> <li>Up to 32 separate interrupt sources</li> <li>Four selectable interrupt priority levels</li> </ul>                                       |

| Vector Table              | <ul> <li>Located at fixed address in flash.</li> <li>Every vector contains the address of the interrupt handler.</li> </ul>                           | <ul> <li>Default address at 0x000000000</li> <li>Can be relocated during initialization.</li> <li>Each vector contains the starting address of the corresponding interrupt handler</li> </ul> |

| Interrupt handlers        | <ul> <li>ISRs end with a RTI (return-from-interrupt)</li> <li>Compiler directive to indicate the function is an ISR</li> </ul>                        | <ul> <li>Entry and Exit sequences<br/>supported in hardware.</li> <li>ISR routines written as<br/>standard C function</li> </ul>                                                              |

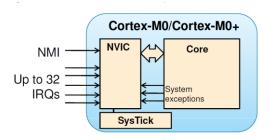

## 3.4.1 Nested Vectored Interrupt Controller (NVIC)

The NVIC is a standard module on the ARM Cortex M series. This module is closely integrated with the core and provides very low latency entering and exiting an interrupt service routine (ISR).

The NVIC provides four different interrupt priorities which can be used to control the order in which interrupts must be serviced. Priorities are 0-3, with 0 receiving the highest priority.

Configuring the NVIC for the specific module involves writing three registers:

- NVIC Set Enable Register (NVICSERx)

- NVIC Clear Pending Register (NVICCPRx)

- NVIC Interrupt Priority (NVICIPxx)

```

Sample Code

/* Set the ICPR and ISER registers accordingly */

NVIC_ClearPendingIRQ(PIT_CH1_IRQn);/* Clear pending interrupts*/

NVIC_EnableIRQ(PIT_CH1_IRQn); /* Enable interrupts*/

```

In this case the first two functions are used in order to enable interrupts and clear pending interrupts.

The interrupt priority is left by default.

Note:

The parameter PIT\_CH1\_IRQn is defined at the corresponding interrupt vector at the device header.

The bellow code shows the different Interrupt Handler:

# 3.5 Peripherals Differences

|                                     | HCS08 MCU                                                                                                                                                                                                                                                                                  | KE MCU                                                                                                                                                                                                                                                                                                                                          |

|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ICS<br>Internal Clock source        | • FLL selectable 512, 608,<br>1024, 1216, 1536, 1824<br>(QE)                                                                                                                                                                                                                               | FLL multiplication factor fixed to 1024                                                                                                                                                                                                                                                                                                         |

| SIM<br>System Integration<br>Module | <ul> <li>Includes Universal Unique Identifier (UUID)</li> <li>Pin remapping is controlled by the SIM_PINSEL register.</li> <li>There is no SIM_BUSDIV register. It cannot further divide bus clock and flash clock down.</li> <li>All peripheral clocks are enabled after reset</li> </ul> | <ul> <li>Includes fields for Kinetis Family ID, Sub-Family ID, Revision Number, and Device Pin ID.</li> <li>Pin remapping is controlled by the SYS_SOPT1 register in S08P. The bus clock can be further divided by 2 for both bus and flash clock via the SIM_BUSDIV register.</li> <li>All peripheral clocks are gated off at reset</li> </ul> |

| Flash Memory<br>Controller          |                                                                                                                                                                                                                                                                                            | <ul> <li>Support read-while-write.         Allowing read from flash         while programming/erasing         the flash.     </li> </ul>                                                                                                                                                                                                        |

| PinOut                              | BKGD pin for debug 8 high-<br>drive pins supporting<br>20 mA drive capability                                                                                                                                                                                                              | <ul> <li>SWD_DIO and SWD_CLK pins<br/>for debug</li> <li>8 high-drive pins supporting<br/>20 mA drive capability</li> </ul>                                                                                                                                                                                                                     |

| Port Control and GPIO               | <ul> <li>Access to it in 8 bit registers</li> </ul>                                                                                                                                                                                                                                        | <ul> <li>Access to it in 32 bit registers</li> <li>Improved access to registers</li> </ul>                                                                                                                                                                                                                                                      |

| ADC                                 | <ul> <li>SAR ADC</li> <li>ADC 12-bit result is read in more than one cycle</li> </ul>                                                                                                                                                                                                      | <ul> <li>SAR ADC</li> <li>ADC 12-bit result is read in just one cycle</li> </ul>                                                                                                                                                                                                                                                                |

| RTC<br>Real Time Clock              | 8 bit register access width                                                                                                                                                                                                                                                                | 32 bit register access width                                                                                                                                                                                                                                                                                                                    |

#### Freescale Semiconductor

| TMP/FTM                      | • TPM | FTM  Signed up counter  Dead time insertion hardware  Fault control inputs  Enhanced triggering functionality  Initialization and polarity control  |

|------------------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| PIT Periodic Interrupt Timer |       | <ul> <li>Array of timer channels</li> <li>32-bit module counter</li> <li>Each channel counts<br/>individually</li> <li>Interrupt support</li> </ul> |

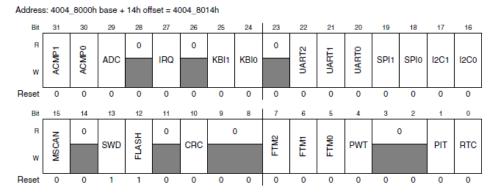

#### 3.5.1 Clock gate

One of the main differences between the devices mentioned is the clock setting.

At Kinetis, each clock module must be enabled using the SCGC register from the System Integration Module.

The system integration module (SIM) provides system control and chip configuration registers.

#### 12.2.6 System Clock Gating Control Register (SIM\_SCGC)

#### Sample Code

Please note that each clock module must be enabled using the SIM\_SCGC register.

Freescale Semiconductor

In regard with the rest of the modules, please refer to the Kinetis E Reference Manual and the sample codes attached to this document.

# 5 References

KE06 Reference manual.

http://www.freescale.com/files/microcontrollers/doc/ref manual/MKE06P80M48SF0RM.pdf

Migration Guide From S08 to Kinetis E Family. http://www.freescale.com/files/32bit/doc/app\_note/AN4757.pdf

Migration Guide From S08 to Kinetis L Series MCUs.

http://www.freescale.com/files/32bit/doc/app\_note/AN4662.pdf