- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- General Purpose Microcontrollers

- :

- LPC Microcontrollers

- :

- LPC11U68 secondary bootloader MTB conflicts with ram vectors?

LPC11U68 secondary bootloader MTB conflicts with ram vectors?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

LPC11U68 secondary bootloader MTB conflicts with ram vectors?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I created a secondary bootloader for the LPC11U68 chip which jumps to our main program at 0x4004.

In the main program I copy the interrupt vectors to an array set to a ram array set to be located at vtable.

int32_t vector_in_ram[AQUA_CPU_INTERRUPTS] __attribute__ ((section ("vtable")));

I then set the interrupts to be used from the ram.

LPC_SYSCTL->SYSMEMREMAP = 0x1;

My problem is that the LPC11U68 chip maps the MTB trace in the local SRAM starting at address 0x1000 0000.

The vtable is located by the link script to 0x10000300 whereas for my use it should be at the MTB trace address.

"When the MAP bits in the SYSMEMREMAP register are set to 0x0 or 0x1, the boot

ROM or RAM respectively are mapped to the bottom 512 bytes of the memory map

(addresses 0x0000 0000 to 0x0000 0200)."

How can I disable the MTB trace in release code and change the link script just to remove it leaving everything else as is?

In my project Preprocessor defines there is __MTB_BUFFER_SIZE=256.

I removed it and recompiled but it did not help.

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Another related question, please.

I tied to bypass the problem moving the interrupt vectors to ram in my main program by using interrupt jumps in my bootloader program. This I understand will add just the jump commands latency. My main program uses the USB rom serial code. I seem to have a problem using the bootloader jump method with the USB when my main program is located at 0x4000. The program seems to start and I can seem debug printout on an uart port but stalls apparently in the USB initialization. The main program works when located at address 0. I saw on the forum where there were problems with the CAN rom interface in a similar situation. It my just be a bug somewhere.

/*****************************************************************************

** Function name: USB_IRQHandler

**

** Description: Redirects CPU to application defined handler

**

** Parameters: None

**

** Returned value: None

**

*****************************************************************************/

void USB_IRQHandler(void)

{

/* Re-direct interrupt, get handler address from application vector table */

asm volatile("ldr r0, =0x4098");

asm volatile("ldr r0, [r0]");

asm volatile("mov pc, r0");

} // USB_IRQHandler

/*****************************************************************************

** Function name: USB_FIQHandler

**

** Description: Redirects CPU to application defined handler

**

** Parameters: None

**

** Returned value: None

**

*****************************************************************************/

void USB_FIQHandler(void)

{

/* Re-direct interrupt, get handler address from application vector table */

asm volatile("ldr r0, =0x409C");

asm volatile("ldr r0, [r0]");

asm volatile("mov pc, r0");

} // USB_FIQHandler

/*****************************************************************************

** Function name: USBWakeup_IRQHandler

**

** Description: Redirects CPU to application defined handler

**

** Parameters: None

**

** Returned value: None

**

*****************************************************************************/

void USBWakeup_IRQHandler(void)

{

/* Re-direct interrupt, get handler address from application vector table */

asm volatile("ldr r0, =0x40B8");

asm volatile("ldr r0, [r0]");

asm volatile("mov pc, r0");

} // USBWakeup_IRQHandler

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi David,

To disable the MTB feature, I have another idea, the LPC11U68 contains the Cortex M0+ core which integrates the Vector Table Offset Register (VTOR), it support to relocate the interrupt vector.

Hope it helps.

Have a great day,

TIC

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

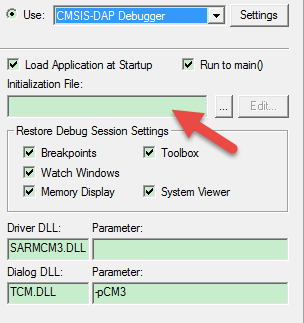

I could not find a Dbg_MTB in the NXP or my project directory nor could I find a dialog as in the photo.

I use the MCUXpresso IDE v10.1.1_606 IDE and just need to remove the MTB stuff if possible from my release (not debug) link script so that I can use the ram interrupt vector which I understand start a 0x0 in the ram.

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi David Kaplan,

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------