- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- Product Forums

- :

- MPC5xxx

- :

- Re: Re-initializing CLK settings

Re-initializing CLK settings

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Re-initializing CLK settings

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

We are working with MPC5744P. In the application we have configured the PLL0 to be 160 MHz and PLL1 to be 200 MHz and out SYSCLK is based on PLL1(200 MHz). When we work with just the application, we correct see the tasks executing periodically, meaning 10ms tasks are executed every 10ms.

But, when we work with bootloader and the application, the see that the tasks executing at a different rate, meaning 10ms tasks are executed every 6.5ms. I believe clock settings are different in bootloader.

Questions:

Is there any way that we can re-initialize properly the clock setting in application? We are though initializing the correct settings that we want but I think it is not taking any effect. So, I was wondering if we can do at anytime? If we can, how would that be done?

Please note that, we don't access to bootloader as it is delivered by our supplier. I could ask them but I would like to have an option to change them in the application as well.

Thanks in advance.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

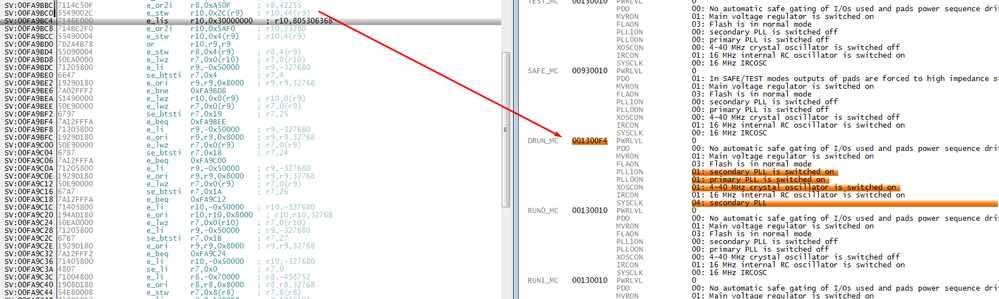

I've done debugging on your assembly code and I can see issue with mode transition at first:

see following pictures:

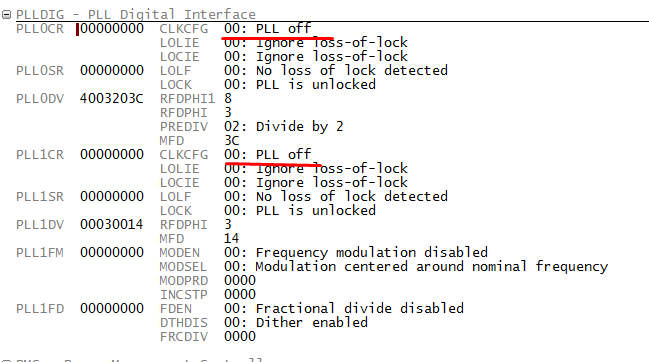

1. you have your PLL's off

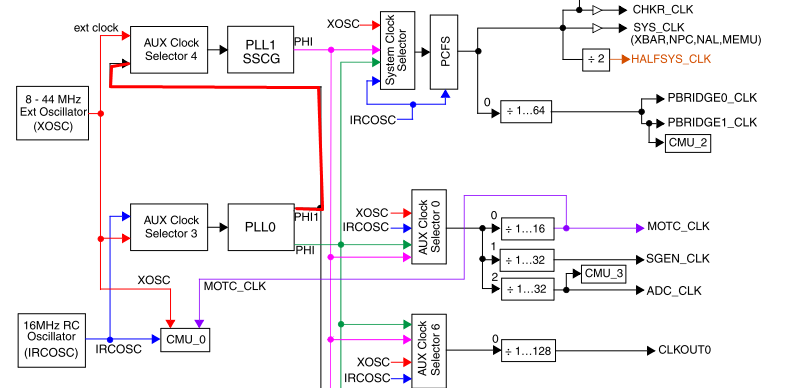

2. You are connecting PLL0 PHI1 to AUX4 input for PLL1 generation:

3. But you have no PLL0 signal in this time.

4. The DRUN is your target mode and you are enabling both PLL's. PLL0 as source of PLL1 while you have no PLL0.

Your mode transition will fail and your system clock will stay IRC 16MHz. (I guess this is what you measure on output pin).

Solution:

----------

1. Configure PLL0 , do mode transition. (PLL1 disabled in ME_MC_DRUN)

2. Enable PLL1 in DRUN mode and do mode transition again

This is also described in Reference manual.

You can also use our PLL calculator :Excel MPC5744P Clock Configurator

which generates code depending on Clock configuration.

Peter

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks Peter. I hope you have checked BootApplication.S19.

The application itself works correctly but it does not work in BootApplication.S19. I will cross verify these again and see what is happening.

Thanks for your time.

- Sagar

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yes,

I have checked bootapplicaiton.s19

and this is what I can see.

Peter

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

"Is there any way that we can re-initialize properly the clock setting in application?"

I expect every application first configure device (clocks, wait-states, peripherals, etc..) and then it starts executing application tasks.

Always verify is the change has taken effect before processing to the tasks.

You don't have touch bootloader. After bootloader execution finishes, you have to just simple do micro initialization in application.

Configure clocks according to your needs.

Peter

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Peter,

Thanks for responding. Yes, after bootloader finishes its execution, we are re-initializing in application; configuring the clocks as needed but it is not taking effect.

I got clarification from our supplier that they also use the same PLL and SYSCLK settings as we do. I don't understand why would they differ in behavior!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

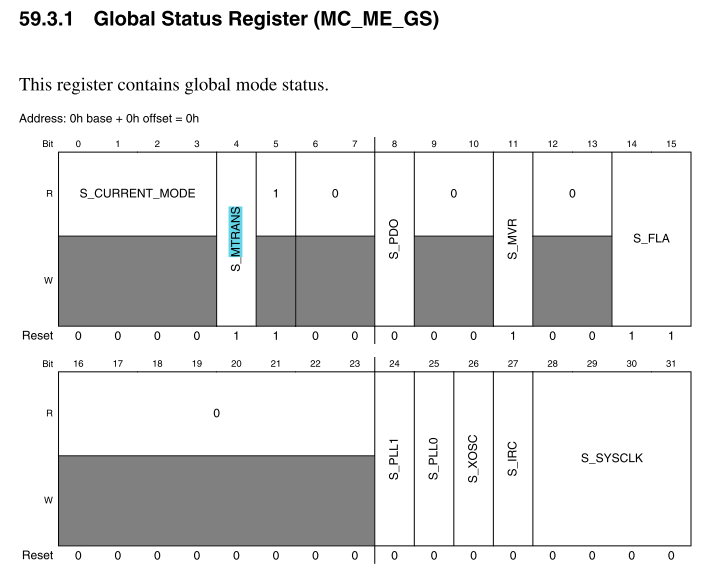

What do you see in MTRANS after your application mode change?

Did your micro takes mode change successfully?

Can you see on CLKOUT correct system clock.

Peter

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

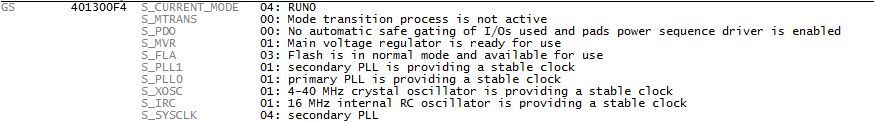

It is 00 in both cases. Following is the register structure.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

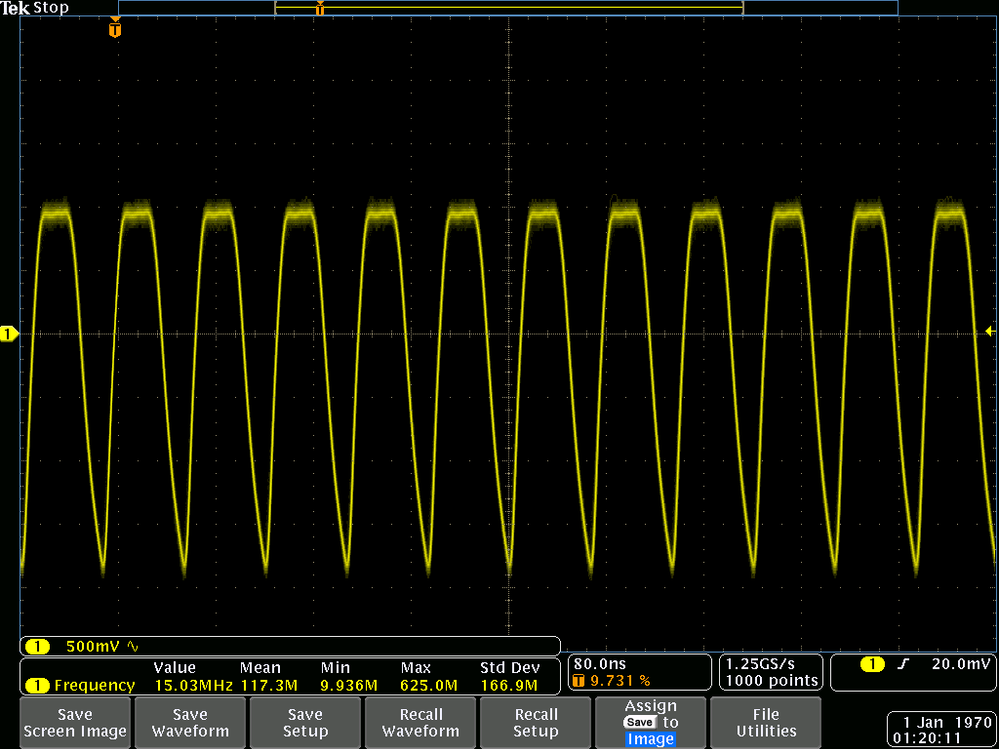

Here is what I measured CLK_OUT from both scenarios.

1. CLK_OUT when just application is run. You can see that frequency is 10MHz. With MFD = 20, SYSCLK=200MHz.

2. CLK_OUT when bootloader and application is run. See that the frequency is 15MHz. I don't know what is MFD here and hence do not know that is SYSCLK. As per our supplier's statement, they say they have the same configuration as we do. So, something is not right. MFD cannot be 20 because 20*15MHz=300MHz, SYSCLK is not possible for this micro.

Please let me know if I have misunderstood anything wrong.

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Here is an update:

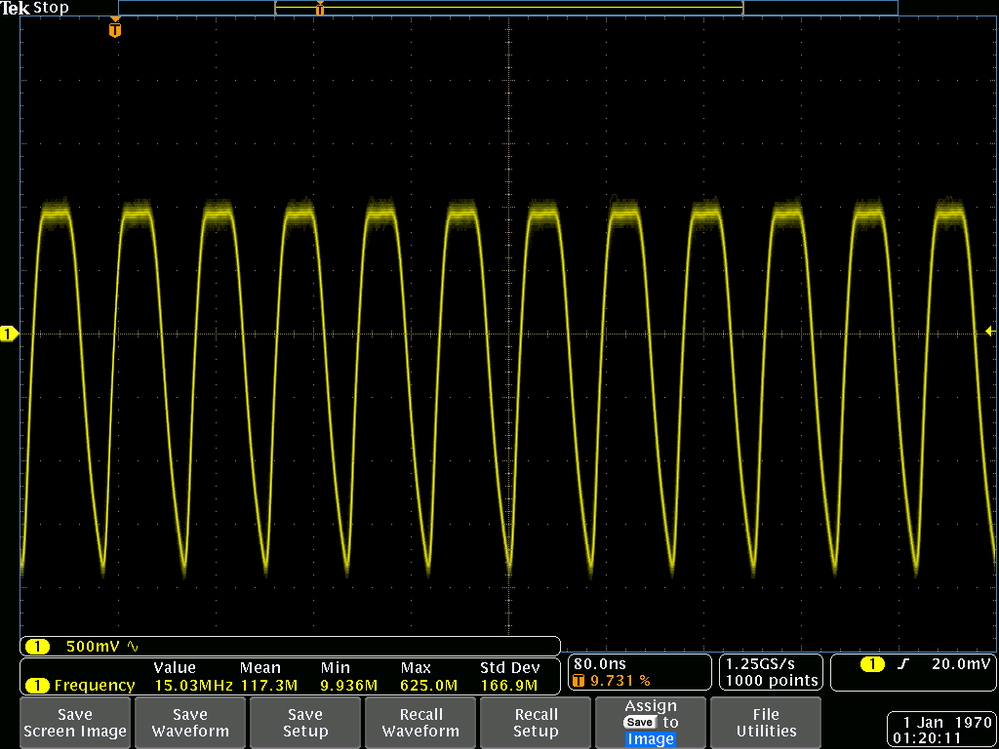

When bootloader is ran, CLK_OUT is as follows:

(MFD=10. So, 20MHz * 10 = 200MHz)

When Application is ran, CLK_OUT is as follows:

(MFD=20. So 10MHz * 20 = 200MHz)

When both bootloader and application is ran, CLK_OUT is as follows:

It looks like MFD is getting averaged. I don't know what exactly is happening.

Can someone help me please?

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Ok,

When you measure 15Mhz (bootloader and application run) check the configuration of CGM (clock generation module) and check also settings of PLL.

Or send me your output file and i will check it. (the failing scenario)

Frequency always corresponds to clock configuration. (if you measure it directly on CLKOUT pin)

Peter

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for replying.

Sure, I am attaching all output files. Also, following are the details.

Bootloader:

Output file name: Bootloader.S19

PLLDIG_PLL0DV=0x4003203C;

PLLDIG_PLL1DV=0x00030014;

CLK_OUT = 20 MHz

Application:

Output file name: Application.S19

PLLDIG.PLL0DV.R = 0x40021014;

PLLDIG.PLL1DV.R = 0x00020014;

CLK_OUT = 10 MHz

Bootloader + Application:

Output file name: BootApplication.S19

CLK_OUT = 15 MHz.

** This is the failing scenario **

Thanks for the help.