- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- LVDS crtc field and connection to framebuffer

LVDS crtc field and connection to framebuffer

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I am working on connecting an LVDS to my project, with no success as of yet. I am a bit lost when it comes to the crtc field in the device tree.

I am working off kernel 3.14.79

I have modified the hummingboard2 device tree's entry for ldb to suit the timings of my display, to look like this:

/* old mxcfb1 setting for HDMI - POSTED here for clarity */

/*

mxcfb1: fb@0 {

compatible = "fsl,mxc_sdc_fb";

disp_dev = "hdmi";

interface_pix_fmt = "RGB24";

mode_str ="1920x1080M@60";

default_bpp = <32>;

int_clk = <0>;

late_init = <0>;

status = "okay";

};*/

/* new fb1 setting for LVDS */

&mxcfb1 {

disp_dev = "ldb";

interface_pix_fmt = "RGB666";

default_bpp = <16>;

int_clk = <0>;

late_init = <0>;

mode_str ="1280x720M@60";

status = "okay";

};&ldb {

status = "okay";lvds-channel@0 {

crtc = "ipu1-di0"; // ipu2-di0 has errors in dmesg on boot/* Ive observed the following properties in other posts, which I assume

* are specific to splitting the LVDS due to larger displays and the limitations of the clock

* but I am unsure if its necessary for a singular display */

ipu_id = <0>;

disp_id = <1>;

ext_ref = <1>;

mode = "sin0";

sec_ipu_id = <0>;

sec_disp_id = <0>;

status = "okay";display-timings {

native-mode = <&timing0>;/* overwrite timings for Tianma TM070JDHG30 */

timing0: hsd100pxn1 {

clock-frequency = <75210590>;

hactive = <1280>;

vactive = <720>;

hback-porch = <5>;

hfront-porch = <64>;

vback-porch = <2>;

vfront-porch = <40>;

hsync-len = <69>;hsync-len = <69>;

vsync-len = <42>;

}; // ~timing0

}; // ~display-timings

}; //~lvds-channel@0

}; // ~ldb

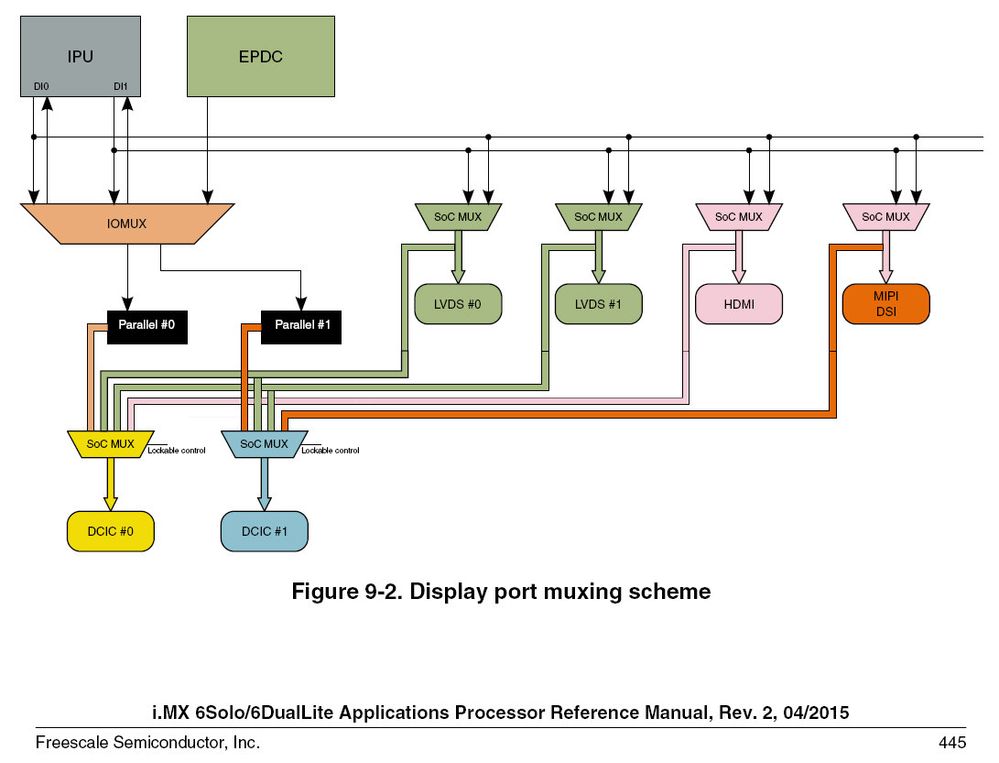

I've read that the crtc is supposed to point to the IPU device to connect the LVDS to, but I cannot find any documentation on this property, and/or what other supporting nodes need to be configured for this to work.

as i mentioned in the comment ipu2_di0 provides errors in dmesg (invalid or unspecified crtc), but ipu1_di0 seems to run okay in the dmesg:

[ 0.414411] mxc_sdc_fb fb.32: registered mxc display driver ldb IPU1_DISP0

[ 0.414424] mxc_sdc_fb fb.32: registered mxc display driver ldb

To summarize :

I can't get my LVDS working, and at this point everything I try is a shot in the dark, so my basic questions are:

1) What value should I be putting for the crtc property?

2) What other supporting (device tree or other) configurations are needed to support the crtc property?

3) How does this magically link to a frame buffer? Thus far I've been catting' to the frame buffers to see if theres any changes on my displays, but have yet to have any luck.

Thanks in advance

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

For a sense of completion, I was able to get it working!

My problem was a hardware problem. After that was solved and a slight timing adjustment, using boundary device's timing for the Tianma (I'm using the same display, but not their Boundary U-Boot). For those struggling, here is my device tree node:

&ldb {

status = "okay";

lvds-channel@0 {

crtc = "ipu1-di0";

ipu_id = <0>;

disp_id = <0>;

status = "okay";

fsl,data-width = <24>;

display-timings {

native-mode = <&timing1>;

timing1: tianma {

clock-frequency = <68152388>;

hactive = <1280>;

vactive = <800>;

hback-porch = <5>;

hfront-porch = <63>;

vback-porch = <2>;

vfront-porch = <39>;

hsync-len = <1>;

vsync-len = <1>;

}; //~display-timings

}; //~display-timings

};//~lvds-channel

};//~ldb

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

For a sense of completion, I was able to get it working!

My problem was a hardware problem. After that was solved and a slight timing adjustment, using boundary device's timing for the Tianma (I'm using the same display, but not their Boundary U-Boot). For those struggling, here is my device tree node:

&ldb {

status = "okay";

lvds-channel@0 {

crtc = "ipu1-di0";

ipu_id = <0>;

disp_id = <0>;

status = "okay";

fsl,data-width = <24>;

display-timings {

native-mode = <&timing1>;

timing1: tianma {

clock-frequency = <68152388>;

hactive = <1280>;

vactive = <800>;

hback-porch = <5>;

hfront-porch = <63>;

vback-porch = <2>;

vfront-porch = <39>;

hsync-len = <1>;

vsync-len = <1>;

}; //~display-timings

}; //~display-timings

};//~lvds-channel

};//~ldb

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Dan

what processor used in the case, as i.MX6DL has only one IPU,

while i.MX6Q - two. For crtc one can look at ldb driver in

linux/drivers/video/fbdev/mxc/ldb.c and description in attached Linux Manual.

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

igorpadykov Its an i.MXDL. I have discovered there were hardware issues. I am working to resolve those and then will revisit. In the meantime, it may be a silly question, but is it possible to use the same IPU to provide the same data to two displays simultaneously ? i.e. to HDMI and LVDS ?

EDIT:

nevermind. I see all variants support dual displays here.

https://www.solid-run.com/freescale-imx6-family/imx6-som/imx6-som-specifications/

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Dan

please look at

Best regards

igor