- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- Product Forums

- :

- MPC5xxx

- :

- Re: eDMA problem in S32R274?

eDMA problem in S32R274?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear NXP engineer:

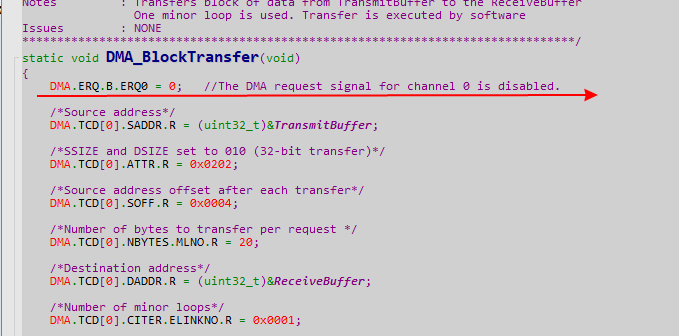

I want to use the eDMA module of S32R274,I refrence the exmaple Example MPC5775K-DMA_Transfer S32DS ,For this sentence,as follows:

Why disable it ,if do as this,Will it still transfer successfuly?

Aand additionally question:Whether FlexCAN in S32R274 could use a eDMA request?

Sincerely hope to get your help,thanks!

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

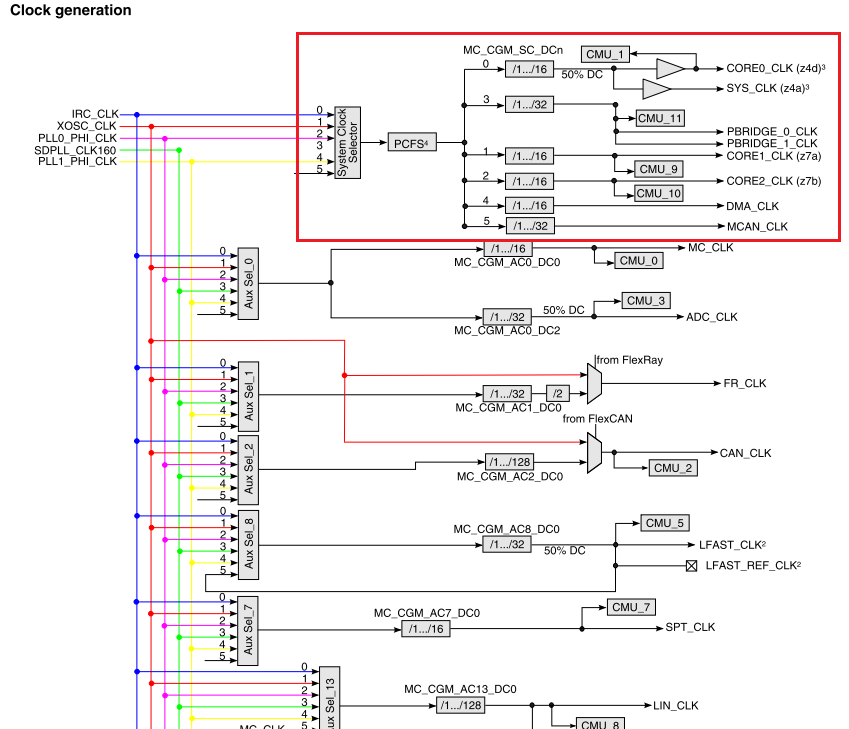

PBRIDGE_0_CLK is derived from System Clock which is 264MHz (PLL0).

PBRIDGE_0_CLK is set by MC_CGM_SC_DC_3 register. DIV bits in this register are set to 3 by default, so divider is 4. This tells you that PBRIDGE clock is 66MHz (PLL0/4 ....264/4=66)

Please ignore SC_CGM_AC13 register settings. This is not related to PBRIDGE clock settings.

2) In general, this bridge allows masters to access (write and read) the slaves. So, if DMA (master) wants to access to UART (slave), this must be enabled in AIPS bridge. Please read chapter 22 in MPC5775K reference manual.

3) It could be little bit complicated. At first, check if you have correctly configured pins and if the the pins you configured are routed to UART transceiver. Second, try to send characters without DMA and check, if it works. If yes, check DMA settings. If no, there will be most probably some issue with pad settings.

Regards,

Martin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

In this case apparently transfer is initiated software way thus DMA hardware request does not need to be enabled.

The eDMA requests for FlexCAN are not supported on this device.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hello David:

I need to use uart in edma way in S32R274,I refrence the exmapleExample MPC5775K UART_with_DMA S32DS ,I have some question about this example.

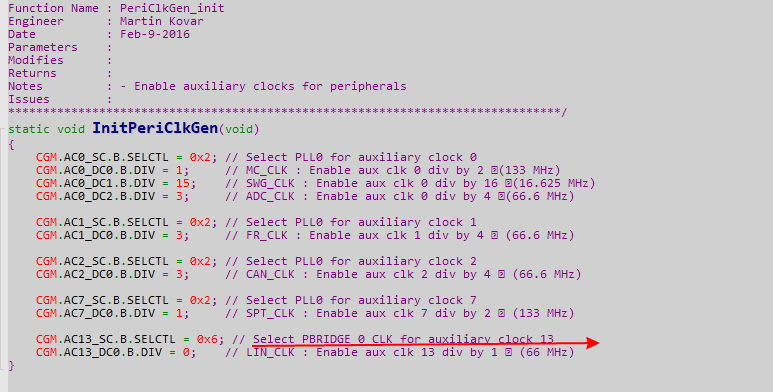

1:Why baud clock is 66MHz (PBRIDGE_CLK)?It seems that PBRIDGE_0_CLK is not configured,it is only configured PLL0

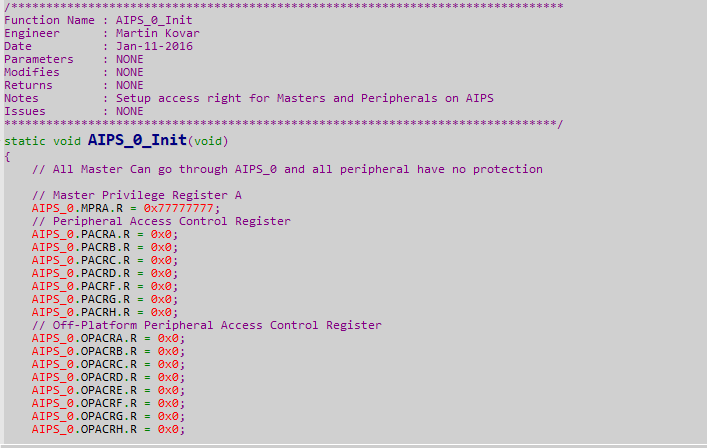

2:Why must be configured APIS_0,APIS_1?What function do they have?

3:I transplanted it to SR274, but did not succeed, the data did not send out from uart, do you have any good debugging advice?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

PBRIDGE_0_CLK is derived from System Clock which is 264MHz (PLL0).

PBRIDGE_0_CLK is set by MC_CGM_SC_DC_3 register. DIV bits in this register are set to 3 by default, so divider is 4. This tells you that PBRIDGE clock is 66MHz (PLL0/4 ....264/4=66)

Please ignore SC_CGM_AC13 register settings. This is not related to PBRIDGE clock settings.

2) In general, this bridge allows masters to access (write and read) the slaves. So, if DMA (master) wants to access to UART (slave), this must be enabled in AIPS bridge. Please read chapter 22 in MPC5775K reference manual.

3) It could be little bit complicated. At first, check if you have correctly configured pins and if the the pins you configured are routed to UART transceiver. Second, try to send characters without DMA and check, if it works. If yes, check DMA settings. If no, there will be most probably some issue with pad settings.

Regards,

Martin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Martin,

Follow your suggestion,I have used uart with edma ways to send a data .But I still have a question, Excepting EDMA that use AIPS, where there will be used AIPS?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Every master must be enabled on AIPS bridge to access slave (read, write). Some of them are enabled by default, another ones must be enabled by application. Please check AIPS_MPRA and AIPS_MPRB registers.

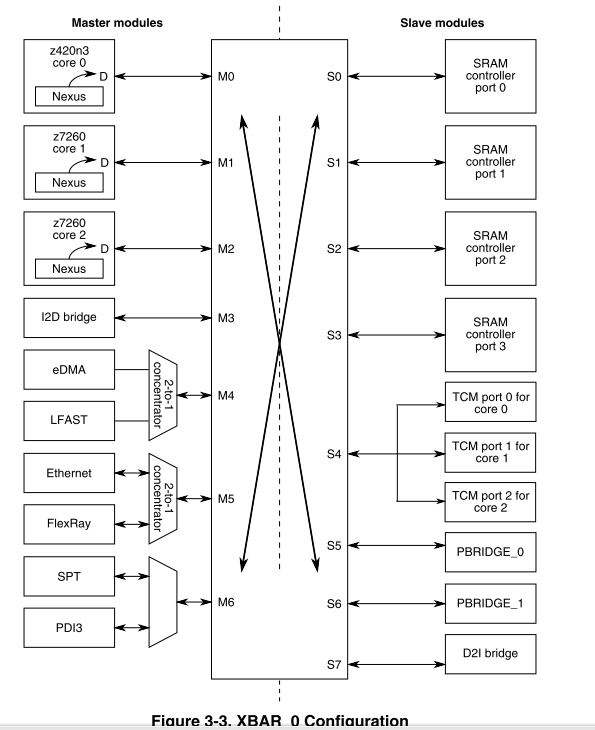

For Master logical numbers, please check Figure3-3 and table 3-8.

Regards,

Martin