- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- QorIQ Processing Platforms

- :

- P-Series

- :

- PCIE INTx issue

PCIE INTx issue

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

PCIE INTx issue

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

env: p2041--rc;

p1011-ep;

step:

1. p2041 connect the intx;

intConnect((VOIDFUNCPTR *) (0x2a), isrPCIE, 0);

intEnable(0x2a);

2. p1011 send intx message to 2041

p1011 mem32Addr=0xa0000000;

PEXOWAR0[WTT] = 0x5.

*(unsigned int*)0xa0000000 = 0x20040000;

3. p2041 cannot come int the isrPCIE ?

would you please give me some suggestions?

p2041--access the p1011 as follow:

vendor ID = 0x1957-

device ID = 0x0108

command register = 0x0006-

status register = 0x0010

revision ID = 0x11

class code = 0x0b

sub class code = 0x20

programming interface = 0x01

cache line = 0x10

latency time = 0x00

header type = 0x00

BIST = 0x00

base address 0 = 0xc4000000

base address 1 = 0xc0000008

base address 2 = 0xc4100004

base address 3 = 0x00000000

base address 4 = 0x00000000

base address 5 = 0x00000000

cardBus CIS pointer = 0x00000000

sub system vendor ID = 0x0000

sub system ID = 0x0000

expansion ROM base address = 0x00000000

interrupt line = 0x2a

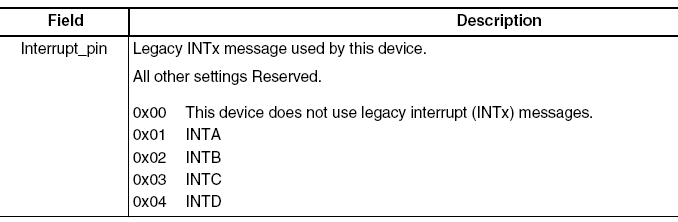

interrupt pin = 0x01

min Grant = 0x00

max Latency = 0x00

Capabilities - Power Management

Capabilities - PCIe: Endpoint, IRQ 0

Device: Max Payload: 256 bytes, Extended Tag: 5-bit

Acceptable Latency: L0 - <64ns, L1 - <1us

Errors Enabled: Relaxed Ordering No Snoop

Max Read Request 512 bytes

Link: MAX Speed - 2.5Gb/s, MAX Width - by 4 Port - 0 ASPM - L0s

Latency: L0s - <2us, L1 - >64us

ASPM - Disabled, RCB - 64bytes

Speed - 2.5Gb/s, Width - by 1

Ext Capabilities - Advanced Error Reporting. 0x100. Version 1. AER Control: 0xa0

Uncorrectable : Mask 0x0. Severity 0x62010

Uncorrectable Status:

Correctable : Mask 0x0.

Correctable Status:

HeaderLog:

Error Source Identification: 0x0 0x0

Capabilities - Message Signaled Interrupts: 0x70 control 0x88 Disabled, 64-bit, MME: 0 MMC: 4

Address: 0000000000000000 Data: 0x0000

Per-vector Mask: Unsupported

value = 0 = 0x0

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You wrote:

> *(unsigned int*)0xa0000000 = 0x20040000;

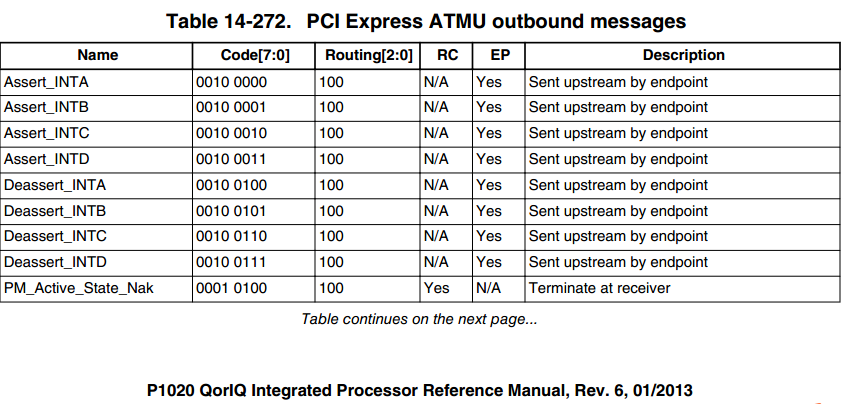

For the Assert_INTA message the operation should be:

*(unsigned int*)0xa0000000 = 0x8020;

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

how to get the value?

For the Assert_INTA message the operation should be:

*(unsigned int*)0xa0000000 = 0x8020;

i send the message 0x8020, but the result is the same......

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Message data[16-18] = Routing[2:0]

Message data[24-31] = Code[7:0]

INTA example:

Message data (big-endian, binary) = 0000_0000_0000_0000_1000_0000_0010_0000

> i send the message 0x8020, but the result is the same......

Check settings of the P2041 MPIC.

What are values of the GCR, CTPR0 and corresponding EIVPRn?

Which PCIe controller of the P2041 is used?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

thanks for your help.

p2041--pcie3 connect the p1011 pcie1.

P2041- Reg[gcr]=0x2000_0000; Reg[ctpr]=0x0000_0000; Reg[eivpr0]=0x80c0_0000;

follw the pcie information:

interrupt line = 0x2a

interrupt pin = 0x01

we use the inta interrupt, which is not the external interrupt.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

> Reg[eivpr0]=0x80c0_0000;

This means that MSK=1 and PRIORITY=0.

Possible correct value can be 0x00410000.

Concerning the EIVPR0[P] value :

Note that it is possible to share IRQn and INTx if the external interrupt is level sensitive;

however, if an interrupt occurs, the interrupt service routine must poll both the external

sources connected to the IRQn input and the PCI Express INTx sources to determine

from which path the external interrupt came. In any case, IRQn should be pulled to the

negated state as determined by the associated polarity setting in EIVPRn[P].

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

eivpr is External interrupt n (IRQn) vector/priority register.

we use the inta---which is internal interrupt.

intb\intc\intd is the eivpr.

i donot known how to work next step...

Can I modiy the INTA\intb\intc\intd mode? the regiser of p1011 header type0 interrupt_pin is read only?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Sorry, what is the IIVPR24 value?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

we use the 26 PCI Express 3 INTA.

reg[IIVPR-26]= 8080_0000;

when execute the intconnect ,then reg[IIVPR-26]= 0083_002a;

when p1011 send the msg 0x8020, the reg[IIVPR-26] of p2041 = 8083_002a;

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

> when execute the intconnect ,then reg[IIVPR-26]= 0083_002a;

This looks correct.

> when p1011 send the msg 0x8020, the reg[IIVPR-26] of p2041 = 8083_002a;

Why MSK is set? There will be no interrupt event in this case.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

> when p1011 send the msg 0x8020, the reg[IIVPR-26] of p2041 = 8083_002a;

Why MSK is set? There will be no interrupt event in this case.

I donot the reason. Does it means the p2041 has captured the msg 0x8020 from the p1011?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yes, I think so.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

ok, Why MSK is set? why the p2041 canot come in the isr???? the msg is error?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Please debug the interrupt handler code.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

i read the register:

Reg[IILR-26]=0X0000_0000;

Reg[IIDR-26]=0x0000_0000;

does it meas p2041 cannot receive this interrupt.

how to debug the interrupt handler code? any suggestion , thanks very much.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Sorry, I'm hardware engineer.

Let's check that the INTA message is received.

You wrote:

> when execute the intconnect ,then reg[IIVPR-26]= 0083_002a;

Please modify the value to 0x0080_0000 and generate the INTA message.

What is the register value after that?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

thank for your help.

1. p2041 execute the intconnect, then I modify the reg[IIVPR-26]=0080_0000;

2. p1011 send msg 0x8020;

3. p2041 check the reg[IIVPR-26] , the value is 0080_0000;

reg[IIDR-26]=0000_0001

reg[IILR-26]=0000_0000

reg[MCSR1]=0000_0000

reg[IRQSIESR1]=0000_0000

reg[IACK]=0000 00ff

it menas the p2041 does not recved the inta?

i donot known the reason....

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

thank for your great help.

1. p2041 execute the intconnect, then I modify the reg[IIVPR-26]=0080_0000;

2. p1011 send msg 0x8020;

3. p2041 check the reg[IIVPR-26] , the value is 0080_0000;

reg[IIDR-26]=0000_0001

reg[IILR-26]=0000_0000

reg[MCSR1]=0000_0000

reg[IRQSIESR1]=0000_0000

reg[IACK]=0000 00ff

it menas the p2041 does not recved the inta?

i donot known the reason....