- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- Product Forums

- :

- MPC5xxx

- :

- Re: About the MPC5634m eMIOS input capture and output compare

About the MPC5634m eMIOS input capture and output compare

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

About the MPC5634m eMIOS input capture and output compare

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, Guys

I want to use the input caputure and output compare function in MPC5634m, but the code cannot realize the functions. Can you find the fault in my code? Thank you

//input capture

#include "MPC5634M_MLQC80.h"

unsigned int i=0;

unsigned int time1;

unsigned int time2;

unsigned int shuju[8];

void pll_init_80M(void)

{

FMPLL.SYNCR.R = 0x03080030; /* Initial setting: 40 MHz for 8 MHz crystal */

while (FMPLL.SYNSR.B.LOCK != 1) {}; /* Wait for LOCK = 1 */

FMPLL.SYNCR.R = 0x03080430; /* Enable FM */

while (FMPLL.SYNSR.B.LOCK != 1) {}; /* Wait for FMPLL to LOCK again */

FMPLL.SYNCR.R = 0x03000430; /* Final setting: 80 MHz for 8 MHz crystal */

}

void pll_init_64M(void)

{

FMPLL.SYNCR.R = 0x03080030; /* Initial setting: 40 MHz for 8 MHz crystal */

while (FMPLL.SYNSR.B.LOCK != 1) {}; /* Wait for LOCK = 1 */

FMPLL.SYNCR.R = 0x03080430; /* Enable FM */

while (FMPLL.SYNSR.B.LOCK != 1) {}; /* Wait for FMPLL to LOCK again */

FMPLL.SYNCR.R = 0x16000000; /* Final value for 64 MHz: RFD=0 */

}

void initEMIOS(void)

{

EMIOS.MCR.B.GPRE= 63; /* Divide 64 MHz sysclk by 63+1 = 64 for 1MHz eMIOS clk*/

EMIOS.MCR.B.ETB = 0; /* External time base is disabled; Ch 23 drives ctr bus A */

EMIOS.MCR.B.GPREN = 1; /* Enable eMIOS clock */

EMIOS.MCR.B.GTBE = 1; /* Enable global time base */

EMIOS.MCR.B.FRZ = 0;

}

void initEMIOSch2(void)

{ /* EMIOS CH 9: Output Pulse Width Modulation */

EMIOS.CH[2].CCR.B.BSL = 0x3; /* Use internal counter */

EMIOS.CH[2].CCR.B.FEN = 1;

EMIOS.CH[2].CCR.B.EDSEL = 0; /*Single edge triggering defined by the EDPOL bit*/

EMIOS.CH[2].CCR.B.EDPOL = 0; /*Trigger on a falling edge*/

EMIOS.CH[2].CCR.B.MODE = 0x02; /* MPC551x, MPC563x: Mode is SAIC*/

SIU.PCR[181].R = 0x0500; /* Initialize pad for eMIOS chan. 2 output */

}

void EMIOS_RX_ISR(void)

{

while(EMIOS.GFR.B.F2==0){ };

time1=time2;

time2=EMIOS.CH[2].CADR.R;

shuju[i] = time2-time1;

i++;

if(i>7)

i=0;

}

void main(void)

{

pll_init_64M();

initEMIOS();

initEMIOSch2();

INTC_InstallINTCInterruptHandler(EMIOS_RX_ISR,53,10);

/* Loop forever */

for (;;)

{

}

}

//output compare

#include "MPC5634M_MLQC80.h"

void pll_init_80M(void)

{

FMPLL.SYNCR.R = 0x03080030; /* Initial setting: 40 MHz for 8 MHz crystal */

while (FMPLL.SYNSR.B.LOCK != 1) {}; /* Wait for LOCK = 1 */

FMPLL.SYNCR.R = 0x03080430; /* Enable FM */

while (FMPLL.SYNSR.B.LOCK != 1) {}; /* Wait for FMPLL to LOCK again */

FMPLL.SYNCR.R = 0x03000430; /* Final setting: 80 MHz for 8 MHz crystal */

}

void pll_init_64M(void)

{

FMPLL.SYNCR.R = 0x03080030; /* Initial setting: 40 MHz for 8 MHz crystal */

while (FMPLL.SYNSR.B.LOCK != 1) {}; /* Wait for LOCK = 1 */

FMPLL.SYNCR.R = 0x03080430; /* Enable FM */

while (FMPLL.SYNSR.B.LOCK != 1) {}; /* Wait for FMPLL to LOCK again */

FMPLL.SYNCR.R = 0x16000000; /* Final value for 64 MHz: RFD=0 */

}

void initEMIOS(void)

{

EMIOS.MCR.B.GPRE= 63; /* Divide 64 MHz sysclk by 63+1 = 64 for 1MHz eMIOS clk*/

EMIOS.MCR.B.ETB = 0; /* External time base is disabled; Ch 23 drives ctr bus A */

EMIOS.MCR.B.GPREN = 1; /* Enable eMIOS clock */

EMIOS.MCR.B.GTBE = 1; /* Enable global time base */

EMIOS.MCR.B.FRZ = 0;

}

void initEMIOSch2(void)

{ /* EMIOS CH 2: Output Pulse Width Modulation */

EMIOS.CH[2].CADR.R = 100; /*match value*/

EMIOS.CH[2].CCR.B.BSL = 0x3; /* Use internal counter */

EMIOS.CH[2].CCR.B.EDSEL = 1; /* the output flip-flop is toggled at each match*/

EMIOS.CH[2].CCR.B.EDPOL = 1; /* Polarity-leading edge sets output/trailing clears*/

EMIOS.CH[2].CCR.B.MODE = 0x03; /* MPC551x, MPC563x: Mode is SAOC */

SIU.PCR[181].R = 0x0600; /* Initialize pad for eMIOS chan. 2 output */

}

void initSIU(void)

{

SIU.PCR[187].R = 0x0203;

}

int main(void) {

volatile int i = 0;

pll_init_64M();

initEMIOS();

initEMIOSch2();

initSIU();

/* Loop forever */

for (;;)

{

SIU.GPDO[187].R = 0;

if(EMIOS.CH[2].CADR.R == EMIOS.CH[2].CCNTR.R)

{

EMIOS.CH[0].CSR.B.FLAG =1;

SIU.GPDO[187].R = 1;

}

if(EMIOS.CH[2].CADR.R == EMIOS.CH[2].CCNTR.R)

EMIOS.CH[0].CSR.B.FLAG =1;

}

}

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

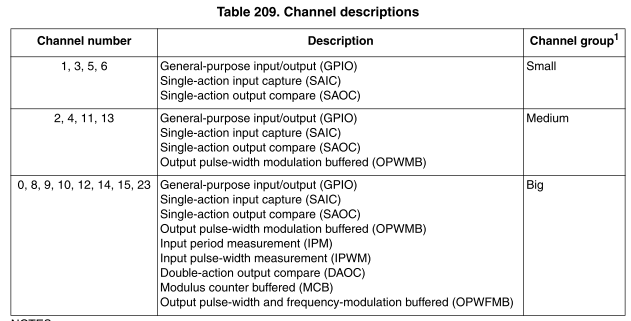

Channel 2 (medium channel) does not have internal counter, so cannot run from it.

So either select channel from the big group or select other counter bus for the channel 2 using CCR[BSL].

You can refer to the SAIC example in the following thread: https://community.nxp.com/message/605675

BR, Petr

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

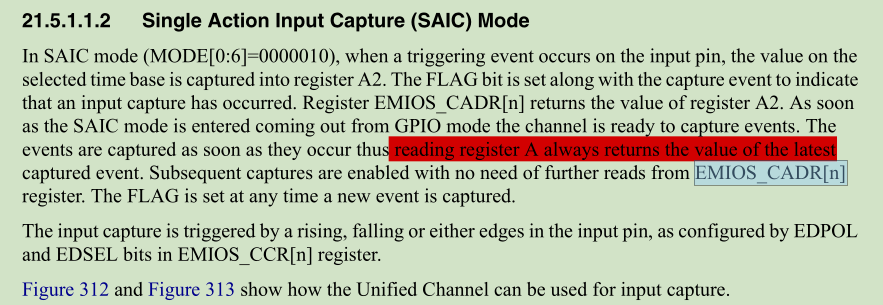

but the emios[2] have SAIC(Single Action Input Capture)MODE ,this mode could return EMIOS_CADR[n]. But I cannot read the change of EMIOS_CADR[n]. How to exlplain it?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

can you tell me that how to set the time for one count?

for eample 1count=1us

Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Rong,

the example I pointed to (https://community.nxp.com/message/605675) sets eMIOS global clock to 1MHz.

BR, Petr

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you for your response, it is really helpful for me, Thank you.