- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- i.MX フォーラム

- :

- i.MXプロセッサ

- :

- Re: GPIO set and clear time duration in u-boot in IMX6

GPIO set and clear time duration in u-boot in IMX6

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

GPIO set and clear time duration in u-boot in IMX6

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

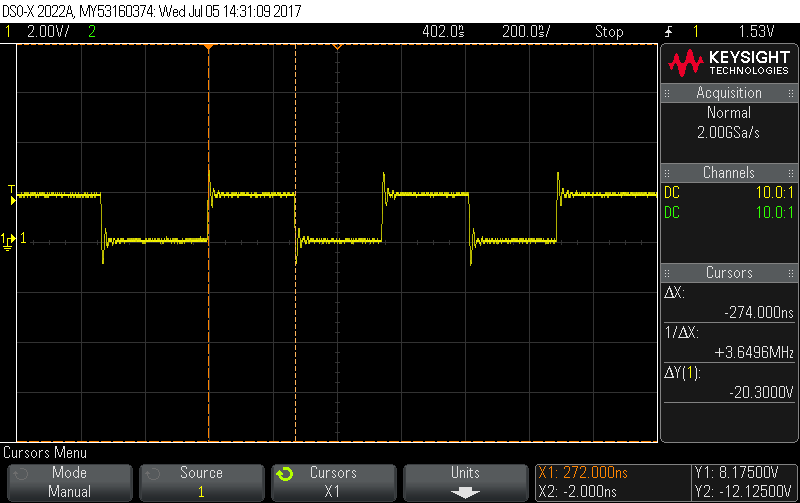

We are using IMX6Quad processor where we set and clear a gpio 3,21 with assembly code in u-boot given below

static iomux_v3_cfg_t const gpio_toggle_pads[] = {

MX6_PAD_EIM_D21__GPIO3_IO21 | MUX_PAD_CTRL(NO_PAD_CTRL),

};

static void gpio_toggle(void)

{

imx_iomux_v3_setup_multiple_pads(gpio_toggle_pads, ARRAY_SIZE(gpio_toggle_pads));

gpio_direction_output(IMX_GPIO_NR(3, 21),0);

asm(" ldr r0,=0x20A4000");

asm(" ldr r1,=(1<<21)");

asm(" ldr r2,=(0<<21)");

asm(" str r1,[r0]");

asm(" str r2,[r0]");

asm(" str r1,[r0]");

asm(" str r2,[r0]");

asm(" str r1,[r0]");

}

where for the first low to high is 300ns , and others either low to high or high to low its around 270ns.

1.why this much delay(270ns) between setting and clearing of gpio in imx6 processors ?

2.please provide us solutions to reduce it if possible ?

thanks,

uday

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi uday

some customers achieved working with GPIO on SDK :

the trick was to enable MMU, the L2 cache, and set the mmu entry that cover the

GPIO_DR address of Device type (which set the bufferable attribute)

+ mmu_enable();

+ // Enable L2 Cache

+ _l2c310_cache_setup();

+ _l2c310_cache_invalidate();

+ _l2c310_cache_enable();

- mmu_map_l1_range(0x00a00000, 0x00a00000, 0x0f600000, kStronglyOrdered,kShareable, kRWAccess); // More peripherals

+ mmu_map_l1_range(0x00a00000, 0x00a00000, 0x0f600000, kDevice, kShareable, kRWAccess); // More peripherals

The above is the entry for mapping a chunk of 0x0f600000 bytes of physical memory

(0x000A00000 - 0x10000000) to its virtual address 0x000A00000

This is a 1 to 1 mapping. As one can see all the GPIO registers (0x0209C000 - 0x020B401C) fall in these area.

The only difference between the the KStronglyOrdered and the KDevice type is that the later

enable the bufferable option in its entry descriptor.

case kStronglyOrdered:

entry.c = 0;

entry.b = 0;

entry.tex = 0;

entry.s = 1; // Ignored

break;

case kDevice:

if (isShareable)

{

entry.c = 0;

entry.b = 1;

entry.tex = 0;

entry.s = 1; // Ignored

}

If one already have the L2 cache enabled and the MMU, try to find the entry that

correspond to the area where the GPIO registers are mapped and set the bufferable

field for that particuat entry.

In linux some customers succeded to decrease time to 92 ns (184 ns period to toggle IO)

using direct register acces in a kernel module.

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi igor

can you give me the linux SDK version and link for imx6Quad processors to work on ?

thanks

uday

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告