- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- I.MX7D LPDDR3 measurement issue

I.MX7D LPDDR3 measurement issue

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

I.MX7D LPDDR3 measurement issue

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi support,

We tried to measure the DRAM timing with 12GHz differential probe. It seems we have the similar problem on the measurement like the problem as below link. But in our schematic, the JTAG_MOD has been pulled down.

Our problem is that when we connect the DQS0 to the scope, the boot will hand up or can not boot, but connect the clock and DQ only without DQS connection can be ok to run the test. Once we connect the DQS, the boot will be fail. I have run the memtool and the stress test can be more than 620MHz, I think the timing tolerance should be enough. Do you have any idea for it?

I want to upload my schematic for you, can anyone see it here? I want to keep it confidential.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

You mentioned, that the DDR Stress test is working.

Are the same DDR initialization parameters used for the Stress testmemory init script and for system boot ?

Please look at Chapter 1 (Porting U-Boot from an i.MX 6/7 Reference Board to an i.MX 6/7 Custom Board) of “i.MX_BSP_Porting_Guide.pdf”

Have a great day,

Yuri

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I mean when I perform the DDR timing test in scope to measure the timing, it will cause boot fail or hand up. The parameter we used can support the stress test up to 6xxMHz, the tolerance should be enough.

I have checked the waveform of the DQS, the write waveform for DQS is good but we found the read waveform is very ugly. The Read DQS comes from the LPDDR3 and the measured point is on the carrier of the LPDDR3. Do you have any idea for it? I know the LPDDR3 on IMX7 does not support the ODT. Or we need to measure the read DQS on the CPU (receiver) side?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

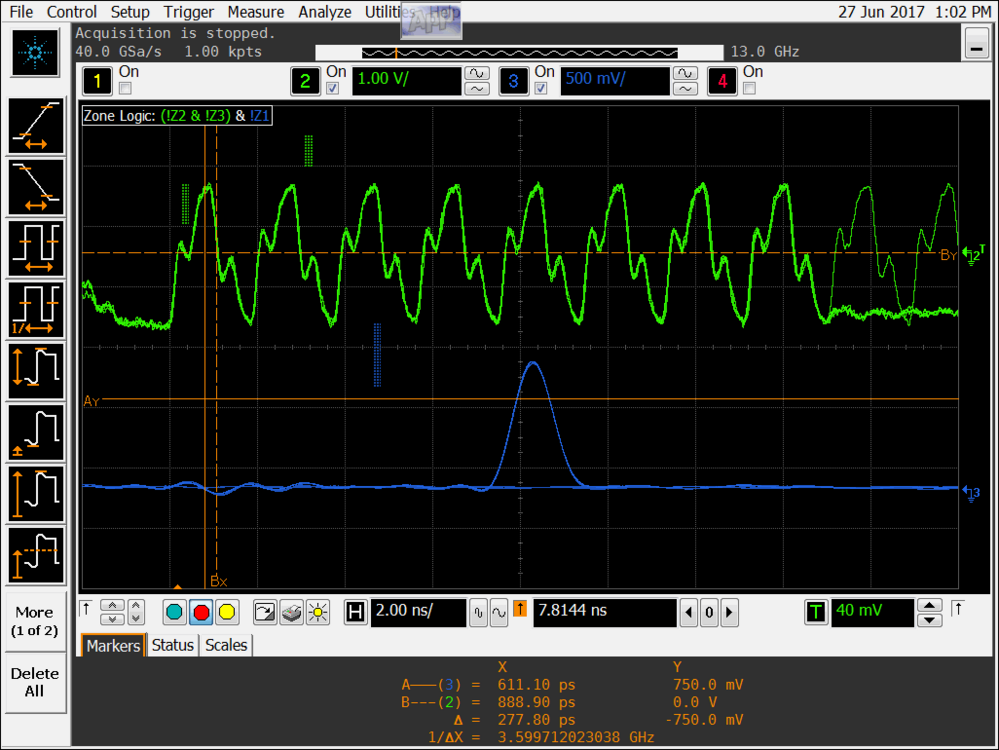

The read waveform is as below, the DQS is output from LPDDR3 and measure on the LPDDR3 carrier test package.

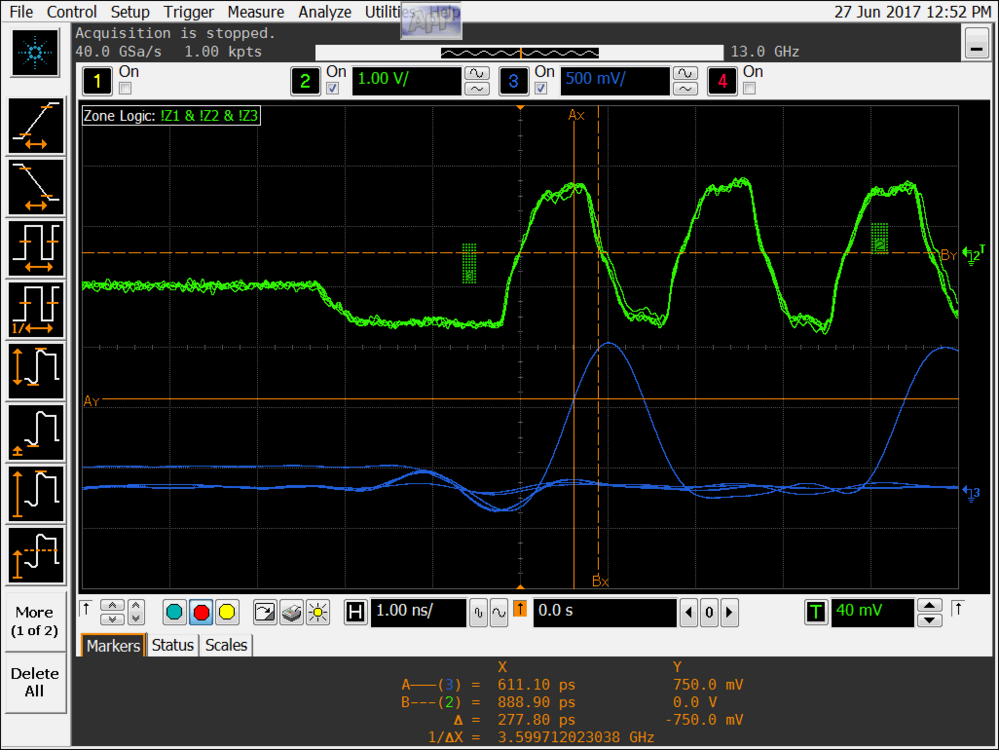

The below is the write and output from IMX7D, the measure on the LPDDR3 carrier test package.

Since the write waveform is good, so I think the PCB impedance should be ok but we get the bad output from the LPDDR3. From your experience, what can we try from the PHY setting?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

You may try to configure DDR drive strength.

Regards,

Yuri.