- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- Product Forums

- :

- MPC5xxx

- :

- Re: MPC5777C EBI chip select generation

MPC5777C EBI chip select generation

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I configured EBI with the following setting but CS is not generating

1.PLL0 --- 192MHZ,PLL1-- 264MHZ

2.SYSCLKSEL -- PLL1,plat_clk = 132MHZ

3.clkout=66MHZ,engclk= 132/32

4.EBI configuration for 16 bit,non-multiplexed,CS access

EBI_MCR = 1;

EBI.BMCR.R = 0;

/*CS0 0x2000_0000–0x3FFF_FFFF*/

EBI.CAL[0].OR.R = 0;//(0xFFF00000);

EBI.CAL[0].OR.B.SCY = 0x0a;

EBI.CAL[0].BR.R = (0x20000000 | 0x1A2B);

SIU.PCR[256].R = 0x060F;//0x060F; CS0 config

SIU.PCR[294].R = 0x060F;//0x060F; RD_WR

SIU.PCR[277].R = 0x060F;//0x060F;

for (i=259;i<=277;i++)//address bus

{

PCR[i] = 0x0440;

}

for (i=278;i<=293;i++)//data bus

{

PCR[i] = 0x0440;

}

/*writing in external space in while*/

for(;;)

{

*(int *)(0x20000000) = 0x5555;

//delay

}

I am monitoring CS in oscilloscope,but it is not cumming. i am testing this on NXP EVB and project is created in S32DS.

please give some solution.

Thanks&Regards,

Naidu

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I am attaching test code I have written. It partially works on my side, but I have some preliminary version of MPC5777C-516DS where there is incorrectly routed D_ADD_DAT31 lines thus my simple test don't pass. But I can see in the debugger window it works, but data are slightly corrupted.

Please, let me know if it works on you side, hoping you have newer EVB. Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

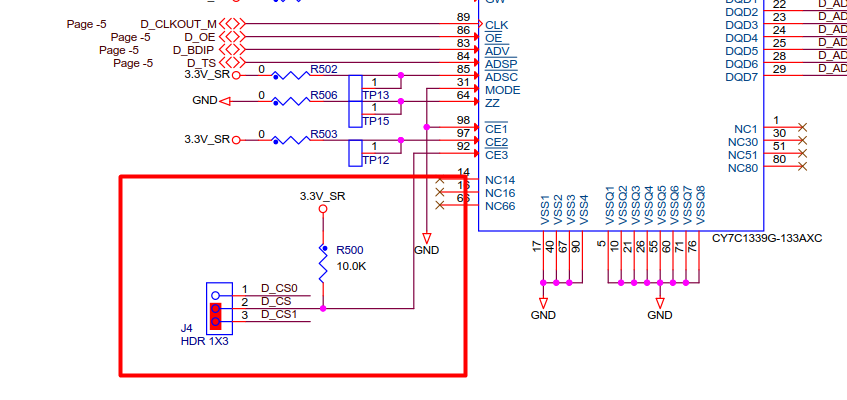

Hi, do you have configured following jumper?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi David,

I am checking pin 1 status in oscilloscope,it is not toggling,it is always high. Please see some more observations

1.TLB entry in startup code for MMU initialisation and AN5191 are not matching.(table numbers)

2.in startup code RPN of external memory is zero,i changed it to 0x2000 but still it is not working. in metroworks for MPC5567 project, in HW_init function,for external memory initialisation RPN and EPN are having same value.(0x2000)

3.In MPC5567 project with metroworks,external memory initialisation will happen only after the macro definition.here also we need to do any setting?

If you are having any facility to check this problem in your lab then i will share entire project. Otherwise share the EBI firmware already tested is available with you.

Thanking You.

Regards,

Naidu

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I will share example code, probably tomorrow.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You have incorrectly defined OR register that probably the reason why you don't see asserted chip-select.

See following document, section 5:

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I referred the section 5 of the document,OR value zero means entire memory space is selected,ia it correct? Anyway I checked with both OR values still it is not coming. Ok please share the software with CS access.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I am attaching test code I have written. It partially works on my side, but I have some preliminary version of MPC5777C-516DS where there is incorrectly routed D_ADD_DAT31 lines thus my simple test don't pass. But I can see in the debugger window it works, but data are slightly corrupted.

Please, let me know if it works on you side, hoping you have newer EVB. Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Following is the MMU initialization in my project(which is generated by IDE)

e_lis r3, 0x1001

mtspr 624, r3

e_lis r4, 0xC000

e_or2i r4, 0x0480

mtspr 625, r4

e_lis r5, 0x4000

e_or2i r5, 0x0028

mtspr 626, r5

e_lis r6, 0x4000

e_or2i r6, 0x003f

mtspr 627, r6

tlbwe

e_lis r3, 0x1000

mtspr 624, r3

e_lis r4, 0xC000

e_or2i r4, 0x0700

mtspr 625, r4

e_lis r5, 0x0000

e_or2i r5, 0x0020

mtspr 626, r5

e_lis r6,0x0000

e_or2i r6, 0x003f

mtspr 627, r6

tlbwe

e_lis r3, 0x1002

mtspr 624, r3

e_lis r4, 0xC000

e_or2i r4, 0x0580

mtspr 625, r4

e_lis r5, 0xFFE0

e_or2i r5, 0x002A

mtspr 626, r5

e_lis r6, 0xFFE0

e_or2i r6, 0x003f

mtspr 627, r6

tlbwe

e_lis r3, 0x1003

mtspr 624, r3

e_lis r4, 0xC000

e_or2i r4, 0x0700

mtspr 625, r4

e_lis r5, 0x2000

e_or2i r5, 0x0020

mtspr 626, r5

e_lis r6,0x0000

e_or2i r6, 0x003f

mtspr 627, r6

tlbwe

e_lis r3, 0x1004

mtspr 624, r3

e_lis r4, 0xC000

e_or2i r4, 0x0580

mtspr 625, r4

e_lis r5, 0xC3E0

e_or2i r5, 0x002A

mtspr 626, r5

e_lis r6, 0xC3E0

e_or2i r6, 0x003f

mtspr 627, r6

tlbwe

In the given SW in External_SRAM_MMU_init() function you are refering TLB 2?is it ok?in above startup code it is at TLB3.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yes, my startup uses TLB2 for external bus

#TLB2 = external bus @ 0x2000_0000, VLE

e_lis r3,0x1002

mtspr mas0,r3

e_lis r3,0xC000

e_or2i r3,0x0700

mtspr mas1,r3

e_lis r3,0x2000

e_or2i r3,0x0020

mtspr mas2,r3

e_lis r3,0x0000

e_or2i r3,0x003F

mtspr mas3,r3

tlbwe

Feel free to modify it according your setup - btw following configurator could be possibly helpful for you:

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thank you for quick support.

1.what is the IDE you are using?i am unable to open the SW shared by you?

i try to do the changes as per shared SW in S32DS,but it is not accepting assembly instructions in .c file.

2.if possible share the SW with S32DS IDE.

Thanks&Regards,

Naidu

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

It is based on GreenHills compiler. However all necessary setting regarding EBI is present in main.c file. It should not be difficult to port it into S32.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

i am unable to add External_SRAM_MMU_init() function in my IDE,it contains TLB entry modification in assembly language and my compiler is giving error.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi david,

Thank you for your support,i added assembly instructions for TLB modification.now chip select is generating.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Can you please guide me how to open it through S32DS