- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- Product Forums

- :

- MPC5xxx

- :

- Re: SDADC of MPC5775K

SDADC of MPC5775K

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

SDADC of MPC5775K

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I want to power up all SDADC's simultaneously,but the last channel has no data,the data of the other 7 channels are correct.Please tell me how to configure SDADC.

Thanks!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

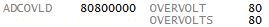

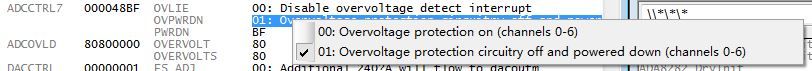

I met the same problem about SDADC. The value of 0~6 channels of SDADC is correct, but the value in last channel is almost 0. I checked the state of SDADC channel, it seems the Channel H is always keep in over voltage and over load status.

I try to disable over voltage protection via clear ADCCTRL7_OVPWRDN. But this switch bit seems only have effect to channel 0-6. Channel 7 still in over voltage status when I have closed the over voltage protection.

@Peter Vlna

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello

I am working on SDADC of MPC5775K too. I configured the register as reference manual recommended. But I can not see any data in SRAM using SDMA when the SDMA address was 0x40000000 and FRM__ACQ_DONE flag was set correctly. Could you give me some help or any example about SDADC with SDMA configuration.

Regards

Hai

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I am not so familiar with radar modules, but I will try to explain the situation.

You have acquired data via SDADC correctly. So you can see conversion is ended.

I expect that on end of conversion is DMA transfer triggered.

You have to correctly configure DMA to HW trigger request from SDADC.

I also expect that you must configure AIPS so the master (DMA) can access slaves.

If you done all this configuration correctly I see no other issues here and data transfer should work as required.

Peter

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Who can help me?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

The radar modules are supported only on request as the applications are very customer specific.

I do not expect that someone outside NXP will help you with this topic on community.

We have posted one simple example on SDADC here:

https://community.nxp.com/docs/DOC-330909

We will most probably create a set of some general examples for external use in future.

Peter

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I want to configure SDADC,too.But there is no example .You say that the data of the other 7 channels are correct.where is the data stored??what is the address?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You may try to configure SDMA to specify an address.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I've been able to sample data and read data from SDMA, but I have another problem.

We can set the number of sample(256,I set)in a chirp in the SPT module, and then we can set the number of chirp(128,I set) in a frame. This means that when SPT.GBL_STATUS.B.FRM_ACQ_DONE is set, we should adopt 256*128 data, but only the actual 128*208 data, if I increase the value of sample, the effective numerical maximum of only 208.

Have you ever had this problem?Or maybe the last channel didn't have all 0 data, but it was missing data like me.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

CTE triggers ADC sample capture.But I don't know how to configure CTE .Could you give me any example or your code?

regards

Junyi