- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- i.MAX6 Quad Processor Based Custom Hardware Design.

i.MAX6 Quad Processor Based Custom Hardware Design.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

i.MAX6 Quad Processor Based Custom Hardware Design.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear All,

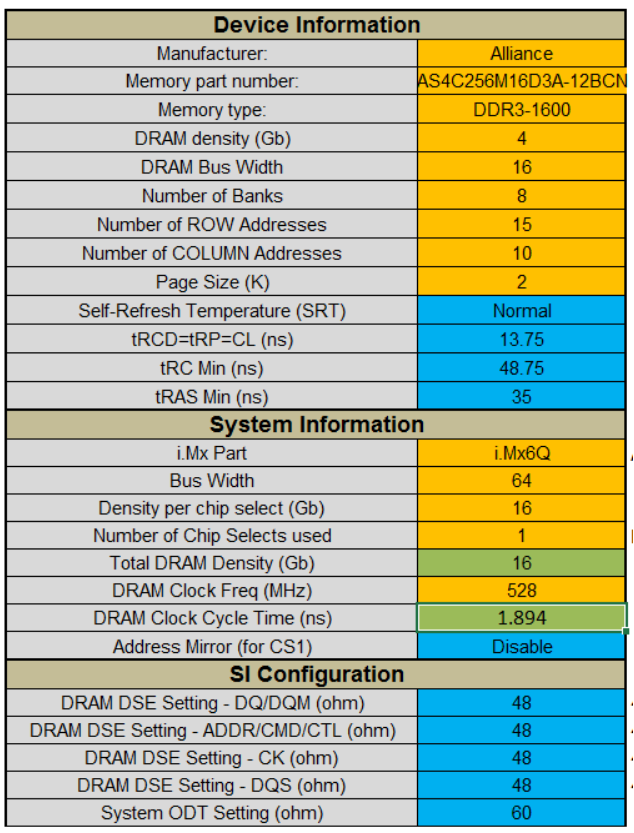

I have developed i.MAX6 processor based custom hardware design and for that I have used Alliance AS4C256M16D3A-12BCN RAM (Data Sheet for RAM ) I could flash the Boot ROM of the processor from uboot by using USB OTG interface and now I'm stuck at DDR MEMORY CALIBRATION.

1. In order to bringing up a custom hardware I think first we should do the DDR memory calibration and include the read and write level calibrations to uboot. Is this correct ? Do we have any thing to do before this ?

2. So when I'm running the DDR calibration using ddr_stress_tester_v2.60 software it shows "ERROR FOUND, we can't get suitable value !!!! dram test fails for all values.. "

============================================

DDR Stress Test (2.6.0)

Build: Nov 18 2016, 23:40:32

NXP Semiconductors.

============================================

============================================

Chip ID

CHIP ID = i.MX6 Dual/Quad (0x63)

Internal Revision = TO1.2

============================================

============================================

Boot Configuration

SRC_SBMR1(0x020d8004) = 0x00000000

SRC_SBMR2(0x020d801c) = 0x21000001

============================================

ARM Clock set to 1GHz

============================================

DDR configuration

BOOT_CFG3[5-4]: 0x00, Single DDR channel.

DDR type is DDR3

Data width: 64, bank num: 8

Row size: 15, col size: 10

Chip select CSD0 is used

Density per chip select: 2048MB

============================================

Current Temperature: 51

============================================

DDR Freq: 528 MHz

ddr_mr1=0x00000000

Start write leveling calibration...

running Write level HW calibration

Write leveling calibration completed, update the following registers in your initialization script

MMDC_MPWLDECTRL0 ch0 (0x021b080c) = 0x001F001F

MMDC_MPWLDECTRL1 ch0 (0x021b0810) = 0x001F001F

MMDC_MPWLDECTRL0 ch1 (0x021b480c) = 0x001F001F

MMDC_MPWLDECTRL1 ch1 (0x021b4810) = 0x001F001F

Write DQS delay result:

Write DQS0 delay: 31/256 CK

Write DQS1 delay: 31/256 CK

Write DQS2 delay: 31/256 CK

Write DQS3 delay: 31/256 CK

Write DQS4 delay: 31/256 CK

Write DQS5 delay: 31/256 CK

Write DQS6 delay: 31/256 CK

Write DQS7 delay: 31/256 CK

Starting DQS gating calibration

. HC_DEL=0x00000000 result[00]=0x11111111

. HC_DEL=0x00000001 result[01]=0x11111111

. HC_DEL=0x00000002 result[02]=0x11111111

. HC_DEL=0x00000003 result[03]=0x11111111

. HC_DEL=0x00000004 result[04]=0x11111111

. HC_DEL=0x00000005 result[05]=0x11111111

. HC_DEL=0x00000006 result[06]=0x11111111

. HC_DEL=0x00000007 result[07]=0x11111111

. HC_DEL=0x00000008 result[08]=0x11111111

. HC_DEL=0x00000009 result[09]=0x11111111

. HC_DEL=0x0000000A result[0A]=0x11111111

. HC_DEL=0x0000000B result[0B]=0x11111111

. HC_DEL=0x0000000C result[0C]=0x11111111

. HC_DEL=0x0000000D result[0D]=0x11111111

ERROR FOUND, we can't get suitable value !!!!

dram test fails for all values.

So it may be bad PCB layout or incorrect Script. But I did the script editing according to the RAM Data sheet. This is the changed excel sheet. Can you find any mistake in this according to the given RAM DATA SHEET ? If the problem is with the BAD PCB layout how I can confirm it whether BAD PCB or incorrect script ?

#Oliver Chen#igorpadykov#Wang Lin,

I must be thankful to you all if you can help me on this matter.

Regards,

Peter.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Please look at hints below regarding the issue.

You may try to decrease memory frequency till 400 MHz.

Perhaps the problem relates to some inaccuracy in memory PCB design.

You may use sections 3.3.1 (Identifying Issue on Calibrations) and 3.3.2 (Identifying

Issue on Stress Test) of the following document.

Freescale i.MX6 DRAM Port Application Guide-DDR3

Please check Your PCB design using Chapter 3 (i.MX 6 Series Layout Recommendations)

of the Hardware Development Guide. In particular, please use Excel page named “MX6 DRAM

Bus Length Check” in “HW Design Checking List for i.Mx6”.

HW_Design_Checking_List_for_i.MX6DQP6DQ6SDL

Have a great day,

Yuri

------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer

button. Thank you!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear #Yuri Muhin

Many thanks for your reply. Do you have any idea of getting the same value for "Write leveling calibration" as follows.

MMDC_MPWLDECTRL0 ch0 (0x021b080c) = 0x001F001F

MMDC_MPWLDECTRL1 ch0 (0x021b0810) = 0x001F001F

MMDC_MPWLDECTRL0 ch1 (0x021b480c) = 0x001F001F

MMDC_MPWLDECTRL1 ch1 (0x021b4810) = 0x001F001F

From where this value 0x001F001F came from ? If the test stuck in this point does that means even the processor couldn't access or write to the RAMs ?

Regards,

Peter.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

"Whether or not the DRAM interface is working at all, the Write Leveling test will always complete.

The returned values may not be valid, and usually if the returned values are 0x001F001F - at least, with the

stress test version V1.03 - the test numbers are not valid."

Regards,

Yuri.