- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- MQX Software Solutions

- :

- MQX Software Solutions

- :

- Re: K70 150, increase clock from 120MHz to 150MHz

K70 150, increase clock from 120MHz to 150MHz

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello

U used a K70 120m with tower K70 system and MQX 4.1.

I migrate to a home board with a K70150m, then I would modify MQX to increase CPU clock from 120MHz to 150MHz.

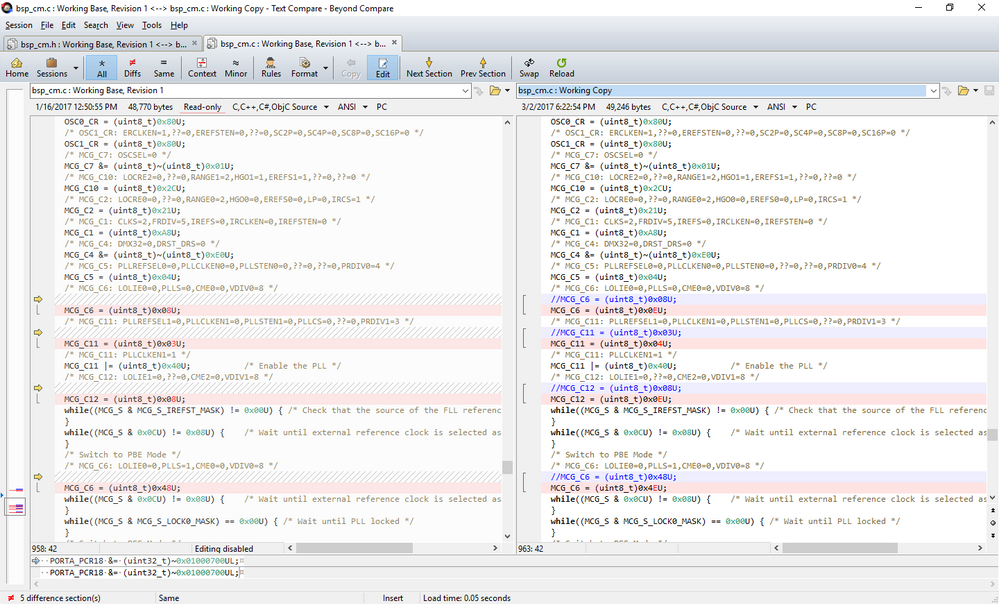

I made following modifications (See Tag "//debug AG Clock"):

static void Cpu_SetMCGModePEE(uint8_t CLKMode) { switch (CLKMode) { case 0U: /* Switch to PEE Mode */ /* OSC0_CR: ERCLKEN=1,??=0,EREFSTEN=0,??=0,SC2P=0,SC4P=0,SC8P=0,SC16P=0 */ OSC0_CR = (uint8_t)0x80U; /* MCG_C10: LOCRE2=0,??=0,RANGE1=2,HGO1=1,EREFS1=1,??=0,??=0 */ MCG_C10 = (uint8_t)0x2CU; /* OSC1_CR: ERCLKEN=1,??=0,EREFSTEN=0,??=0,SC2P=0,SC4P=0,SC8P=0,SC16P=0 */ OSC1_CR = (uint8_t)0x80U; /* MCG_C1: CLKS=0,FRDIV=5,IREFS=0,IRCLKEN=0,IREFSTEN=0 */ MCG_C1 = (uint8_t)0x28U; /* MCG_C2: LOCRE0=0,??=0,RANGE0=2,HGO0=0,EREFS0=0,LP=0,IRCS=1 */ MCG_C2 = (uint8_t)0x21U; /* MCG_C11: PLLREFSEL1=0,PLLCLKEN1=0,PLLSTEN1=0,PLLCS=0,??=0,PRDIV1=3 */ MCG_C11 = (uint8_t)0x03U; /* MCG_C11: PLLCLKEN1=1 */ MCG_C11 |= (uint8_t)0x40U; /* Enable the PLL */ /* MCG_C12: LOLIE1=0,??=0,CME2=0,VDIV1=8 */ MCG_C12 = (uint8_t)0x08U; /* MCG_C5: PLLREFSEL0=0,PLLCLKEN0=0,PLLSTEN0=0,??=0,??=0,PRDIV0=4 */ MCG_C5 = (uint8_t)0x04U; /* MCG_C6: LOLIE0=0,PLLS=1,CME0=0,VDIV0=8 */ //Debug AG Clock MCG_C6 = (uint8_t)0x48U; MCG_C6 = (uint8_t)0x4EU; while((MCG_S & 0x0CU) != 0x0CU) { /* Wait until output of the PLL is selected */ } break; default: break; } }

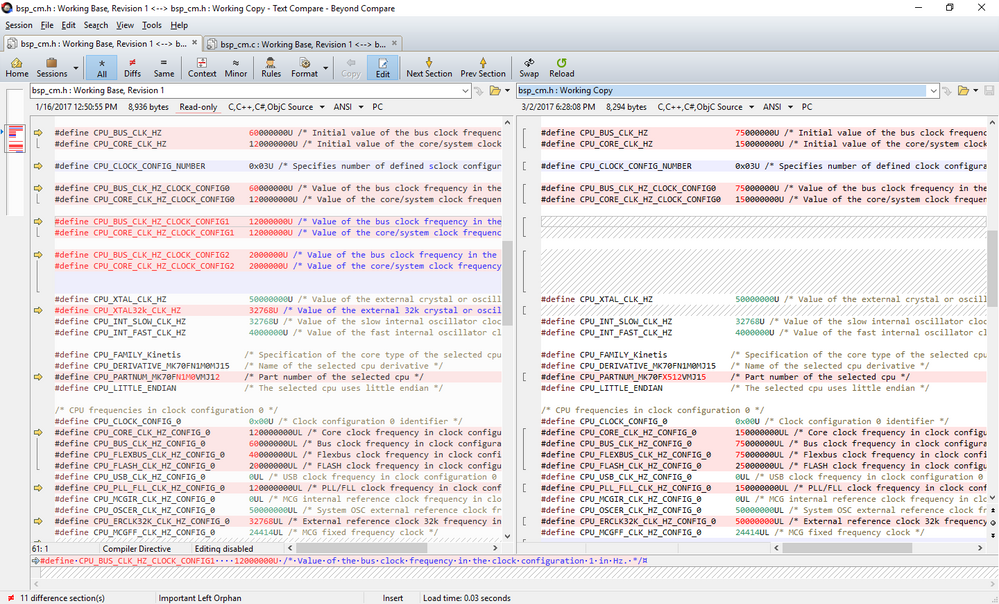

And then

//debug AG Clock #define CPU_BUS_CLK_HZ 60000000U /* Initial value of the bus clock frequency in Hz */ //debug AG Clock #define CPU_CORE_CLK_HZ 120000000U /* Initial value of the core/system clock frequency in Hz. */ #define CPU_BUS_CLK_HZ 75000000U /* Initial value of the bus clock frequency in Hz */ #define CPU_CORE_CLK_HZ 150000000U /* Initial value of the core/system clock frequency in Hz. */ #define CPU_CLOCK_CONFIG_NUMBER 0x03U /* Specifies number of defined sclock configurations. */ //debug AG Clock #define CPU_BUS_CLK_HZ_CLOCK_CONFIG0 60000000U /* Value of the bus clock frequency in the clock configuration 0 in Hz. */ //debug AG Clock #define CPU_CORE_CLK_HZ_CLOCK_CONFIG0 120000000U /* Value of the core/system clock frequency in the clock configuration 0 in Hz. */ #define CPU_BUS_CLK_HZ_CLOCK_CONFIG0 75000000U /* Value of the bus clock frequency in the clock configuration 0 in Hz. */ #define CPU_CORE_CLK_HZ_CLOCK_CONFIG0 150000000U /* Value of the core/system clock frequency in the clock configuration 0 in Hz. */

/* CPU frequencies in clock configuration 0 */ //debug AG Clock #define CPU_CLOCK_CONFIG_0 0x00U /* Clock configuration 0 identifier */ //debug AG Clock #define CPU_CORE_CLK_HZ_CONFIG_0 120000000UL /* Core clock frequency in clock configuration 0 */ //debug AG Clock #define CPU_BUS_CLK_HZ_CONFIG_0 60000000UL /* Bus clock frequency in clock configuration 0 */ //debug AG Clock #define CPU_FLEXBUS_CLK_HZ_CONFIG_0 40000000UL /* Flexbus clock frequency in clock configuration 0 */ //debug AG Clock #define CPU_FLASH_CLK_HZ_CONFIG_0 20000000UL /* FLASH clock frequency in clock configuration 0 */ //debug AG Clock #define CPU_USB_CLK_HZ_CONFIG_0 0UL /* USB clock frequency in clock configuration 0 */ //debug AG Clock #define CPU_PLL_FLL_CLK_HZ_CONFIG_0 120000000UL /* PLL/FLL clock frequency in clock configuration 0 */ //debug AG Clock #define CPU_MCGIR_CLK_HZ_CONFIG_0 0UL /* MCG internal reference clock frequency in clock configuration 0 */ //debug AG Clock #define CPU_OSCER_CLK_HZ_CONFIG_0 50000000UL /* System OSC external reference clock frequency in clock configuration 0 */ //debug AG Clock #define CPU_ERCLK32K_CLK_HZ_CONFIG_0 32768UL /* External reference clock 32k frequency in clock configuration 0 */ //debug AG Clock #define CPU_MCGFF_CLK_HZ_CONFIG_0 24414UL /* MCG fixed frequency clock */ #define CPU_CLOCK_CONFIG_0 0x00U /* Clock configuration 0 identifier */ #define CPU_CORE_CLK_HZ_CONFIG_0 150000000UL /* Core clock frequency in clock configuration 0 */ #define CPU_BUS_CLK_HZ_CONFIG_0 75000000UL /* Bus clock frequency in clock configuration 0 */ #define CPU_FLEXBUS_CLK_HZ_CONFIG_0 50000000UL /* Flexbus clock frequency in clock configuration 0 */ #define CPU_FLASH_CLK_HZ_CONFIG_0 25000000UL /* FLASH clock frequency in clock configuration 0 */ #define CPU_USB_CLK_HZ_CONFIG_0 0UL /* USB clock frequency in clock configuration 0 */ #define CPU_PLL_FLL_CLK_HZ_CONFIG_0 150000000UL /* PLL/FLL clock frequency in clock configuration 0 */ #define CPU_MCGIR_CLK_HZ_CONFIG_0 0UL /* MCG internal reference clock frequency in clock configuration 0 */ #define CPU_OSCER_CLK_HZ_CONFIG_0 50000000UL /* System OSC external reference clock frequency in clock configuration 0 */ #define CPU_ERCLK32K_CLK_HZ_CONFIG_0 32768UL /* External reference clock 32k frequency in clock configuration 0 */ #define CPU_MCGFF_CLK_HZ_CONFIG_0 24414UL /* MCG fixed frequency clock */

But after try, CPU clock is always 120MHz. (LCDC clock with a div 4 is always at 30MHz...)

what I have forget to upgrade clock frequency?

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Arno Gir,

Please check the attached document, this document shows how to change default clock settings in Kinetis BSPs.

I hope this helps!!

Have a great day,

Sol

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Bellow are the modifications done:

In user_config.h, add:

#define BSPCFG_CPU_CORE_CLK_HZ 120000000U /* Set to 120000000U or 150000000U */

in bsp_cm.c, Repalce All following line

/* MCG_C11: PLLREFSEL1=0,PLLCLKEN1=0,PLLSTEN1=0,PLLCS=0,??=0,PRDIV1=3 */

MCG_C11 = (uint8_t)0x03U;....

MCG_C5 = (uint8_t)0x04U;

by

#if (BSPCFG_CPU_CORE_CLK_HZ == 150000000)

/* MCG_C11: PLLREFSEL1=0,PLLCLKEN1=0,PLLSTEN1=0,PLLCS=1,??=0,PRDIV1=3 */

MCG_C11 = (uint8_t)0x13U;

#else /* (BSPCFG_CPU_CORE_CLK_HZ == 120000000) */

/* MCG_C11: PLLREFSEL1=0,PLLCLKEN1=0,PLLSTEN1=0,PLLCS=0,??=0,PRDIV1=3 */

MCG_C11 = (uint8_t)0x03U;

#endif....

#if (BSPCFG_CPU_CORE_CLK_HZ == 120000000)

MCG_C5 = (uint8_t)0x04U;

#else /* (BSPCFG_CPU_CORE_CLK_HZ == 150000000) */

MCG_C5 = (uint8_t)0x03U;

#endif

in bsp_cm.h replace

#define CPU_BUS_CLK_HZ 60000000U /* Initial value of the bus clock frequency in Hz */

#define CPU_CORE_CLK_HZ 120000000U /* Initial value of the core/system clock frequency in Hz. */#define CPU_CLOCK_CONFIG_NUMBER 0x03U /* Specifies number of defined sclock configurations. */

#define CPU_BUS_CLK_HZ_CLOCK_CONFIG0 60000000U /* Value of the bus clock frequency in the clock configuration 0 in Hz. */

#define CPU_CORE_CLK_HZ_CLOCK_CONFIG0 120000000U /* Value of the core/system clock frequency in the clock configuration 0 in Hz. */

by

#define CPU_BUS_CLK_HZ (BSPCFG_CPU_CORE_CLK_HZ / 2) /* Initial value of the bus clock frequency in Hz */

#define CPU_CORE_CLK_HZ (BSPCFG_CPU_CORE_CLK_HZ ) /* Initial value of the core/system clock frequency in Hz. */#define CPU_CLOCK_CONFIG_NUMBER 0x03U /* Specifies number of defined sclock configurations. */

/* CR #250 */

#define CPU_BUS_CLK_HZ_CLOCK_CONFIG0 (BSPCFG_CPU_CORE_CLK_HZ / 2) /* Value of the bus clock frequency in the clock configuration 0 in Hz. */

#define CPU_CORE_CLK_HZ_CLOCK_CONFIG0 (BSPCFG_CPU_CORE_CLK_HZ ) /* Value of the core/system clock frequency in the clock configuration 0 in Hz. */

And replace

/* CPU frequencies in clock configuration 0 */

#define CPU_CLOCK_CONFIG_0 0x00U /* Clock configuration 0 identifier */

#define CPU_CORE_CLK_HZ_CONFIG_0 120000000UL /* Core clock frequency in clock configuration 0 */

#define CPU_BUS_CLK_HZ_CONFIG_0 60000000UL /* Bus clock frequency in clock configuration 0 */

#define CPU_FLEXBUS_CLK_HZ_CONFIG_0 40000000UL /* Flexbus clock frequency in clock configuration 0 */

#define CPU_FLASH_CLK_HZ_CONFIG_0 20000000UL /* FLASH clock frequency in clock configuration 0 */

#define CPU_USB_CLK_HZ_CONFIG_0 0UL /* USB clock frequency in clock configuration 0 */

#define CPU_PLL_FLL_CLK_HZ_CONFIG_0 120000000UL /* PLL/FLL clock frequency in clock configuration 0 */

#define CPU_MCGIR_CLK_HZ_CONFIG_0 0UL /* MCG internal reference clock frequency in clock configuration 0 */

#define CPU_OSCER_CLK_HZ_CONFIG_0 50000000UL /* System OSC external reference clock frequency in clock configuration 0 */

#define CPU_ERCLK32K_CLK_HZ_CONFIG_0 32768UL /* External reference clock 32k frequency in clock configuration 0 */

#define CPU_MCGFF_CLK_HZ_CONFIG_0 24414UL /* MCG fixed frequency clock */

by

#define CPU_CLOCK_CONFIG_0 0x00U /* Clock configuration 0 identifier */

#define CPU_CORE_CLK_HZ_CONFIG_0 (BSPCFG_CPU_CORE_CLK_HZ ) /* Core clock frequency in clock configuration 0 */

#define CPU_BUS_CLK_HZ_CONFIG_0 (BSPCFG_CPU_CORE_CLK_HZ /2) /* Bus clock frequency in clock configuration 0 */

#define CPU_FLEXBUS_CLK_HZ_CONFIG_0 (BSPCFG_CPU_CORE_CLK_HZ /3) /* Flexbus clock frequency in clock configuration 0 */

#define CPU_FLASH_CLK_HZ_CONFIG_0 (BSPCFG_CPU_CORE_CLK_HZ /6) /* FLASH clock frequency in clock configuration 0 */

#define CPU_USB_CLK_HZ_CONFIG_0 0UL /* USB clock frequency in clock configuration 0 */

#define CPU_PLL_FLL_CLK_HZ_CONFIG_0 (BSPCFG_CPU_CORE_CLK_HZ ) /* PLL/FLL clock frequency in clock configuration 0 */

#define CPU_MCGIR_CLK_HZ_CONFIG_0 0UL /* MCG internal reference clock frequency in clock configuration 0 */

#define CPU_OSCER_CLK_HZ_CONFIG_0 50000000UL /* System OSC external reference clock frequency in clock configuration 0 */

#define CPU_ERCLK32K_CLK_HZ_CONFIG_0 32768UL /* External reference clock 32k frequency in clock configuration 0 */

#define CPU_MCGFF_CLK_HZ_CONFIG_0 24414UL /* MCG fixed frequency clock */

Exemple to make work USB, we need to stay on 120MHz because at 150MHz we can't respect the maximum USB frequency.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Arno Gir,

Please check the attached document, this document shows how to change default clock settings in Kinetis BSPs.

I hope this helps!!

Have a great day,

Sol

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank,

All work now.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

can you please post your final source code that worked, I am struggling to do the same. I have MQX 4.2 with IAR (NO CW).

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I did the following changes to bsp_cm.h:

And bsp_cm.c:

But now, FlexCAN module does not work at all, also I2C baud is having a problem, with 120MHz clock, I sed to set it to 400KHz, with 150MHz system and 75MHz bus clock, I can only set I2C baud to 390KHz.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

arnogir, can you please post your final source code that worked, I am struggling to do the same. I have MQX 4.2 with IAR (NO CW).

Thanks