- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- Product Forums

- :

- Sensors

- :

- Re: MMA8451Q accessing FIFO and xyz samples concurrently

MMA8451Q accessing FIFO and xyz samples concurrently

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

MMA8451Q accessing FIFO and xyz samples concurrently

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

My question has two parts:

1. We have ODR set to 400 Hz. We have configured the FIFO to trigger (FMODE = 11) on pulse event with watermark in the middle of the 32-sample FIFO buffer. I think this implies that the 80 msec wide buffer has 40 msec from the pulse event (and watermark) to the time when the FIFO buffer is full and the interrupt is triggered. Is that correct, i.e., in FMODE = 11 is the interrupt generated not at the watermark but rather 40 msec later when the buffer is full?

2. For separate purpose, running concurrently, our firmware polls the most recent xyz-data sample at 50 Hz or every 20 msec (by reading the usual xyz-data register 0x01, not the FIFO buffer). When we have this code in place, and we read the FIFO buffer following the pulse interrupt, we see FIFO values of -8160 filling one or more samples at the end of the FIFO, and the data spike that generated the pulse event is shifted that number of samples from the watermark. Is it possible that reading 0x01 is corrupting the FIFO? Is there a way to configure and use the accelerometer so we can get both FIFO for each pulse event and also poll ordinary data stream from 0x01 concurrently?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Thomas,

Thank you for writing.

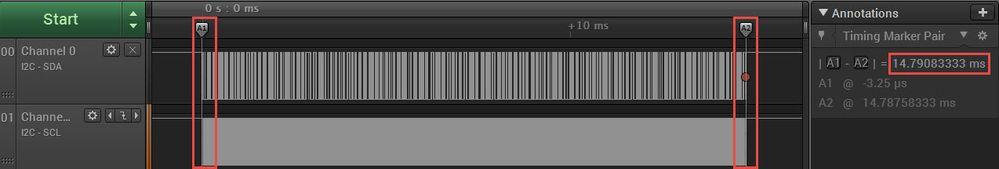

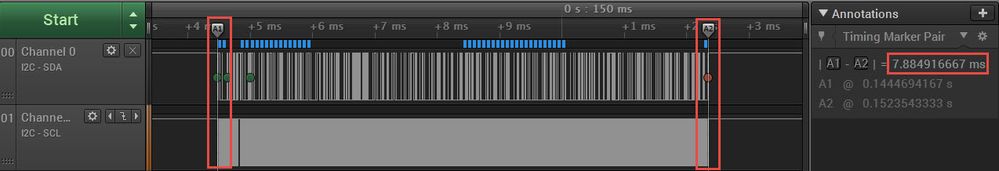

In this case, I created a sample project in which the MMA8451Q is set as follow: ODR=400Hz, FIFO Full Buffer Mode, interrupt enabled, I2C baud rate = 125KHz. You may refer to the images below in order to get a better understanding of the watermark:

1)

2)

The first image shows the time that passed, about 15ms, in order to fill the FIFO buffer using a watermark of 32. The second image shows the time that passed, about 7.8ms, with a watermark of 16. In both cases, an interrupt is generated (overflow).

So we can conclude that, indeed, your assumption is correct.

Please let me know if I misunderstood your question.

Regards,

David

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi David,

Thanks very much for your reply. I really appreciated your taking time to set up and run that experiment. I think that answered part 1 of my question. Do you have any thoughts on part 2? Does the -8160 value look familiar to you? Is there a way to configure and use the accelerometer so we can get both FIFO for each pulse event and also poll ordinary data stream from 0x01 concurrently?

Thanks again!

Tom.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Thomas,

In regard with the second question, please note that the sample data output registers (0x01 to 0x06), store the current sample data if the FIFO data output register driver is disabled, but if the FIFO data output register driver is enabled (F_MODE > 00) the sample data output registers point to the head of the FIFO buffer (register 0x01 X_MSB) which contains the previous 32 X, Y, and Z-data samples.

So the Register 0x01 points to the FIFO buffer and is used to access 8-bit or 14-bit data. You may want to wait until the FIFO buffer is full in order to read the data.

Please let me know if my answer is clear. I am glad to help.

Regards,

David