- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Re: Big gap between SDMA writes on EIM bus on 6sl/Linux 4.1

Big gap between SDMA writes on EIM bus on 6sl/Linux 4.1

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Big gap between SDMA writes on EIM bus on 6sl/Linux 4.1

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

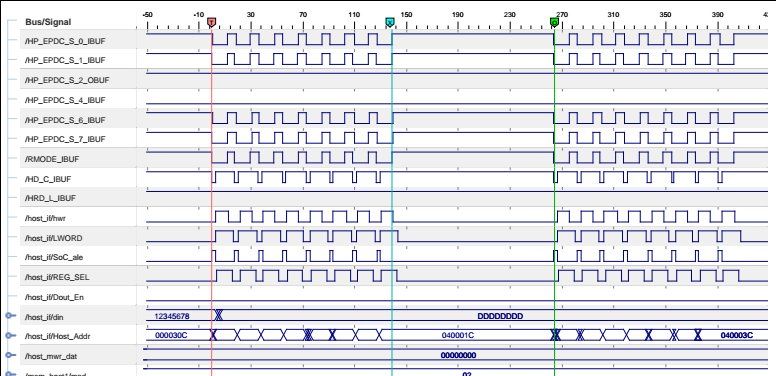

We're using a 6sl based board with Linux 4.1. We have 32-bit EIM transactions working using individual memory read/writes. We also have SDMA from host memory to EIM target (an FPGA) partially working but we're seeing unexpected large gaps within the SDMA transfers. For example, if we transfer 64 bytes in 32-bit mode, with 66MHz EIM clock, instead of seeing 16 consecutive transfers, we see the transfer split into 1 batch of 8 writes and then a pause of about 625ns and only then the 2nd batch of remaining 8 writes.

I've attached a scope screenshot.

I've tried changing various parameters within the EIM_GCR/CS1WCRx/etc registers. Tried tweaking burst length BL, write continuous, WC and others but the gap between the 2 sequences remains the same. That leaves the 2 suspect areas as being the SDMA test driver, or the SDMA AP2AP script which is in the sdma binary in 4.1.

My current EIM settings:

0x021B8018: 00930089 00001100 0F010000 00000000

0x021B8028: 01040400 00000000

My test dmaengine setup is:

dma_cap_zero(dma_m2m_mask);

dma_cap_set(DMA_SLAVE, dma_m2m_mask);

m2m_dma_data.dma_request = 0;

m2m_dma_data.dma_request2 = 0;

m2m_dma_data.peripheral_type = IMX_DMATYPE_MEMORY;

m2m_dma_data.priority = DMA_PRIO_HIGH;

dma_m2m_chan = dma_request_channel(dma_m2m_mask, dma_m2m_filter,

&m2m_dma_data);

dma_m2m_config.direction = DMA_MEM_TO_MEM;

dma_m2m_config.dst_addr_width = DMA_SLAVE_BUSWIDTH_4_BYTES;

dma_m2m_config.src_addr_width = DMA_SLAVE_BUSWIDTH_4_BYTES;

dma_m2m_config.src_maxburst = 64;

dma_m2m_config.dst_maxburst = 64;

dmaengine_slave_config(dma_m2m_chan, &dma_m2m_config);

dma_m2m_desc = dma_m2m_chan->device->device_prep_dma_memcpy(dma_m2m_chan, targetaddr, rbuf, 64, 0);

I've tried varying the burst size but it has no effect. I noticed some other postings on the forum which seem to suggest problems with EIM transfers, I'm wondering if there's an underlying problem. https://community.nxp.com/thread/329143

Also, does anyone know if there's a way to develop and add our own SDMA scripts to fix the bugs/problems with the existing FSL scripts? I tried asking FSL, and initially it seemed positive but now the request thread seems to be dead: Adding ap_2_ap_fixed into sdma rom

Thanks!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello jayakumar2,

as far as I remember, we have solved this trouble doing nothing ! Silicium Rev 1.3 of the i.MX6S (I don't know the SL behavior) corrects the issue seen on Rev 1.1 and Rev 1.2.

Please pay attention that internal architecture (for i.MX6S/D/Q) has not been prepared for such fast transfer, even if it seems obvious. People from NXP explained me that due to internal structure and pipes to go through, the time you observe is not abnormal, and they have even been surprised that correction appears in Rev 1.3.

So you should get in touch with very specialized NXP engineer if trouble is still present with the SL die.

Let us aware,

Poussemousse.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Please look at the following thread, especially to final message of

How to increase speed EIM consecutive acces on iMx6S

Regards,

Yuri.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jaya

please check

SDMA transfer between EIM and memory problem

Measure SDMA Memory To Memory Copy Performance on i.MX6Q

https://community.nxp.com/docs/DOC-106467

https://community.nxp.com/message/521500?commentID=521500#comment-521500

Custom sdma scripts can be developed using NXP Professional Services:

http://www.nxp.com/support/nxp-professional-services:PROFESSIONAL-SERVICE

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------