- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- Re: FB_TA signal behaviour in burst-inhibited mode

FB_TA signal behaviour in burst-inhibited mode

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

FB_TA signal behaviour in burst-inhibited mode

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello, I have a question about the flexbus in Kinetis K64 controller. I'm using the flexbus in burst-inhibited mode for a 8 bits bus size. If I execute the 16 bits access using the automatic acknowlege it works well, but if I use the FB_TA signal, the cycle is closed after read of first byte. A note: the second pulse of FB_ALE comes in any case but the second FB_CS0 pulse doesn't occurs. Have you some work around?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I suggest you use auto-acknowledge mode to terminate the memory accessing cycle by setting the AA bit with CSCR[AA] =

1.

If you clear the AA bit by CSCR[AA] =0, you have to drive the FB_TA signal with external circuit so that user can terminate memory accessing cycle by driving the FB_TA with external logic . You have to use a CPLD or simple FPGA to output signal to drive the FB_TA. In the case, you can use the FB_ALE or FB_CS falling edge to trigger a state machine and clear the FB_TA, after the predefined BUS_CLK, you can set the FB_TA so that the memory accessing cycle can be terminated.

Hope it can help you

BR

Xiangjun Rong

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks xiangjun.rong for you answer, but the K64 behavior isn't correct.

In my board the BUS_CLK signal isn't available between K64 and FPGA.

Inside FPGA I handle many DRams through a 16 bit communication device, so I use the FB_TA to close the cycle.

The access used is 16 bits burst-inhibited to 8-bit port, and the number of wait state is defined by FB_TA signal, but of course the wait states aren't the same at any access: it depends if at the other side of DPRam an access occurs at the same time.

The FB_TA assertion doesn't close the individual transfer, but it closes also the complete cycle (see 31.4.12.5 of K64 Sub-Family Reference Manual, Rev. 2, January 2014 picture page 778).

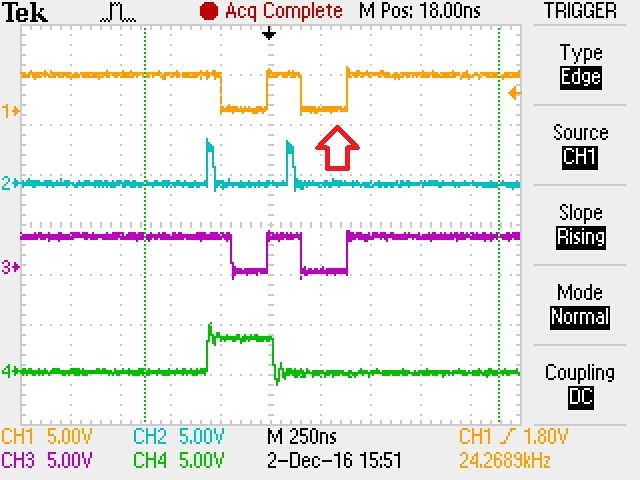

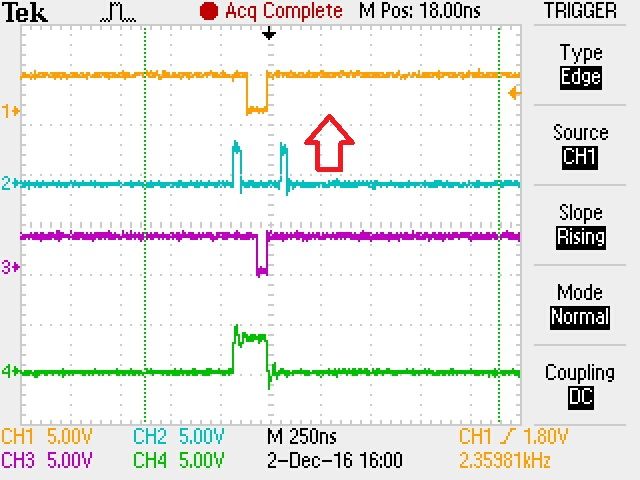

In attachment you can find pictures with the signals routed to test points by FPGA:

Legenda:

Channel 1 (orange): signal FB_CS0

Channel 2 (blue): signal FB_ALE

Channel 3 (purple): signal FB_TA

Channel 4 (green): signal FB_TSIZ1

Please see the two pictures without FB_TA connected and with FB_TA connected (AA=1).

Please note the presence of FB_ALE without FB_CS0 at the second transfer, when FB_TA is connected (second picture)

Thanks in advanced.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, Marco,

Do you use the FlexBus to access multiple DRAM or just SRAM, what is the function of FPGA? can you use multiple CSx to access the SRAM? If the K64 has enough CSx to access SRAM, you can use Auto-Acknowledge mode.

If you do use FB_TA to terminate the access, I still think you have to FB_CLK, because the rising edge of FB_CLK is used to sample the FB_TA signal, if your FPGA does not use FB_CLK, how do you synchronize the FB_TA with FB_CLK?

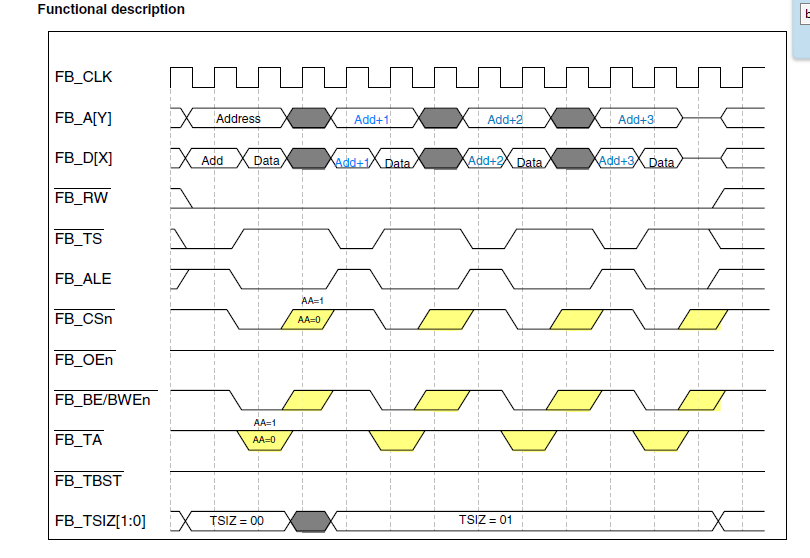

This is the timing of 32-bit-write burst-inhibited to 8-bit port described at 31.4.12.5.

BTW, the BSTR and BSTW bits should be cleared to disable burst mode.

Hope it can help you.

BR

XiangJun Rong

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi XiangJun Rong,

Thanks for your answer.

1) The FPGA uses flexbus to access to a controller and other glue logic. The controller interfaces also internal dual port sram. For this reason the FB_TA answer time isn't always the same.

2) Yes, I have multiple CSx in FPGA interface. The access to controller use FB_CS0, but in spare pins are available also FB_CS2, FB_CS4 and FB_CS5.

3) Yes, I know. It's possible to use Auto-Acknowledge mode, but the access becomes slow at all cycles. Using FB_TA the access is slow only when the bus at the other side of DPRAM executes an access at the same time.

4) No, the FB_CLK signal is not available in my FPGA. The FB_TA signal is sampled by K64. If the falling edge of FB_TA become at the same time of rising edge of FB_CLK, an additional wait state can be added. It isn't a problem.

i.e see item 4 at "2.1 Read cycle" of AN4393 Rev. 0, 05/2012.

Using the basic access, it works well without synchronize FB_TA with FB_CLK. It's normal for all bus async busses

5) Yes I disabled the burst mode clearing BSTR and BSTW flags.

Using only Auto-Acknowledge mode it's work well, but using FB_TA to close any single transfer it doesn't work.

Can you confirm this behaviour of K64?

It's strange because the FB_ALE signal is correctly asserted, but the FB_CS0 is not asserted (see pictures of last message).

Is it only a problem of FB_CS0 signal? Can I solve the problem substituting FB_CS0 with FB_CS2 (or FB_CS4 or FB_CS5)?

Thanks in advanced.

Marco

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

As a workaround, I recommend you use Auto-Acknowledge mode, you can connect CSx to each SRAM or memory-mapped devices, each CSx access timing can be set up independently,for each CSx has it's own FB_CSCRn.

Regarding your solution to terminate access with FB_TA, I think it is difficult to generte the FB_TA with FB_CLK involvement.

BR

Xiangjun Rong