- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- How to get mux 32bit work

How to get mux 32bit work

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

How to get mux 32bit work

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

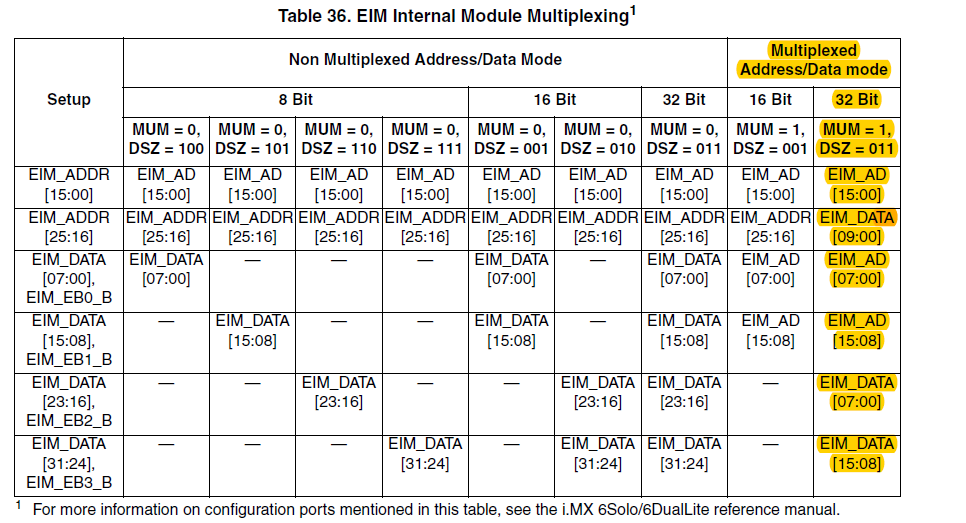

I am using i.mx6 solo processor connected to FPGA through EMI bus. I want to read and write 32bit data from the FPGA. I use Mux mode with DSZ=011( 26bit address:16bit AD+EIM data(0~9), 32bit data:16bit AD+EIM data(0~15),But CPU reset after writing 32 bit data to FPGA. does someone found this issues?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Yuri,

thanks for your comments,

our current configure as below:(It work at mux 16bit mode, but 32bit will reset at second write process), would you help check if something we missed? thanks

regval = val | 0x7<<28 | (0x3 << 16)| 0x4<<8 | 0x7<<3 | 0x3<<1 | 1<<2 | 1<<23;

writel( regval, WEIM_BASE_ADDR );

regval= 0x1;

writel(regval,WEIM_BASE_ADDR+0x4);

//write timimg

//WSC=6, ADVA=0, ADVN=1, ADH=1

regval = 0x6<<24 | 0x1<<18;

writel(regval, WEIM_BASE_ADDR + 0x10);

//WSC=7, RADVN=1, ADH=1, OEA=0

regval = 0x7<<24 | 0x1<<16;

writel(regval, WEIM_BASE_ADDR + 0x8);

iomux_v3_cfg_t eimfpga_da_pads[] = {

//EIM_AD[15:0]

MX6_PAD_EIM_DA0__WEIM_WEIM_DA_A_0 | MUX_PAD_CTRL(WEIM_NOR_PAD_CTRL),

MX6_PAD_EIM_DA1__WEIM_WEIM_DA_A_1 | MUX_PAD_CTRL(WEIM_NOR_PAD_CTRL),

MX6_PAD_EIM_DA2__WEIM_WEIM_DA_A_2 | MUX_PAD_CTRL(WEIM_NOR_PAD_CTRL),

MX6_PAD_EIM_DA3__WEIM_WEIM_DA_A_3 | MUX_PAD_CTRL(WEIM_NOR_PAD_CTRL),

MX6_PAD_EIM_DA4__WEIM_WEIM_DA_A_4 | MUX_PAD_CTRL(WEIM_NOR_PAD_CTRL),

MX6_PAD_EIM_DA5__WEIM_WEIM_DA_A_5 | MUX_PAD_CTRL(WEIM_NOR_PAD_CTRL),

MX6_PAD_EIM_DA7__WEIM_WEIM_DA_A_7 | MUX_PAD_CTRL(WEIM_NOR_PAD_CTRL),

MX6_PAD_EIM_DA8__WEIM_WEIM_DA_A_8 | MUX_PAD_CTRL(WEIM_NOR_PAD_CTRL),

MX6_PAD_EIM_DA9__WEIM_WEIM_DA_A_9 | MUX_PAD_CTRL(WEIM_NOR_PAD_CTRL),

MX6_PAD_EIM_DA10__WEIM_WEIM_DA_A_10 | MUX_PAD_CTRL(WEIM_NOR_PAD_CTRL),

MX6_PAD_EIM_DA11__WEIM_WEIM_DA_A_11 | MUX_PAD_CTRL(WEIM_NOR_PAD_CTRL),

MX6_PAD_EIM_DA12__WEIM_WEIM_DA_A_12 | MUX_PAD_CTRL(WEIM_NOR_PAD_CTRL),

MX6_PAD_EIM_DA13__WEIM_WEIM_DA_A_13 | MUX_PAD_CTRL(WEIM_NOR_PAD_CTRL),

MX6_PAD_EIM_DA14__WEIM_WEIM_DA_A_14 | MUX_PAD_CTRL(WEIM_NOR_PAD_CTRL),

MX6_PAD_EIM_DA15__WEIM_WEIM_DA_A_15 | MUX_PAD_CTRL(WEIM_NOR_PAD_CTRL),

//EIM_A_D[25:16]

MX6_PAD_CSI0_DATA_EN__WEIM_WEIM_D_0 | MUX_PAD_CTRL(WEIM_NOR_PAD_CTRL),

MX6_PAD_CSI0_VSYNC__WEIM_WEIM_D_1 | MUX_PAD_CTRL(WEIM_NOR_PAD_CTRL),

MX6_PAD_CSI0_DAT4__WEIM_WEIM_D_2 | MUX_PAD_CTRL(WEIM_NOR_PAD_CTRL),

MX6_PAD_CSI0_DAT5__WEIM_WEIM_D_3 | MUX_PAD_CTRL(WEIM_NOR_PAD_CTRL),

MX6_PAD_CSI0_DAT6__WEIM_WEIM_D_4 | MUX_PAD_CTRL(WEIM_NOR_PAD_CTRL),

MX6_PAD_CSI0_DAT7__WEIM_WEIM_D_5 | MUX_PAD_CTRL(WEIM_NOR_PAD_CTRL),

MX6_PAD_CSI0_DAT8__WEIM_WEIM_D_6 | MUX_PAD_CTRL(WEIM_NOR_PAD_CTRL),

MX6_PAD_CSI0_DAT9__WEIM_WEIM_D_7 | MUX_PAD_CTRL(WEIM_NOR_PAD_CTRL),

MX6_PAD_CSI0_DAT12__WEIM_WEIM_D_8 | MUX_PAD_CTRL(WEIM_NOR_PAD_CTRL),

MX6_PAD_CSI0_DAT13__WEIM_WEIM_D_9 | MUX_PAD_CTRL(WEIM_NOR_PAD_CTRL),

//EIM_DATA[31:26]

MX6_PAD_CSI0_DAT14__WEIM_WEIM_D_10 | MUX_PAD_CTRL(WEIM_NOR_PAD_CTRL),

MX6_PAD_CSI0_DAT15__WEIM_WEIM_D_11 | MUX_PAD_CTRL(WEIM_NOR_PAD_CTRL),

MX6_PAD_CSI0_DAT16__WEIM_WEIM_D_12 | MUX_PAD_CTRL(WEIM_NOR_PAD_CTRL),

MX6_PAD_CSI0_DAT17__WEIM_WEIM_D_13 | MUX_PAD_CTRL(WEIM_NOR_PAD_CTRL),

MX6_PAD_CSI0_DAT18__WEIM_WEIM_D_14 | MUX_PAD_CTRL(WEIM_NOR_PAD_CTRL),

MX6_PAD_CSI0_DAT19__WEIM_WEIM_D_15 | MUX_PAD_CTRL(WEIM_NOR_PAD_CTRL),

MX6_PAD_EIM_LBA__WEIM_WEIM_LBA | MUX_PAD_CTRL(WEIM_NOR_PAD_CTRL),

MX6_PAD_EIM_OE__WEIM_WEIM_OE | MUX_PAD_CTRL(WEIM_NOR_PAD_CTRL),

MX6_PAD_EIM_RW__WEIM_WEIM_RW | MUX_PAD_CTRL(WEIM_NOR_PAD_CTRL),

MX6_PAD_EIM_CS0__WEIM_WEIM_CS_0 | MUX_PAD_CTRL(WEIM_NOR_PAD_CTRL),

MX6_PAD_EIM_CS1__WEIM_WEIM_CS_1 | MUX_PAD_CTRL(WEIM_NOR_PAD_CTRL),

};

Br,

Jason

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Please check if EIM clock is not gated in CCM Clock Gating Register (CCM_CCGR6).

Also, section 22.6 (Initialization Information) of i.MX6 S/DL RM (IMX6SDLRM,

Rev. 2, 04/2015) contains examples of EIM initialization.

Have a great day,

Yuri

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------