- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- UnderVoltage shutdown fail

UnderVoltage shutdown fail

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

UnderVoltage shutdown fail

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Communities,

I have a custom board build on i.MX6D and PF0100F0A PMIC which powered by a 1-cell Li-po battery.

When the battery voltage is at ~3.1V open, the boot up sequence will make it drop to ~2V then stay at 2.7V.

From the datasheet, this should trigger the PMIC undervolt detect and put it into coincell mode.

But on our board, this fail to happen. The board just shutdown and bootup again and again until the battery protect circuit completely cut the power.

I have tried to pull the PWRON pin to 3V by external power supply, supply the VSNVS by external supply but nothing change.

I just want the undervoltage detection works, shut the system down and stay power off until the battery is about 3.1V which is datasheet stated rising threshold of UVDET and someone press the power button again.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Edmond

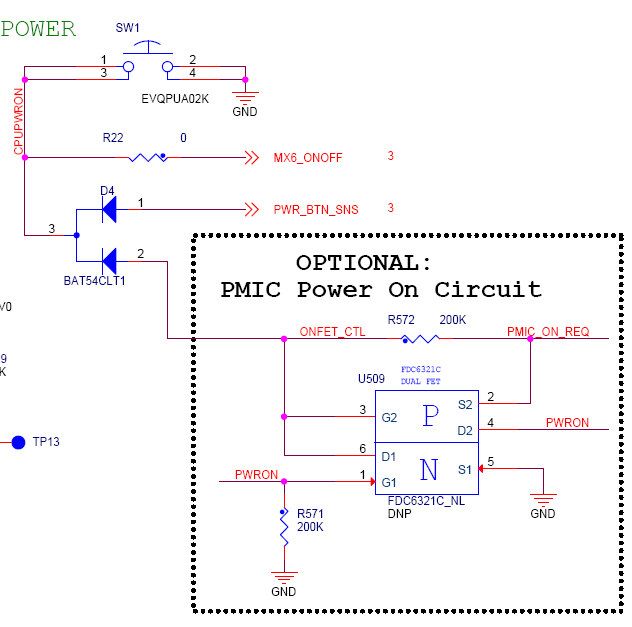

seems this is copy from sabre spf-27392 p.19 schematic

when processor powered off, voltage between G2-S2 is equal so

p-fet nonconductive and PWRON should be = 0, pulled down by R571.

On your circuit this is C398. When G2 goes to ground p-fet conducts

and PMIC_ON_REQ (high) goes to PWRON, turning on PMIC.

When PWRON=0 input voltage will not turn on PMIC with

configuration PWRON_CFG=0.

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi igor,

Thanks for your help.

Should I replace my C398 to 200k pull-down as sabre schematic?

I have tried this but no help.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I believe yes.

Seems it is necessary to attach permanent licell to VDD_SNVS_IN,

then check signals with oscillosope.

Best regards

igor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have tried your solution:

1. Apply 3VDC as licell to PMIC

2. Change the C398 to 200k pull down

But no help. Exactly same situation as before.

Is there anywhere you think it's suspicious?

Regards,

Edmond

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

so what is voltage between G2-S2 ?

~igor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for the reply.

measured as below.

Tried remove D17 pin 1, which isolate the un-initialize GPIO from CPU, but no help.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

you should try to find why G2=0, it should be the same

as S2. If removing D17 does not help, then you used wrong fet

or there are some layout errors, like short circuits.