- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- Product Forums

- :

- MPC5xxx

- :

- Re: MPC5775K SEMA42 multi cores

MPC5775K SEMA42 multi cores

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, Martin KovarPetr StancikStanislav Sliva

I'm trying to debug to SEMA42 module in the MPC5775K. I'd like to make one core to communicate with other. Is there some sample codes to share? Thanks.

Regards,

Ron

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Ron,

the general (simplified) principle of using semaphores is following:

You have two cores, one shared resource (for example memory) and one gate, which protects the shared resource. If any core wants to access to the shared resource, it has to check, of the gate is unlocked. If yes, core locks the gate and uses the shared resource (this is called critical section). After core leaves critical section (does not want to work shared resource anymore), core has to unlock the gate (because of deadlock) and any other core can use it now.

If the gate is locked, core has to wait, until other core unlock it. Gate can be unlock only by the the core which locked it.

And lets look at the example.

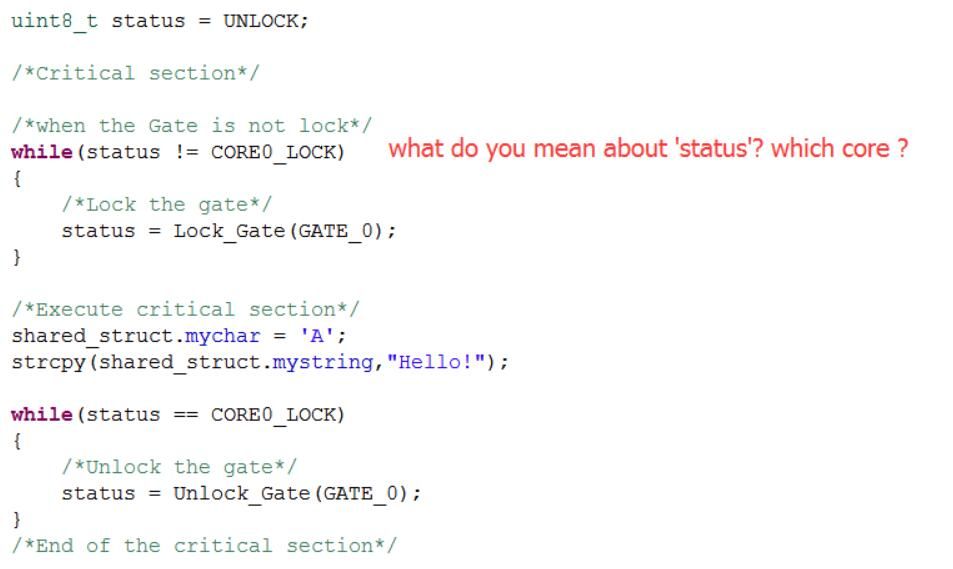

1)what do you mean about status? which core?

Status variable determines the status of the GATE (only gate 0 is used for both cores). If gate is unlock, core can lock it and execute it's critical section (access to shared resource).

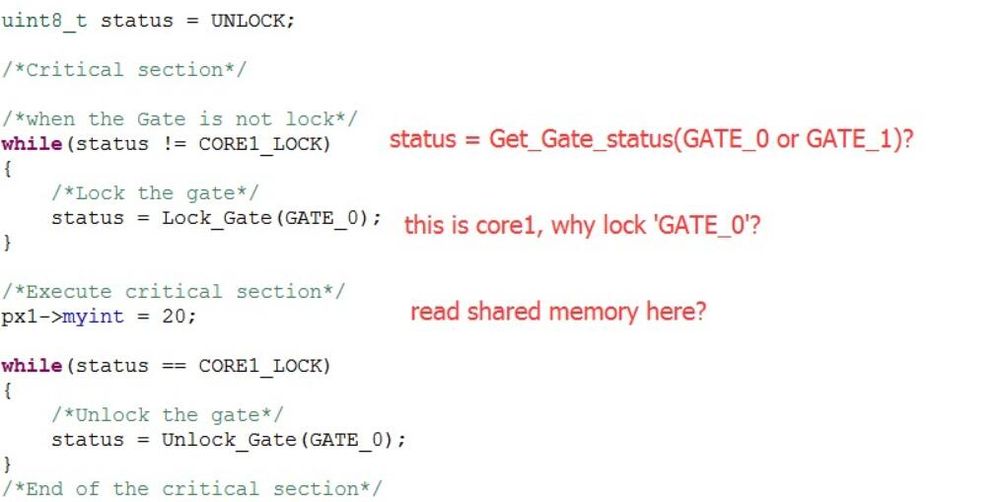

2) status = Get_Gate_Status(GATE0 or GATE1)?

In this example only one gate is used, because there is only one shared resource. So the answer is GATE0. This is also answer for your next question.

3) Read shared memory here?

Yes, after you lock the gate, you are in the critical section and you can use (read/write) shared resource. Just realize, which operations are mutual.

read/read - not mutual...more cores can access shared resource

write/read - mutual exclusion

write/write - mutual exclusion

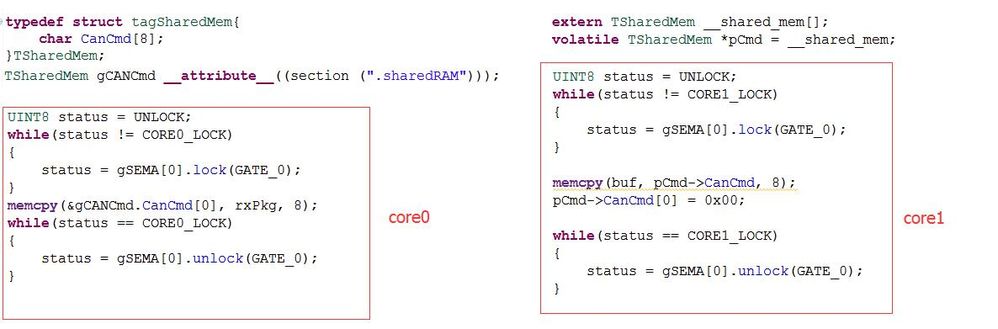

About the use case you describe I do not understand much, but I suppose you have some array called CanCMD[8]. If you want to write to this array, core0 should lock the gate0 and write to the array, then unlock the gate. Core1 has to wait, until gate0 is unlocked. Then core1 locks the gate, reads data from array and unlocks the gate.

Check in the debugger, if memcpy function copies correct data to the correct address and also if pcmd points to correct address.

Regards,

Martin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Martin,

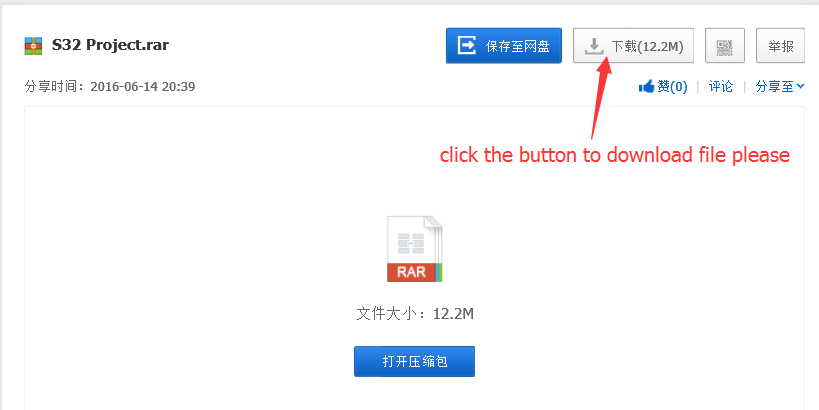

I create a new project. It has the sample problem. I'm confused that I don't know how to upload the code file in the NXP community. So I upload it to the Baidu cloud disk. I'm not sure whether you can download or not.

http://pan.baidu.com/s/1kVpRPOF

My personal email address is ron.liu@live.com. If you have any problem to get it. Please send me an email. I will send it to you as an attach again.

Regards,

Ron

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Ron,

you do not have initialized the shared RAM. Each core initialize only 384K. Please edit mem.ld file for z4 core. Use the following code SRAM_SIZE = 1280K; instead of SRAM_SIZE = 384K;

Now it should works.

Regards,

Martin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, Martin,

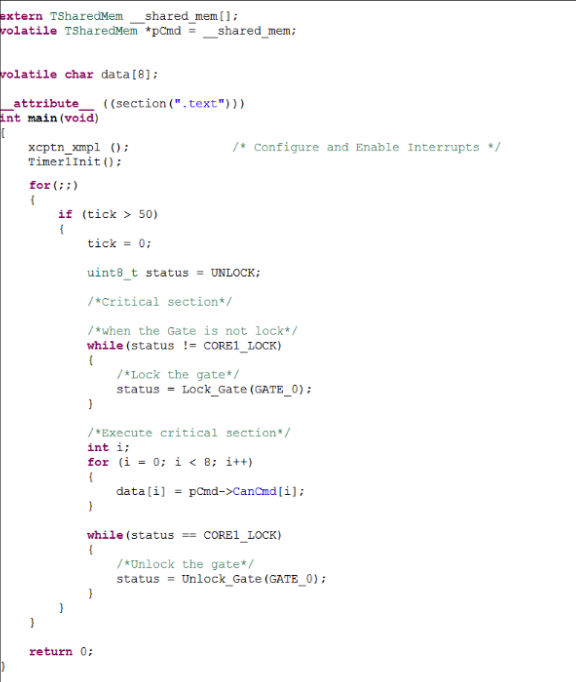

I modified the mem.ld for z4. And it works now. It no longer jump to the IVOR1_Vector(). However there is still a problem. The data is been refreshing all the time in the core0, but I couldn't get the updated data in the core1. In other words, I'm able to see the changing data in core0 and constant data in core1 in the watching windows. Is it the right way to read data in the picture below?

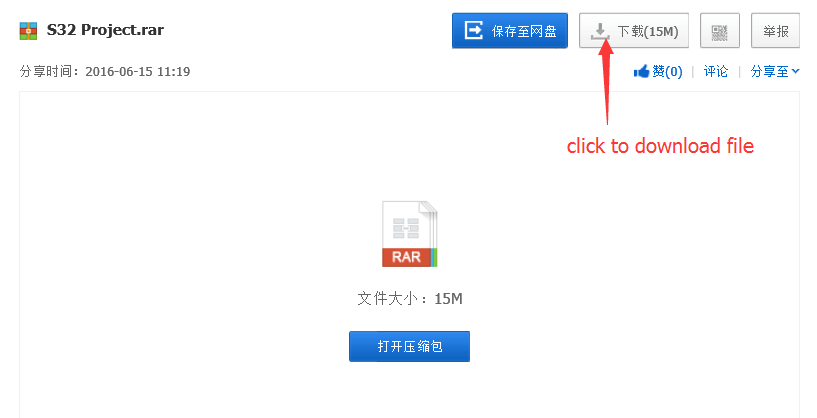

And I upload the new project in the cloud disk. You may download and debug it. http://pan.baidu.com/s/1c1RJ8Qk .

Thanks again.

Ron

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

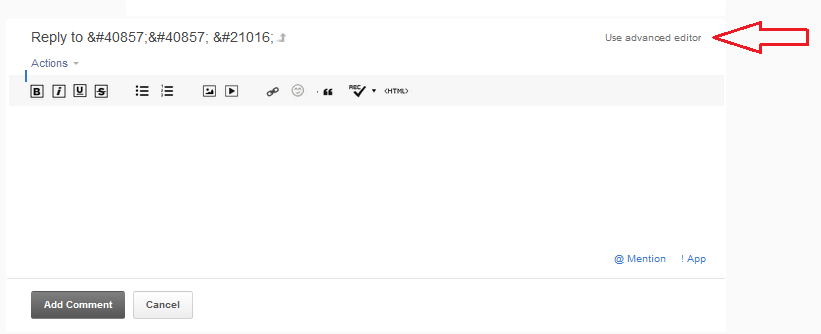

Hi Ron,

please use the advanced editor feature. There is option attach, which could be used to upload your projects.

Regards,

Martin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

And when I try to lock the gate. IVOR1_Vector() appears.

Then I could not trace it by the IDE.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Ron,

please look at the following example. I tested it with PeMicro debug probe in S32DS and I did not get any IVOR exception.

Example MPC5775K Semaphores S32DS

What do you mean by communication between cores? If you want to send messages from one core to another, you can use shared memory. For this purpose the example mentioned above is also usable.

If you have any other question, please feel free to write me back.

Regards,

Martin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Martin,

Thanks. You are right. I'd like to send messages from one core to another. And I have tested your example. Following what you said, I modified the mem.ld and section.ld. But there are still some parts in your example I could not understand. Please pay attention to the red lines.

In the core0,

In the core1,

My project is that the core0 gets commands from CAN bus and then core0 sends the commands to core1 through shared memory. I'm not clear how to lock and unlock cores.

The problem is that I could not read the correct data in the core1.

Regards,

Ron