- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Re: uboot logo color is not normal

uboot logo color is not normal

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Community,

board: imx6q;

version: u-boot-2009.08;

i did what this doc said: https://community.nxp.com/docs/DOC-98109

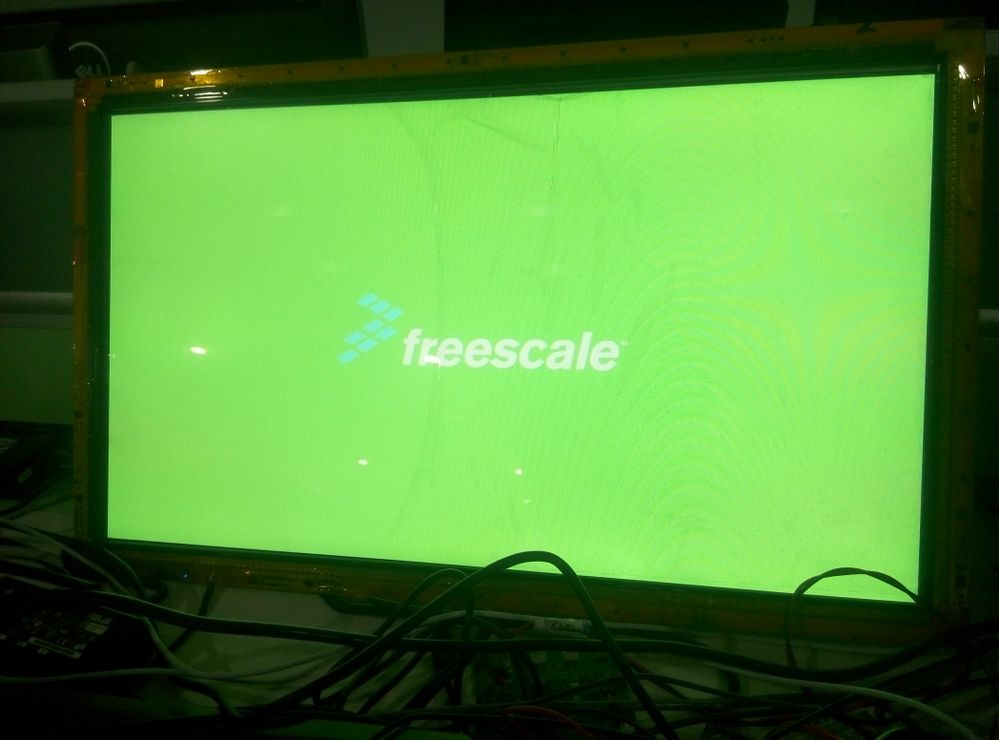

but the logo color is not normal, it si green like this:

what is wrong? and this is my head file:

//#define IPU_OUTPUT_MODE_HDMI

#define IPU_OUTPUT_MODE_LVDS

// #define IPU_OUTPUT_MODE_LCD

#ifdef IPU_OUTPUT_MODE_LVDS

// For LVDS, 1920*1080 resolution, dual channel

#define DISPLAY_WIDTH 1920

#define DISPLAY_HEIGHT 1080

#define DISPLAY_BPP 32

#define DISPLAY_IF_BPP 24 // RGB24 interface

#define DISPLAY_HSYNC_START 80

#define DISPLAY_HSYNC_END 68

#define DISPLAY_HSYNC_WIDTH 12

#define DISPLAY_VSYNC_START 15

#define DISPLAY_VSYNC_END 15

#define DISPLAY_VSYNC_WIDTH 8

#define DISPLAY_PIX_CLOCK 139526400 //(DISPLAY_HSYNC_START + DISPLAY_HSYNC_END + DISPLAY_HSYNC_WIDTH + DISPLAY_WIDTH) *

(DISPLAY_VSYNC_START + DISPLAY_VSYNC_END + DISPLAY_VSYNC_WIDTH + DISPLAY_HEIGHT) * refresh rate (60Hz)

#define LVDS_SPLIT_MODE // For dual channel split mode.

#define DISPLAY_VSYNC_POLARITY 1

#define DISPLAY_HSYNC_POLARITY 1

#define DISPLAY_CLOCK_POLARITY 1

#define DISPLAY_DATA_POLARITY 0

#define DISPLAY_DATA_ENABLE_POLARITY 1

#define IPU_NUM 1 // 1 for IPU1, 2 for IPU2.

#define DI_NUM 0 // 0 for DI0, 1 for DI1.

#define LVDS_PORT 0 // 0 for LVDS0, 1 for LVDS1.

#define DI_CLOCK_EXTERNAL_MODE //When clock external mode was defined, the DI clock root will be PLL3 PFD1,

//without this macro, the DI root clock is IPU internal clock.

nothing changed, just above, can you help me? what should i do? what is info do you need? tell me.

wating for your reply?

thank you.

fulinux.

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I had identified the issue, please apply the attached uboot patch to fix it.

it is based on JB4.3_1.1.1_uboot_logo_keep_patch_2015-09-18.zip

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Li,

1、my kernel displays ok,, not hardware problem.

2、"Do you just used three pair of LVDS data lane?" what does this mean?

3、i haved tried set "#define DISPLAY_IF_BPP 24 " to 18, it is also green color , but color become lighter.

i thank split mode need di0 and di1, but i see this:

#ifdef LVDS_SPLIT_MODE

reg |= (1 << 4);

if (DI == 0)

reg |= (1 << 0);

else if(DI == 1)

reg |= (3 << 0);

#endif

should i delete "if and else" to set di0 and di1 together?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

How about your video mode parameters in kernel?

And which patch do you use? Please also attach your panel datasheet, is it a YUV panel?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

kernel:

drivers/video/mxc/ldb.c

static struct fb_videomode ldb_modedb[] = {

...

{

"LDB-1080P60", 60, 1920, 1080, 12048,

80, 68,

15, 15,

12, 8,

0,

FB_VMODE_NONINTERLACED,

FB_MODE_IS_DETAILED,},

{

//67.3MHZ 67326600

"1080P60", 60, 960, 1080, 14853,

0, 50,

0, 31,

66, 60,

0,

FB_VMODE_NONINTERLACED,

FB_MODE_IS_DETAILED,},

arch/arm/mach-mx6/board-mx6q_sabresd.c:

static struct fsl_mxc_ldb_platform_data ldb_data = {

.ipu_id = 0,//1

.disp_id = 1,

.ext_ref = 1,

.mode = LDB_SEP1,

.sec_ipu_id = 0,//1

.sec_disp_id = 0,

};

i use this L3.0.35_4.1.0_uboot_logo_keep_patch_2013-11-22.zip,

[fulinux@ubuntu uboot-imx]$ git branch

* imx_v2009.08_3.0.35_4.1.0

[fulinux@ubuntu uboot-imx]$ git log

6bd825c ENGR00327364 iMX6x: Ensure that the bandgap self-bias circuit is disabled after boot. (Ranjani Vaidyanathan, 1 year, 7 month

5caea2f ENGR00329930-2 MMC: Fix debounce problem in the tuning algorithm (Ye.Li, 1 year, 8 months ago)

...

i have modified nothing before patch, but i add backlight power gpio code:

static void setup_lvds_iomux(void)

{

....

#if 1

gpio_direction_output(IMX_GPIO_NR(1, 2), 1);

udelay(10*1000);

gpio_set_value(IMX_GPIO_NR(1, 2), 0);

udelay(10*1000);

gpio_set_value(IMX_GPIO_NR(1, 2), 1);

gpio_direction_output(IMX_GPIO_NR(4, 5), 1);

udelay(10*1000);

gpio_set_value(IMX_GPIO_NR(4, 5), 0);

gpio_direction_output(IMX_GPIO_NR(1, 7), 1);

udelay(10*1000);

gpio_set_value(IMX_GPIO_NR(1, 7), 1);

#endif

}

anything info which you need, tell me. this problem makes me very anxious.

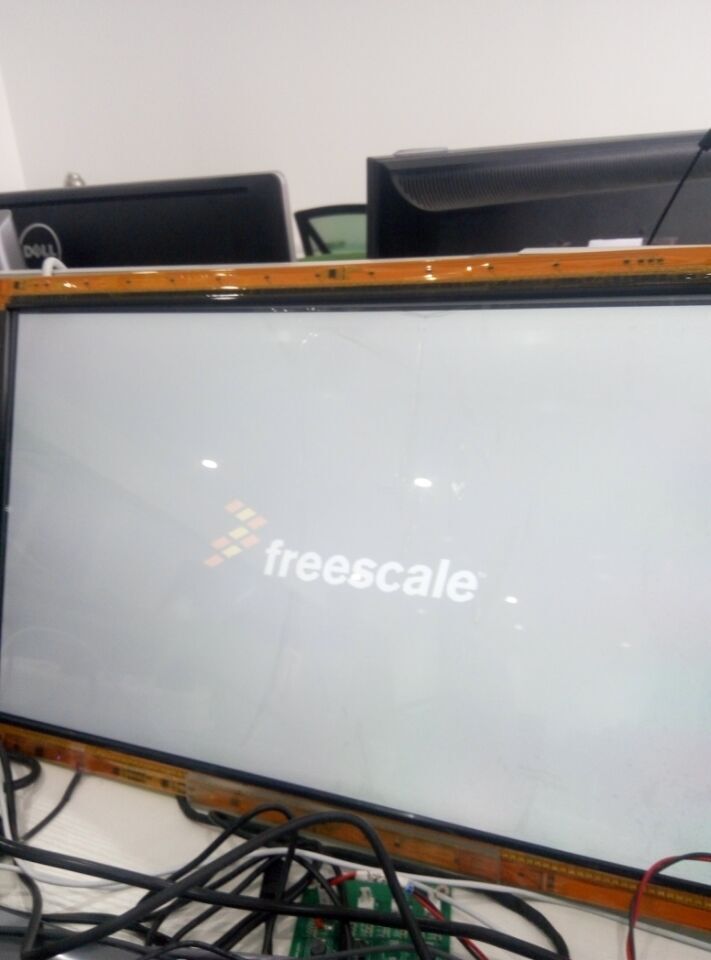

and when i change " #define DISPLAY_BPP 32" to 24, and change "logo_1024x768_24bpp.bmp" to "logo_1920x1080_24bpp.bmp", and then screen like this:

but i am sure my lcd panel support 32bpp, because uboot bootargs is :

"video=mxcfb0:dev=ldb,1920x1080M@60,if=RGB24,bpp=32 consoleblank=0 ldb=spl0 ldo_active=on fbmem=128M" and kernel displays ok!

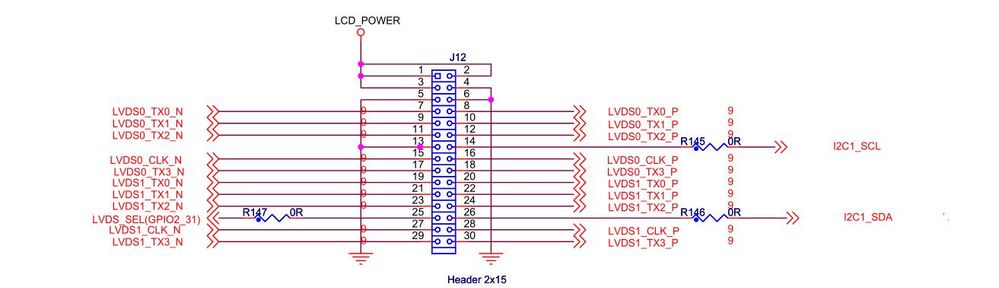

this is panel schematic:

Waiting for you reply!

thankyou,

fulinux.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You should not use 24bpp bmp file, it should be original 32bpp "logo.bmp", and set DISPLAY_BPP to 32 to align with the bmp file.

From your kernel video mode setting, your panel is VSYNC low active, HSYNC low active, pixel clock high active, Date enable low active. So your UBoot setting should be followed:

#define DISPLAY_VSYNC_POLARITY 0

#define DISPLAY_HSYNC_POLARITY 0

#define DISPLAY_CLOCK_POLARITY 1

#define DISPLAY_DATA_POLARITY 0

#define DISPLAY_DATA_ENABLE_POLARITY 0

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

i test as you said, it shows white, red and blue loop, this is my head file:

// For LVDS, 1920*1080 resolution, dual channel

#define DISPLAY_WIDTH 1920

#define DISPLAY_HEIGHT 1080

#define DISPLAY_BPP 32

#define DISPLAY_IF_BPP 24 // RGB24 interface

#define DISPLAY_HSYNC_START 80

#define DISPLAY_HSYNC_END 68

#define DISPLAY_HSYNC_WIDTH 12

#define DISPLAY_VSYNC_START 15

#define DISPLAY_VSYNC_END 15

#define DISPLAY_VSYNC_WIDTH 8

#define DISPLAY_PIX_CLOCK 139526400 //(DISPLAY_HSYNC_START + DISPLAY_HSYNC_END + DISPLAY_HSYNC_WIDTH + DISPLAY_WIDTH) *

(DISPLAY_VSYNC_START + DISPLAY_VSYNC_END + DISPLAY_VSYNC_WIDTH + DISPLAY_HEIGHT) * refresh rate (60Hz)

#define LVDS_SPLIT_MODE 1 // For dual channel split mode.

#endif

#define DISPLAY_VSYNC_POLARITY 0

#define DISPLAY_HSYNC_POLARITY 0

#define DISPLAY_CLOCK_POLARITY 1

#define DISPLAY_DATA_POLARITY 0

#define DISPLAY_DATA_ENABLE_POLARITY 0

#define IPU_NUM 1 // 1 for IPU1, 2 for IPU2.

#define DI_NUM 0 // 0 for DI0, 1 for DI1.

#define LVDS_PORT 0 // 0 for LVDS0, 1 for LVDS1.

#define DI_CLOCK_EXTERNAL_MODE //When clock external mode was defined, the DI clock root will be PLL3 PFD1,

//without this macro, the DI root clock is IPU internal clock.