- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- Clear PWM channel output after StopOnOverflow (KL17Z) ?

Clear PWM channel output after StopOnOverflow (KL17Z) ?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

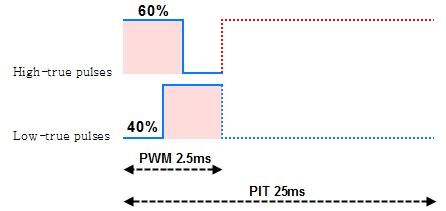

I'm trying to perform high-resolution PWM pulse generation when the pulse high width (1.5 ms) is relatively short (and of more significance) compared to the overall PWM period (~25 ms). To do this, I have:

- set up a PIT timer with a 25 ms period

- set up a TPM timer in edge-aligned PWM mode running at 400 Hz and a duty cycle of 60%

- enabled StartOnTrigger and StopOnOverflow on the TPM channel, and set the PIT timer overflow as the trigger source

What I expected to see was that when the PIT timer overflowed, this would trigger the TPM to start counting up, and the output from the TPM timer would:

1) go high initially

2) stay high for the duration of the 60% ON duty cycle

3) then go low during the 40% OFF duty part of the cycle

4) and remain low when the TPM overflows, until the next PIT trigger occurs.

What I am seeing is ok for steps 1, 2, and 3, but when the TPM overflows, the PWM output goes high and remains high until the next PIT trigger occurs. I haven't found anything in the reference manual to describe how the PWM channel output value should behave when overflow occurs and StopOnOverflow is enabled. It seems (although it is a bit of a guess by me) as if the TPM overflow causes the counter to stop (as intended), but also causes the counter value to reset to zero and the PWM output to go high in anticipation of the PWM operation continuing some time in the future.

Is there any way to clear the TPM PWM output value when a StopOnOverflow event occurs ? I considered using the TPM overflow interrupt to force the output low, but I haven't been able to find a register to write to for the TPM channel output value.

I can post code snippets and/or logic analyser screenshots if it helps.

At this stage, my workaround is to revert to a conventional PWM approach without a PIT trigger, and just accept that I will lose a few bits of resolution on the width of the high pulse. I have seen this post which suggests what I am asking is not possible with a KL17Z, but I would really like to get the above approach working if possible.

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi geoff_s,

Initialise these pins as GPIO output pin and set it low at the begining.

Then initialise these pins as TPM output.

Mux these pins as GPIO in TPM timer channel interrupt.

Mux these pins as TPM output in the tenth TPM timer channel interrupt, or in PIT timer interrupt .

Best Regards,

Robin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks Robin. That is one of the options I have been playing with, and does more or less work. It effectively becomes a "trailing edge-aligned" PWM which is a minor downside for my ultimate application (where multiple PWM signals will be produced simultaneously) but might be worth considering.

// just some defines here to make it easy to switch between alternative approaches to creating the 50Hz PWM signal

#define OPTION_1 1 // generate PWM conventionally using TPM module

#define OPTION_2 2 // generate PWM by using overflow of PIT timer to trigger single-shot pulse from TPM module

#define OPTION_3 3 // generate PWM by using overflow of PIT timer to trigger single-shot pulse from TPM module - but with hacks to workaround apparent bugs (or my misunderstandings)

#define OPTION_4 4 // generate PWM by using overflow of PIT timer to trigger single-shot pulse from TPM module - but use TPM0 overflow interrupt to re-mux pin as GPIO and then force output low

#define OPTION_5 5 // use output compare mode instead

//********************************************************************************************************

// ************* change option in following line depending on which option you prefer ********************

#define PWM_GENERATION_OPTION OPTION_3

I have since come across these posts which suggest the TPM output goes into a floating high-impedance state when the TPM timer overflows. This looks like an un-documented (and illogical) feature of the TPM module. They suggest that it is possible to enable the internal pull-down resistor to force the output low, but I haven't had any success with this method.

Does FTM output when timer is stopped go high impedance?

I've also tried using the TPM timer overflow interrupt to switch the TPM output to a GPIO output pin and set it low - that isn't working at the moment, but I suspect it is my interrupt handling routine that might be at fault. Frustrating...

Thanks for the suggestion though ![]() I like your timing diagrams - what did you create them in ?

I like your timing diagrams - what did you create them in ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi geoff_s,

Initialise these pins as GPIO output pin and set it low at the begining.

Then initialise these pins as TPM output.

Mux these pins as GPIO in TPM timer channel interrupt.

Mux these pins as TPM output in the tenth TPM timer channel interrupt, or in PIT timer interrupt .

Best Regards,

Robin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have tried, but can't get the TPM interrupt working. I set an interrupt routine for PIT overflow (toggle an output pin so I can check it on the logic analyser) without any problems, but as soon as I enable TPM interrupts, neither the TPM nor PIT interrupt routines seem to work. I've tried debugging in KDS but it isn't stopping at the breakpoints I set on the interrupt routines (I'm using a Segger J-Link), so I am really lost and frustrated :smileyconfused:

I've attached a very basic test project. If anyone can see the reason for my problems, I would be very, very grateful.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have it working. Some minor bug fixes in my code, plus deleting and recreating the debug configurations in KDS seems to have cleared out all the problems.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi geoff_s,

I am not sure whether you will accept Low-true pulses Edge-aligned PWM.

- set up a PIT timer with a 25 ms period

- set up a TPM timer in edge-aligned PWM mode running at 400 Hz and a duty cycle of 40% (Low-true pulses)

- enabled StartOnTrigger and StopOnOverflow on the TPM channel, and set the PIT timer overflow as the trigger source

Best Regards,

Robin