- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- Re: K10 processor reset pin always low

K10 processor reset pin always low

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

We have just produced some boards that uses the K10 processor.

I have been unable to program these virgin boards via the JTAG.

After some investigation it appears that the reset pin is always low.

The reset pin is connected to the 3.3v power rail via a 10K resistor and a 1nF cap to ground.

When the board is powered the reset pin remains low.

I cannot therefore use the JTAG port to program the processor for the very first time since the processor is held in reset.

Is there some other pin that I need to set the state of to bring the processor out of reset?

Any suggestions?

Regards.

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Dieter and Hui_Ma

The problem is now sorted and I can program our K10 processors.

Thanks for your help guys, it was appreciated.

To get our board working I did the following:

1) Slowed the power supply rise time by using a 10ohm resistor with a 47uF cap. On our board this gave a rise time of about 4ms which is probably more than I need but I didn't want to risk an improper POR.

2) We had a pull up resistor on the TDO line. This was removed so our board has no pull up or pull down on this line.

3) We had a pull down on the TDI line. This has been changed to a pull up.

4) We had 100ohm protection resistors to each of the JTAG pins and to the reset pin. These were all reduced to zero ohms.

We probably didn't need to do all of the above changes to make it work.

The next step is to determine exactly what are the necessary changes.

That should be easy now.

Thanks again.

Regards

Nasir

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

Please refer the <KQRUG> document chapter 2.1.5.3 about Kinetis debug interface.

The JTAG_TMS signal on PTA3 requires a strong pullup resistor for mode selection. The Cortex Debug specification

recommends that the JTAG_TCLK and JTAG_TDI pins (on PTA0 and PTA1) have pull resistors (high or low) to force a known state on these debug input pins.

Please check the K60 product solder processing, the peak solder temperature should below 260°C.

And please measure the RESET_b pin impedance with GND.

It will check if there with short connection of Reset pin with GND.

Wish it helps.

Have a great day,

Ma Hui

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

dear Hu_Ma

i was looking thru the forum for my particular problem but cannot find any solution other than this reset problem

but my problem is worst,

i am using the MK10DN64VLF5 CPU

i have been using MK10DX128, MK60, MK64, MK20, so i am quite experienced in M4 ARM cpu

all of them has the same jtag connection with the same reset RC and they all work well

but this particular cpu using exactly the same circuit cannot even be erased using the segger jlink

so of course, it cannot enter debug at all.

i have tried to change the reset cap value smaller than 1uF and also tried to power up the VCC slowly but it still cannot be erased or enter debug

i noticed that the jlink can detect the cpu type but it output a lot of error messages that we cannot understand and since there are no circuit between the cpu and the 10pin jtag connector, we are at a loss to troubleshoot the problem.

i have even remove the chip to check on it and the circuits and replaced with another cpu but still having same problem

i do have a pullup on TMS via 1K to a led at 3.3v, i have done this with other cpus about without any problems. so I do not suspect this.

anyway, i will put a pullup to TMS and also NMI just in case but i doubt it work.

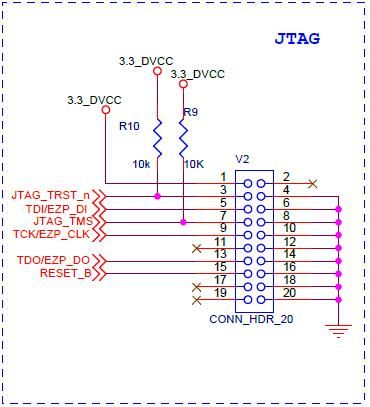

pls see attached files on the circuit and jlink output

i have 500 board to produce immediately but my 15 prototypes has this same problem

and i am running out of time to deadline.

so i need your help desperately

john

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Iam trying to program a custom made k60 board using mutilink jtag. Intialy for two three times it got programmed.But later it didnt get programmed. The reset_b and EZP_CS got low. So as said above i have added 10ohm resistor with a 47uF cap at the reset_b pin. Then the reset_b and ezp_cs pin got high. But still iam not being able to program it, I have pulled up the TDI pin also, the following error appears on kinetis studio

command line arguments: -device=K60FX512 -startserver -singlesession -serverport=7224 -interface=USBMULTILINK -speed=5000 -port=USB1 -USE_CYCLONEPRO_RELAYS=0 -FORCE_MASS_ERASE=0

Device selected is k60fx512

User Specified Hardware Selection : Interface=USBMULTILINK and Port=USB1

Connecting to target.

P&E Interface detected - Flash Version 9.33

Can not enter background mode .

Unable to initialize PEDebug.

PE-ERROR: Failed to Initialize Target

Server running on 127.0.0.1:7224

Connection from "127.0.0.1" via 127.0.0.1

PE-ERROR: Target is not connected

Disconnected from "127.0.0.1" via 127.0.0.1

Target Disconnected.

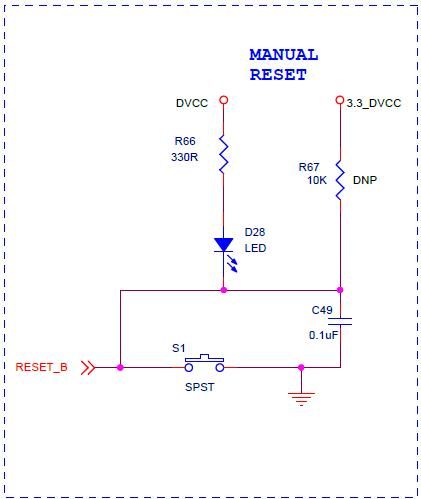

The circuit of reset portion and jtag are attached.Please help.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi all,

We are facing the same reset problem in our custom K70 board. The reset pin is always low. We have pulled the reset pin up externally using 10k resistor. EzPort pin is also pulled high through 10k resistor. We aren't able to trace why this persists.

Your inputs would help us a lot!

Thank You!

Regards,

Felicita.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

It need to check /EZP_CS pin to make sure this pin keep high voltage during the reset phase.

While, I don't think that pin could affect Reset pin status.

Our TWR-K60N512 board using 0.1uF cap connect reset pin to ground.

You can remove 1nF cap to check if the reset pin could be pull up to high voltage.

If the reset pin still with low voltage, it need to check if there exists short connection issue.

Wish it helps.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

When i tried to run a KL10 that did not connect to the SWD debugger, i saw a sawtooth wave on its reset pin. This waveform is the result of K10 internal action. I could also see in phase supply current variations.

When i made the time constant of the reset pullup and capacitor smaller, i finally got it running for about 1.5 microseconds after it released the Reset pin. This happened about every 10 or 20 usec and it was enough for the debugger to connect and begin the first flash operation.

SWD debugging depends on so many factors and its a miracle how well it works once you got it running. On the other hand, there are many ways to get the Kinetis stuck. I can't really say what was wrong inside the K10. Maybe watchdog, maybe odd address, maybe SWD pin disabled, maybe a race condition. For example SWD cannot halt the Kinetis, once you have a stuck interrupt, i mean one that never gets cleared. In that case only a power cycle may help, or a reset switch. The SWD does not allow you to reset the device before it got halted.

The K10 mask 1N36B also has an erratum 4949 "Reset and Boot: Device may not exit the power on reset (POR) event correctly with fast ramp-up slew rates." that you should be aware of.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Dieter

Thank you very much, that was very helpful!!

What you describe is exactly what I am seeing.

My primary problem is that I cannot get the debugger to connect because the reset line is low most of the time.

I erased my K20 tower, repowered it and it too showed the sawtooth waveform on its reset pin.

But the debugger then connects to it everytime and I am able to program it, which is strange based upon your experience.

Are there any pins, whose state I need to be careful about eg that require a pullup or pulldown?

If there is anything else you can suggest that may help to get the debugger going, it would be appreciated.

Thanks again.

Regards

Nasir

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The erratum means that we have to power up the K10 slowly (risetime of some msec, for example 10 Ohm/470 uF). Then the POR works as expected and the Reset pin comes free. Another requirement is that we have a capacitor of 10 nF or more close to the reset pin in order to avoid glitches close to the switching point.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear sir,

We are facing same problem.we are using K60 board....Kinetis K60 not able to program

by using RC values at reset (10ohm,47uf).the rest voltage and /EZP_CS goes high but the problem not has solved yet,We cannot program the ic.so please tell me solution

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks Dieter, your help has been appreciated.

I will try this soon, hopefully it works.

Regards

Nasir

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Hui_Ma

Thanks for the reply.

I have tried all your suggestions but the reset pin is still low.

There is no short to ground, the processor itself is holding the reset pin low.

I have even removed all components around the processor apart from the power supply caps and the reset pin Resistor and Capacitor yet the reset pin still remains low.

If anyone has any suggestions it would be appreciatd.

Regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I check dieter suggested to check the errata e4949 about "Reset and Boot: Device may not exit the power on reset (POR) event correctly with fast ramp-up slew rates." Please check the power up with voltage instantaneous slew rate of VDD below 17 kV/sec. Please let us know your test result.

Thank you for the attention.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Dieter and Hui_Ma

The problem is now sorted and I can program our K10 processors.

Thanks for your help guys, it was appreciated.

To get our board working I did the following:

1) Slowed the power supply rise time by using a 10ohm resistor with a 47uF cap. On our board this gave a rise time of about 4ms which is probably more than I need but I didn't want to risk an improper POR.

2) We had a pull up resistor on the TDO line. This was removed so our board has no pull up or pull down on this line.

3) We had a pull down on the TDI line. This has been changed to a pull up.

4) We had 100ohm protection resistors to each of the JTAG pins and to the reset pin. These were all reduced to zero ohms.

We probably didn't need to do all of the above changes to make it work.

The next step is to determine exactly what are the necessary changes.

That should be easy now.

Thanks again.

Regards

Nasir