- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Re: SGTL5000 on IMX6 with external SYS_MCLK

SGTL5000 on IMX6 with external SYS_MCLK

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Everyone,

I am designing a board with SGTL5000 for the audio codec. I currently have connected an external 24MHz clock directly to the codec to provide the SYS_MCLK signal.

When playing audio for periods the quality is very good but then for periods I get a lot of noise and the the audio seems to switch rapidly between left and right channels.

Must the SYS_MCLK signal be synchronous (generated by the cpu) to the CPU's clocks? Currently I imagine something is drifting in and out of sync.

How accurate must the CLK actually be?

I am trying to find another suitable clock available on my board to test this.

James

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi James

in general one can check solder profile

http://cache.nxp.com/files/microcontrollers/doc/app_note/AN3298.pdf

~igor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Many thanks for the quick response. I have done some further inverstigations and can now see that there isn't a problem synchronising the sample data over I2S bus, that is clocked using its own I2S_SCLK.

I changed the SYS_MCLK freq in the device tree (from 24Mhz to 20Mhz) for an experiment and the audio then gets quicker and higher in pitch just as speeding up a record.

Still I get the problem with the bad noise occasionally, but most of the time the quality is perfect.

I have since replaced with a fresh chip, and I thought it had worked but the noise came back after 10 minutes or so.

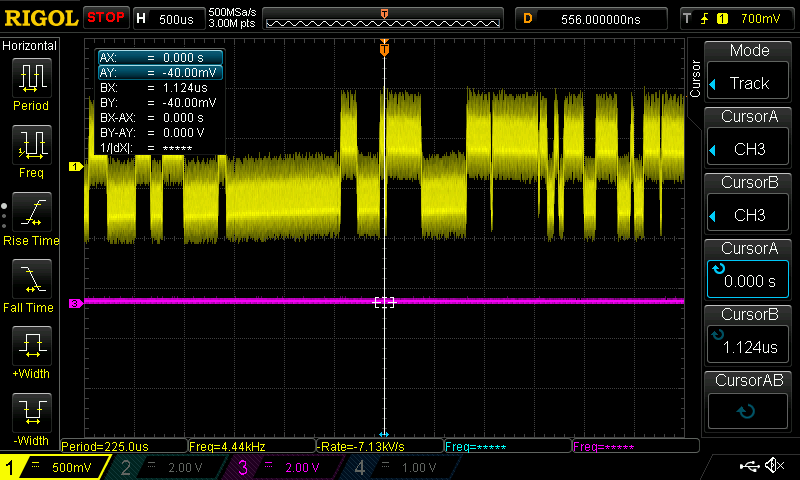

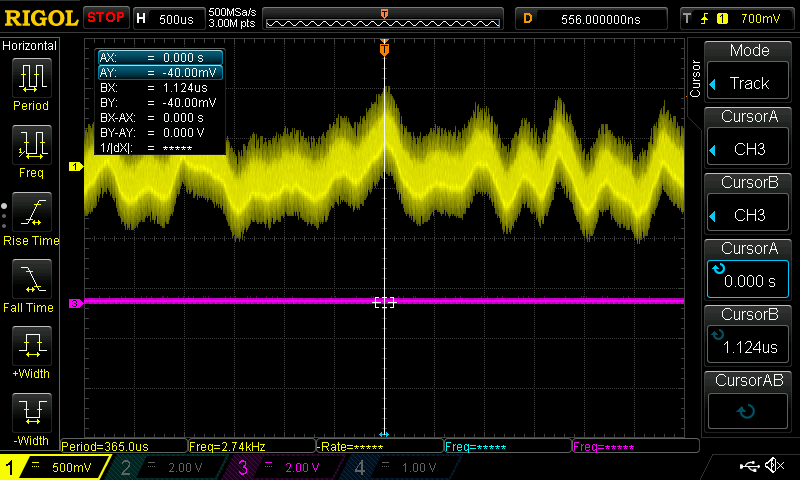

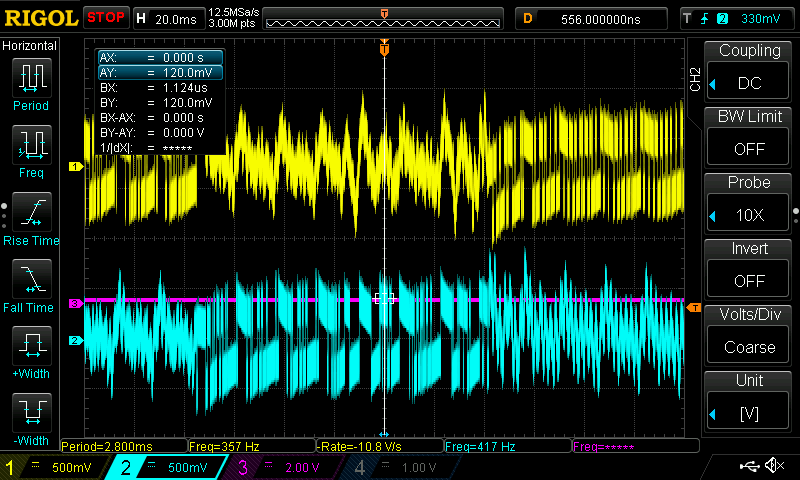

Below is a capture on my oscilloscope of the audio signal when its bad, and further a normal one.

I also looked at the audio ground, and all input supplies, they are all stable and don't show any noise that would relate to that shown above.

A quick question about the VDDD supply, it says we have revision 0x11 on linux. Does that mean our external VDDD cannot be used? Could this have an effect on our signal quality?

sgtl5000 2-000a: sgtl5000 revision 0x11

fsl-asrc 2034000.asrc: driver registered

2-000a: 1200 mV normal

sgtl5000 2-000a: Using internal LDO instead of VDDD

Many thanks,

James

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi James

one can ignore linux comments about revision. Only valid document

about VDDD is official errata

http://cache.freescale.com/files/analog/doc/errata/SGTL5000ER.pdf

also useful link

SGTL5000: external VDDD with linux codec driver

~igor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Igor,

Thanks for the helpful information. I have now found out what is happening. Just thought I'd document it here in case anyone else sees this phenomena.

I noticed that putting a fresh chip on makes the sound quality perfect for a few minutes. After a day of frustration and the quality being really bad, a lot of pops and clicks and that unusual square noise, I decided to reflow the chip... but not replace it. Voila, the quality is absolutely perfect... not a single click or pop.

However I am noticing that as the solder cools further or oxidises, then the quality seems to degrade again and the square noise problem comes back (but then the signal quality is already really bad).

I am using a lead-free solder paste.

Did you ever see that before? I wasn't aware that the solder would degrade after it was set in such a short space of time and cause such poor performance on signal integrity.

Seems like with audio you can literally hear it.

Thanks for your help, you've been very responsive.

James

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi James

in general one can check solder profile

http://cache.nxp.com/files/microcontrollers/doc/app_note/AN3298.pdf

~igor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for the useful information. I'm using some amateur proto-typing tools. I'll take the board to my local lab and have them steam-phase solder the chips.

Also many thanks for being so helpful and responsive. Positively surprised at the high quality of freescale/nxp technical support.

James

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Just wanted to provide an update on how we solved our issue in the end. It turned out not to be a problem of solder.

We had to attach 100pF caps to the SCLK, DIN, and DOUT lines for the SSI interface.

Our transmission lines we're quite long.

Now we have perfect audio quality.

James

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Some further information... I have since discovered that this noise switches between channels when it is active.

It never appears on both L and R channels at the same time.

You can see the square waves switching between channel.

James

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi James

there is no need for SYS_MCLK signal be synchronous,

clock requirements can be found in sgtl5000 datasheet

http://cache.nxp.com/files/analog/doc/data_sheet/SGTL5000.pdf

may be useful to look at AN3363 SGTL5000 Initialization and Programming

http://cache.nxp.com/files/analog/doc/app_note/AN3663.pdf

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------