- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- Product Forums

- :

- MPC5xxx

- :

- Re: MPC5676R REFRENCE MANUAL

MPC5676R REFRENCE MANUAL

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

MPC5676R REFRENCE MANUAL

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

HI ,

I AM READING MPC5676R REFERENCE MANUAL CHAPTER 18 (EMIOS)

18.3.2.4 ,18.3.2.5 AND 18.3.2.6 IN THIS REGISTER WHAT IS MEANING OF A[0:23] 0R B[0:23]

HOW TO KNOW ABOUT A1/A2 OR B1/B2 REGISTER INFORMATION

HIS ANY THING WRONG WITH A[0:23] 0R B[0:23] BITS MENTIONING IN THOSE REGISTERS

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Do not mix the GPIO functionality of the SIU module and eMIOS GPIO modes.

Some words from manual…

All GPIO functions for the device are provided by the SIU. Each device pad that has a GPIO signal has a pin configuration register (PCR) in the SIU where the GPIO function is selected. In addition, each device GPIO signal has an input data register (SIU_GPDIn) and an output data register (SIU_GPDOn). The SIU also implements several parallel GPIO registers (SIU_PGPDOx_x and SIU_PGPDIx_x) that can be used to access up to 32 GPIO bits in a single- and word-sized accesses. The values read/written to these parallel registers are coherent with the data read/written to the SIU_GPDOx_x and SIU_GPDIx_x registers.

If the MCU pad is configured for the eMIOS function and eMIOS channel is set to GPIO input/output mode then

- For GPIO input mode, the input pin status can be determined by reading the channel CSRn[UCIN] bit.

- For GPIO output mode, the unified channel is used as a single output port pin and the value of the CCRn[EDPOL] bit is permanently transferred to the output flip-flop.

BR, Petr

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks a lot,

Hi,

I need some more helpful to go feather clearly according to requirements.

I have some queries

1. I seen some sample codes for emios module there are using mainly 1MHZ to emios channels i.e the frequency coming from system clock(PLL) and after that they divides that pll with some global values to generates 1MHZ is there any specific to having only 1MHZ.

2. I am using channel 23 has counter bus how to write the values in CADR register and how to calculate counter period.

3. Suppose if have to generate 5KHZ frequency pulse wave has out put what values in register CADR and CBDR should we write to get that frequency. Is there any calculations for CADR and CBDR writing values with respective counter (channel 23) also to generates required wave form has output.

4. Now i am using mpc5676R RM with rev 5.0 i am not seeing many block diagrams and full information for emios module how to get latest updated RM with new rev.

Thanks & Regards

mpc5676r

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

thanks petr for response,

- suppose if i am using emios has gpio input and out put mode i hope i should work this register which is mention in mpc5676r RM

- 3.2.1.34 Parallel GPIO Output Register (SIU_PGPDO0 - SIU_PGPDO15)

- 3.2.1.35 Parallel GPIO Input Register (SIU_PGPDI0 - SIU_PGPDI15)

- my query is why they mention only 16 PGPDO and 16 PGPDI bits ? why not

- in emios i have 32 channels suppose if i have use 20 channels has input how is possible to do with above register values?

Thanks & Regards

MPC5676R

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

The eMIOS channel features 24-bit registers for captured/match values (A1/A2 or B1/B2) and a 24-bit internal counter. A1/A2 and B1/B2 registers may have different functionality for each mode of operation, this is well described in “Channel Modes of Operation” chapters of the RM.

The eMIOS channel's CADR, CBRD and CCNTR registers are used to access those internal 24bit registers and A[0:23], B[0:23] resp C[0:23] represents a content of those registers.

Note: depending of used mode the CADRn, CBRDn reading/writing accesses A1/A2, B1/B2 registers differently. This is summarized in Table 18-7.

BR, Petr

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks Petr Stancik for your answer

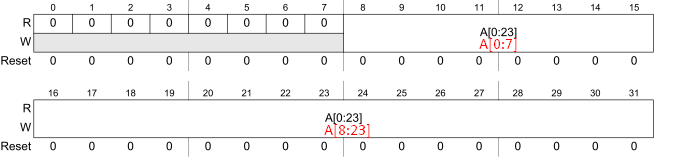

The eMIOS channel's CADR, CBRD and CCNTR registers are used to access those internal 24bit registers and A[0:23], B[0:23] resp C[0:23] represents a content of those registers. I can understand it. My main issue is we have all register of length 32 bits [0:31] but in CADR, CBRD and CCNTR registers are how they mention A[0:23] and A[0:23] two times in CADR, CBRD and CCNTR similarly. Register size is 32 bits how they have mentioned A[0:23] and A[0:23] it means size may cross 32 bits?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

There is 24bit wide writable field in CADR, from bits 8-31. This corresponds to internal 24bit register, bit 8 is the MSB.

Ideally the field description should be

BR,Petr

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks Petr,

Now I am trying to write the driver of EMIOS according requirements.

can I get any sample drivers/sample code/ for emios device. If possible can you share me the links where I can get sample codes to emios .

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Just search over this Community for “eMIOS code”.

For example:

OPWMB: https://community.freescale.com/thread/357241

It is based on eMIOS example given in the AN2865 (http://cache.freescale.com/files/32bit/doc/app_note/AN2865.pdf).

I believe you can create own code similarly for other eMIOS modes based on the individual mode description given in the RM.

BR, Petr