- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Re: IMX6 booting from eMMC - Random failure

IMX6 booting from eMMC - Random failure

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello All,

We have a custom board based on iMX6 quad core processor. It is designed to boot from eMMC, boot setting is from eFuses.

Processor: IMX6 Quad, revision : C

eMMC : MTFC16GJDEC-4M IT ( eMMC v4.41)

uSDHC port : USDHC3

SRC Boot Mode Register 1: 0x00005060

SRC Boot Mode Register 2: 0x30000011

Problem :

We see majority of boards boots as designed. But there are random failures on one or two boards per hundred( 1 to 2% only).

We read the system SRC boot mode registers.Its readings are same for both the working and non-working boards.

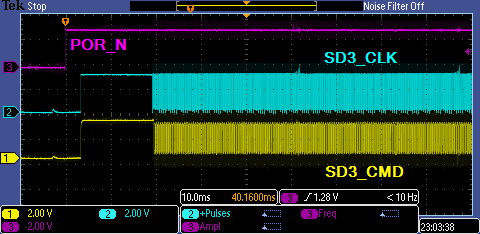

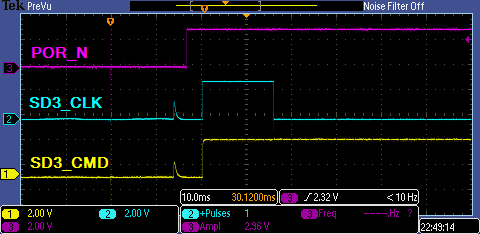

The following signals from i.MX6 are captured for working and non working boards and is as below.

- POR_N ( reset pin)

- SD3_CLK ( clock to eMMC)

- SD3_CMD (CMD line to eMMC)

The waveforms of both working and non working boards are as below

Working Board Waveforms:

Non Working Board Waveforms:

I expect SD3_CLK to toggle at 347.22 KHz( or 400KHz) as IMX6 attempts to boot. After initial CMD exchange between eMMC this clock should switch to 20MHz.

We can see this happen working in correct boards.

In non-booting boards after POR, CLK line stays high for around 16mS and then goes low, its not toggling then and IMX6 is moving to serial downloader mode.

I tweaked the Boot Mode pin settings to serial downloader mode, and observed that SD3_CLK is not changing at all.

This makes me feel that, i.MX6 understands that eMMC is the boot device and attempts to boot from eMMC. But it fails to complete the boot process..???

I extended POR_N so that if the booting problem was due to the timing deviation of internal 200KHz oscillator, it should go away, but there was no luck.

Any help to understand what is happening is really appreciated!!

Few questions came to my mind are :

(A) : Is there a register or memory location that I can access from MFG tool uboot to understand from which stage ( as in fig 8-10,fig 8-11 of reference manual) the booting rolled from eMMC to serial downloader mode.

(B): I went through the application note (TN-29-18: Booting from Embedded MMC e-MMC Device s Supporting MMCA Specification ver.4.3 )from micron. So I was expecting CSD3_CMD line to be held LOW for atleast 74 SD3_CLKs. So any clue where I am wrong? Is there a documentation stating what happens during the boot attempt of i MX6 from eMMC?

(C) Is IMX6 expecting any pattern in the SD3_DATA0 to SD3_DAT7 while SD3_CLK makes its first transition from HIGH to LOW ? And , probably that may be the reason why SD3_CLK stops to make any toggling??

(D) Any directions that can be helpful to understand the issue?

Thanks in advance.

Regards,

Sonu

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sonu

reason may be erratum ERR006282 ROM code uses nonreset PFDs,

which is fixed in rev.1.3 silicon (revision D). To check one can attach jtag debugger

to failed board and output on CCM_CLKO1 (pad GPIO_0 ) clock usdhc3_clk_root divided by 5,

figure out there is(or not) output of usdhc3_clk_root which was sourced from PFD396.

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sonu

reason may be erratum ERR006282 ROM code uses nonreset PFDs,

which is fixed in rev.1.3 silicon (revision D). To check one can attach jtag debugger

to failed board and output on CCM_CLKO1 (pad GPIO_0 ) clock usdhc3_clk_root divided by 5,

figure out there is(or not) output of usdhc3_clk_root which was sourced from PFD396.

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Igor,

Thank You!

On the non booting boards we are not getting the clock but on booting boards we are.

So we are now trying the work around by enabling the WDOG_ENABLE bit fuse.

Thank You.

Regards,

Sonu

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Igor,

The work around mentioned in Freescale erratum is not working for us.

This make me a bit skeptical on whether "ERR006282 ROM code" is our real issue.

Infact our non booting boards never boots.

Is there a possibility that "ERR006282 ROM code" will occur on all power ups?

Is there any way to reset PFD396 from JTAG ? ( I don't know whether this question is silly!)

Thanks for your support.

Regards,

Sonu

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sonu

sorry, if you answered that: "On the non booting boards

we are not getting the clock", this does prove ERR006282 erratum.

How did you connect wdog, it should provide reset pulse on MMPF0100

PWRON also, so whole system with pmic was reset, check

U507 on spf-27392 Sabre schematic.

PFD is described on

http://cache.nxp.com/files/32bit/doc/eng_bulletin/EB790.pdf

i.MX6 D/Q L3.0.35_1.0.3 patch release

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Igor,

Thanks.

I now understand our issue is ERR006282 erratum.

I changed bit 18 of "CCM_CSCMR1" to select USDHC3 clock from PFD352 and i could get the clock!

Now my worry is on the work around. I was wondering whether watchdog timer reset option will work for us.

We see that our board is not booting on all power ups and resets.

So even if the watchdog bites, it will be another reset and board will not boot.

Is there any difference between a watch dog bite reset and manual pulling down of PMIC power ON pin reset?

Any comments?

Thank you for your replies.

Regards,

Sonu

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sonu

difference is that PMIC power ON resets both pmic and processor,

while watchdog only processor. So in ldo bypass case (core voltages

are lowered), pmic voltages will be insufficient to boot-up processor

(at reset processor has ldo enabled configuration).

Best regards

igor