- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- MCUXpresso Software and Tools

- :

- Kinetis Design Studio

- :

- Re: ICS in KEA-128

ICS in KEA-128

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

ICS in KEA-128

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Can anyone say me how to set the ICS module registers for making the system clock run at 24 Mhz in KEA-128?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

we can use FEI mode to generate 24M bus clock.

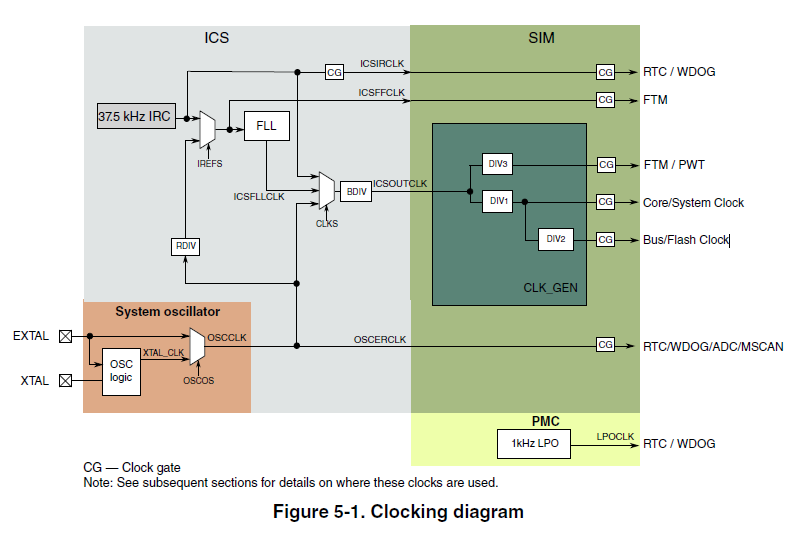

with 37.5khz internal clock, ICSOUT can generate 48Mhz output. ICSOUT=37.5k*1280=48Mhz

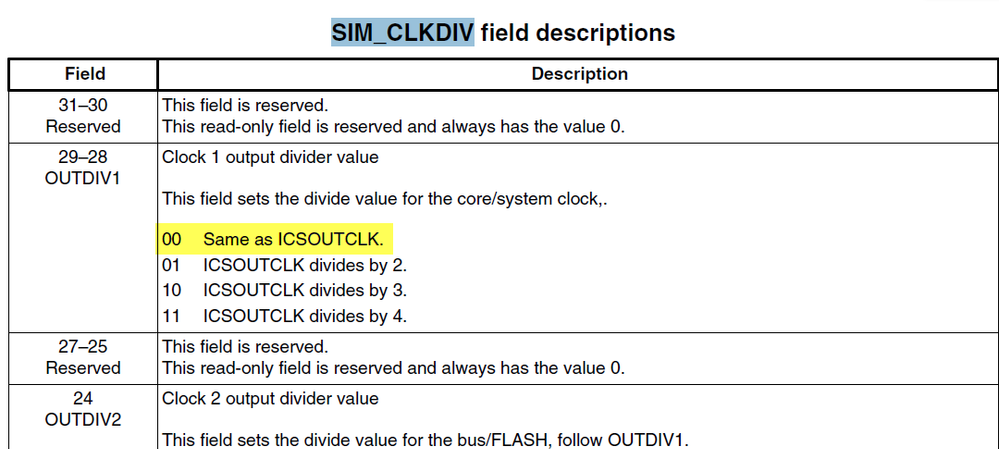

according to below clock diagram, we can set DIV1 as 1 to divide ICSOUT by 2, thus generated system/core clock is 48/2=24Mhz

thus we can set SIM_CLKDIV=0x11100000.

with above code, system/core clock is 48/2=24Mhz, bus clock=48/2/2=12Mhz. I made a demo under KDS3.0. see attached.

can this help you?

Have a great day,

Jennie Zhang

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you jennie.It provides me a basis for my understanding

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

you are welcome.

Jennie Zhang

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jennie,

Can you send that document to my mail id.It says I don't have access to it.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you Jennie :smileyhappy:

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Your code is a processor Expert one based on KDS IDE.Can you provide me a register level Example?

I have an example code for ICS module which works at 20Mhz.Can you suggest me what changes I have to do in it?

void Clk_Init()

{

ICS_C1|=ICS_C1_IRCLKEN_MASK; /* Enable the internal reference clock*/

ICS_C3= 0x90; /* Reference clock frequency = 31.25 KHz*/

while(!(ICS_S & ICS_S_LOCK_MASK)); /* Wait for PLL lock, now running at 40 MHz (1280 * 31.25Khz) */

ICS_C2|=ICS_C2_BDIV(1) ; /*BDIV=2, Bus clock = 20 MHz*/

ICS_S |= ICS_S_LOCK_MASK ; /* Clear Loss of lock sticky bit */

}

This is the standard Example given by KEA-128.

I want to make changes in it.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Vignesh,

in my first response, I set system/core clock by setting DIV1 in SIM module

your code sets system/core clock by setting BDIV in ICS module.

Carlos is correct, you can only remove ICS_C3= 0x90; to get 24M core clock if don't consider clock Trim.

with your code, in FEI mode, FLL output 37.5k*1280=48Mhz

with this code:

ICS_C2|=ICS_C2_BDIV(1) ; // BDIV=divide by 2

ICSOUTCLK = FLL output/2 = 48/2=24Mhz

thus with default SIM_CLKDIV value: DIV1=00, we can get system/core clock = ICSOUTCLK = 24Mhz

can this help you?

Have a great day,

Jennie Zhang

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Vignesh,

You can use the same initialization code but removing the following line:

ICS_C3= 0x90; /* Reference clock frequency = 31.25 KHz*/

This way the IRC frequency will be 37.5kHz, which is the factory trimmed frequency, and you will be able to achieve 48MHz as Jennie already mentioned.

ICSOUT=37.5k*1280=48Mhz

Hope it helps!

Best Regards,

Carlos Mendoza

Technical Support Engineer

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Carlo,

How do you say that 0x90 corresponds to 31.25 Khz IRC?

How to set values between 31.25 Khz to 39.0625 Khz???

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi carlos,

I made a small change to the code.After removing the Trim value.I removed the divider also.This is the code

void Clk_Init()

{

ICS_C1|=ICS_C1_IRCLKEN_MASK; /* Enable the internal reference clock*/

while(!(ICS_S & ICS_S_LOCK_MASK)); /* Wait for PLL lock, now running at 40 MHz (1280 * 31.25Khz) */

ICS_S |= ICS_S_LOCK_MASK ; /* Clear Loss of lock sticky bit */

}

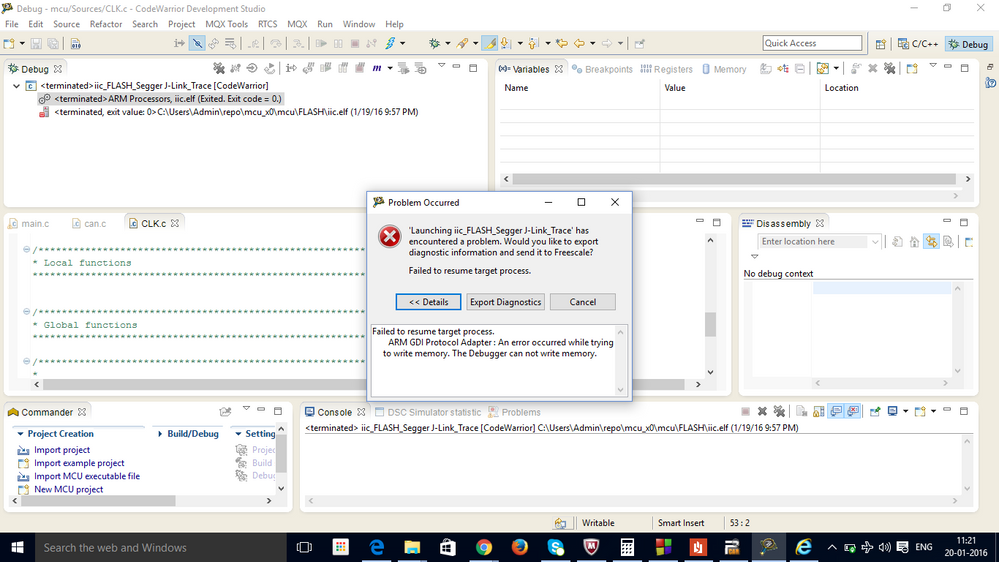

I found that the controller is not able to flash again after running this at this clock.

Can you tell me the reason???

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Vignesh,

I have tested the same code and the application is working as expected and I had no problem flashing the MCU after this.

Could you post a screenshot of the error you get?

Best Regards!

Carlos Mendoza

Technical Support Engineer

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

That means you ran the bus clock at 48 Mhz as mine and the MCU did not find any problem.I ran my MCU in debug mode with Segger(internally SWD).Did you run this at the same way.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Vignesh,

i just tested your code on my side there is no error.

normally the error you got is a target connect issue but not because of code itself. to fix it, please check:

1. if you use NXP demo board TPK-KEA128, if no external power supply provided, please make sure J13 connect 1-2

2. not use if the problem is because of your J-link firmware, please use attached JLink_OpenSDA_V2_1_2015-10-13.bin to update the TPK-KEA128 OpenSDA firmware.

3. attached is my testing project and video, I use KDS3.0. please refer.

can this help you?

Have a great day,

Jennie Zhang

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I want to know how to set the trim value to vary the IRC between 31.25 kHz to 39 Khz?

I also want to know why IRC can vary between that values only?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

there is one good article on this regard:

Yes, OSDA can trim the reference of internal clock source!

Jennie Zhang

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi jennie,

I tried accessing the aricle.It is saying unauthorized access.Can you send that article to my mail id?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

yes, sent. please check your email box.

Jennie Zhang

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Zhang,

The article which you shared me was awsome.

So what I want to understand is that

1)Is there any Formula or Calculation For Finding the ICS_C3 value without this work around???

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

different chip has slightly different internal status, external environment for example temperature also effects ICS_C3 setting values. So I don't think there is a Formular for that. We use the calculation method in the article as I pointed.

Hope this helps!

Jennie Zhang

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Zhang,

The Article you shared in the thread says that The value of ICS_C3 changes.

ICS_C3 was trimmed to value of

0x57 for 39.062kHz and

0x9B for 31.250kHz

But it did not Explain how 0x57 for 39.062 kHz and what will be the values for 0x60 or 0x70 ???

Can you Explain me how to choose the hex value for corresponding kHz?

For Example If suppose, I want to get 35 kHz what hex value should I choose for ICS_C3 register?