- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- Product Forums

- :

- Vybrid Processors

- :

- Re: Vybrid LPDDR2-configuration - IS43LD16640A

Vybrid LPDDR2-configuration - IS43LD16640A

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

We are currently attempting to configure an LPDDR2-chip (ISSI IS43LD16640A).

Seing as we currently work on a Linux host system, we have attempted to do the config manually, taking inspiration from the following threads:

VF5xx / Example of LPDDR2 Configuration

The threads mention errors in the reference manual and internal correspondence, and does not seem to give the answer that we are looking for.

After a few failed tries, we decided that we could use Processor Expert to help us configure the LPDDR2-chips. This too was unsuccessful.

This is very hard to debug, and pinpointing single issues is next to impossible. Are there any resources, other than the Processor Expert Validation Tool, that may help us in this process? Are there any helpful people out there who knows configure this chip?

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

We are marking this post as solved, due to the either low activity or any reply marked as correct.

If you have additional questions, please create a new post and reference to this closed post.

NXP Community!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Thomas,

one more think. I did not noticed if VDDref resistors and ZQ calib resistors are 1%.

/Jiri

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi jiri-b36968,

This part of the issue was just resolved.

As it turned out, the DRAM setup defined wrong address pin. The Vybrid Reference Manual Revisions 7 & 8 recommends DDRMC_CR73[APREBIT]=0xA for both DDR3 and LPDDR2. This assigns DDR_A10/CA10 as the address pin. However, the JEDEC standard specifies DDR_A0/CA0 as the address pin, thus the correct value should be: DDRMC_CR73[APREBIT]=0x0.

Please add a note for future revisions.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi jiri-b36968,

While on the topic of RM errors. Under DDRMC_CR126[UP_ERR_STAT], it states under Bit[0]:

1 = Error: PHY initialization violated maximum PHYUPD_INT (DDRMC_CR131) timing parameter.

However. DDRMC_CR131 is listed as "Reserved". This seems to be true for both revisions 7 & 8.

Could you clarify this?

/Tom

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Thomas,

thank you for notices.

CR131 is programmed 0, which disables timer between controller initiated update requests of PHY - so this error in CR126 never occurs.

/Jiri

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jiri,

We have prepared a tarball for you, but we cannot post it openly here on the forum. Please provide an alternative way for us to send this to you.

/Tom

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Tom,

preferably attach with password and send the password to my email in the profile

or send to my email box directly.

/Jiri

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jiri,

There is no email listed in your profile.

/Tom

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Thomas,

received. Going to check it.

Replies to your questions:

- The LPDDR2 JEDEC spec does not define this parameter.

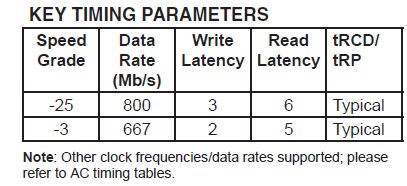

- FAST/TYPICAL/SLOW is the memory grade from manufacturer. From your memory datasheet - you should use typical values:

- for CR26 set it to all banks

- CR132 RDLAT_ADJ link is available to FAE only unfortunately. It discuss strong influence of this field on calibrations of read path.

/Jiri

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jiri,

We have addressed your answer, but still no cigar.

We found that CR41 must be set to 0x1, as mentioned here: Vybrid LPDDR2 Configuration . Also mentioned is that CR41 is listed as "Reserved" in RM. Even though the linked community thread pre-dates the new RM revision, there have been no corrections related to this field, or any of the other "Reserved-by-mistake" fields mentioned in this thread. These fields also seem to be missing from Processor Export, meaning it most likely won't help when configuring LPDDR2 DRAM.

I will keep posting as I (hopefully) progress.

/Tom

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Thomas,

sorry for that, but it suppress assertion of the signal which is not used.

Bit is DFI_INIT_START_INIT_DISABLE:

Disables the assertion of the dfi_init_start signal during DFI initialization. Set to 1 to disable the dfi_init_start signal initialization assertion.

For init we need just CR80 Bit [8] - The Memory Controller initialization has been completed.

/Jiri

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

jiri-b36968 can you continue checking this case?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jiri,

I am slowly working my way through the register settings, but until then here are the answers to your step-by-step questions:

Is DRAM controller initiated correctly? DDRMC_CR80 bit Bit[8]

The DDRMC_CR80[8] bit seems to be set.

Is CKE raised? logic high on CKE output.

The CKE seems to be at logic-high.

Can you see the DRAM clock? What is the frequency and jitter?

The DRAM clock does not seem to be running.

Can you measure shape of the signals? Need active probe for 2GHz or more.

We unfortunately do not have the equipment to measure this.

Can you describe the design? Do you follow DDR recommendations? Trace lengths matching, stacking?

The HW-engineer tell me that the design has been followed, including trace lengths matching and stacking.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Thomas,

That is strange. DRAM controller cannot be initiated without the clock. Please check IOMUXC_DDR_CLK.

Please check and if necessary clear clear bit in CR80 (by writing 1 into appropriate bit in CR81) before the start of DRAM controller. Check again.

/Jiri

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

My apologies. The clock seem to be running after all. There was an issue with our first measurement.