- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Configuring 16-line RGB interface of I.MX6D for 16-bit LCD display

Configuring 16-line RGB interface of I.MX6D for 16-bit LCD display

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Configuring 16-line RGB interface of I.MX6D for 16-bit LCD display

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi All,

We want to know the configure details for 16-line RGB interface of I.MX6D for 16-bit LCD display.

Going through the below community forum,

https://community.freescale.com/thread/327695

we understand the below settings are required to send the RGB565 data over the DISP_DAT0 - DISP0_DAT15 in addition to VSYNC, HSYNC, PCLK.

- Timing in mxc_lcdif.c:

static struct fb_videomode lcdif_modedb[] = {

{

"320x240", 60, 240, 320, KHZ2PICOS(25000), 5, 5, 2, 2, 5, 2,

FB_SYNC_CLK_LAT_FALL,

FB_VMODE_NONINTERLACED,

0,

},

//...

}

2. FB configuration in board-mx6dl_xxxx.c:

static struct fsl_mxc_lcd_platform_data lcdif_data = {

.ipu_id = 0,

.disp_id = 0,

.default_ifmt = IPU_PIX_FMT_RGB565,

};

//...

static struct ipuv3_fb_platform_data RIoTboard_fb_data[] = {

{

.disp_dev = "lcd",

.interface_pix_fmt = IPU_PIX_FMT_RGB565,

.mode_str = "320x240",

.default_bpp = 16,

.int_clk = false,

},

//...

}

3. Pin Muxing in board-mx6dl_xxxx.h:

/* DISPLAY */

MX6DL_PAD_DI0_DISP_CLK__IPU1_DI0_DISP_CLK,

MX6DL_PAD_DI0_PIN15__IPU1_DI0_PIN15, /* DE */

MX6DL_PAD_DI0_PIN2__IPU1_DI0_PIN2, /* HSync */

MX6DL_PAD_DI0_PIN3__IPU1_DI0_PIN3, /* VSync */

//MX6DL_PAD_DI0_PIN4__IPU1_DI0_PIN4, /* Contrast not connected*/

MX6DL_PAD_DISP0_DAT0__IPU1_DISP0_DAT_0,

MX6DL_PAD_DISP0_DAT1__IPU1_DISP0_DAT_1,

MX6DL_PAD_DISP0_DAT2__IPU1_DISP0_DAT_2,

MX6DL_PAD_DISP0_DAT3__IPU1_DISP0_DAT_3,

MX6DL_PAD_DISP0_DAT4__IPU1_DISP0_DAT_4,

MX6DL_PAD_DISP0_DAT5__IPU1_DISP0_DAT_5,

MX6DL_PAD_DISP0_DAT6__IPU1_DISP0_DAT_6,

MX6DL_PAD_DISP0_DAT7__IPU1_DISP0_DAT_7,

MX6DL_PAD_DISP0_DAT8__IPU1_DISP0_DAT_8,

MX6DL_PAD_DISP0_DAT9__IPU1_DISP0_DAT_9,

MX6DL_PAD_DISP0_DAT10__IPU1_DISP0_DAT_10,

MX6DL_PAD_DISP0_DAT11__IPU1_DISP0_DAT_11,

MX6DL_PAD_DISP0_DAT12__IPU1_DISP0_DAT_12,

MX6DL_PAD_DISP0_DAT13__IPU1_DISP0_DAT_13,

MX6DL_PAD_DISP0_DAT14__IPU1_DISP0_DAT_14,

MX6DL_PAD_DISP0_DAT15__IPU1_DISP0_DAT_15

Where,

DISP0_DAT0:DISP0_DAT4 - R0-R4

DISP0_DAT5:DISP0_DAT10 - G0-G5

DISP0_DAT11:DISP0_DAT15 - B0-B4

Please clarify if the above settings is enough to configure framebuffer (e.g. dev/fb0) as 320x240 16bpp (RGB565) and get the IPU to output the data 16-bits at a time.

Is there any other settings required to configure the internal DI format for data and commands for 16bits words such that the IPU driver outputs all LCD data in one clock over DISP0_DAT0:DISP0_DAT15.

Thanks & regards, Pramir

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Pramir

yes these settings are enough, in general process is well described in

sect.17.2 Adding Support for an LCD Panel i.MX53 System Development User’s Guide (rev.1, 3/2011)

http://www.freescale.com/files/32bit/doc/user_guide/MX53UG.pdf

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

HI igor,

thanks for your reply.

In the figure 17-2 Interface, it shows that you have connected 18-data lines with display.

Since my display has only 16-data lines, could you confirm the below connections with display,

DISP0_DAT0:DISP0_DAT4 - R0-R4

DISP0_DAT5:DISP0_DAT10 - G0-G5

DISP0_DAT11:DISP0_DAT15 - B0-B4

Thanks, Pramir

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Pramir

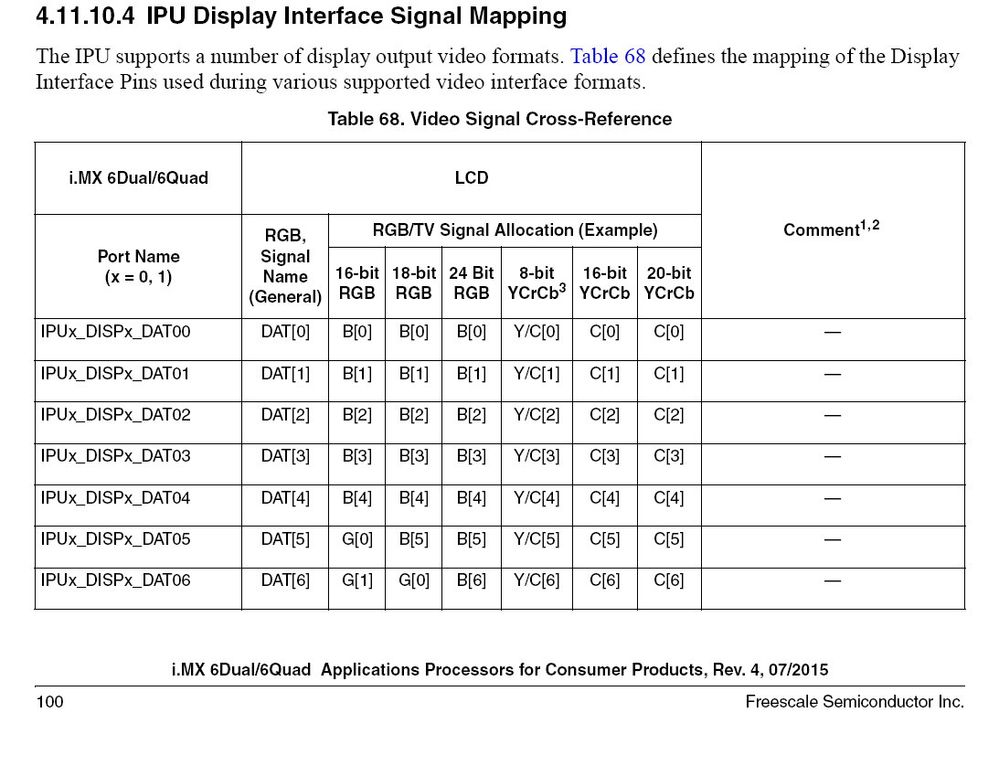

lcd mapping is given in datasheet

i.MX6DQ Datasheet (rev.4, 7/2015)

http://cache.freescale.com/files/32bit/doc/data_sheet/IMX6DQCEC.pdf

Best regards

igor