- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- Re: LMEM_PSCR register not existing in K65

LMEM_PSCR register not existing in K65

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I'm am trying to maximize flash execution performance (which is until now 30% lower than from internal SRAM with FMC Cache activated!).

AN4745 lists the following procedure on activating the LMEM cache:

1. Modify the cache region configuration in the LMEM_PCCRMR from the default values if desired.

2. Set the LMEM_PCCCR[INVW1 and INVW0] bits to configure the controller to invalidate both ways of the CODE bus

cache.

3. Set the LMEM_PCCCR[GO] bit to start the invalidate.

4. Wait for the LMEM_PCCCR[GO] bit to clear indicating the command has completed.

5. Enable the CODE bus cache by setting LMEM_PCCR[ENCACHE].

6. Set the LMEM_PSCCR[INVW1 and INVW0] bits to configure the controller to invalidate both ways of the system bus

cache.

7. Set the LMEM_PCCCR[GO] bit to start the invalidate.

8. Wait for the LMEM_PSCCR[GO] bit to clear indicating the command has completed.

9. Enable the system bus cache by setting LMEM_PSCR[ENCACHE].

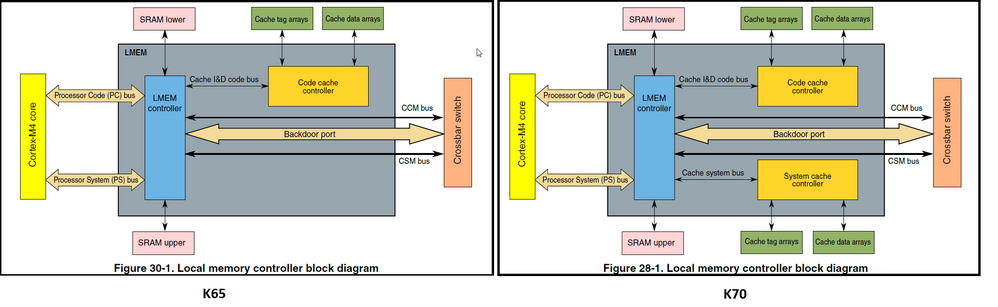

But unfortunately, I can't find any sign of existence for the registers LMEM_PSCR and LMEM_PSCCR in K65.

Am I missing something?

Edit:

Seems like these registers are only available in Kinetis K70 devices since only these have the SYSTEM cache controller.

What does this missing cache controller mean for the flashe execution performance of the K65 devices ?#

I also found out, that enabling the cache in some cases reduces the flash execution performance :smileysad: so simply enabling it may slow down the application.

Is there a special Application Note regarding cache best practices on freescale?

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Peter,

That's true. For K65 without the system cache, there will missing the LEME_PSCCR and LEME_PSCRMR registers as K70 has.

The Flash operation performance could be enhanced with FMC module, which feature also be described at AN4745 document.

The FMC cache and prefetch speculation buffer allow the FMC to respond to flash accesses with no added wait states in many cases. Any time the requested information is available in the cache or prefetch buffer, the FMC responds with no added wait states.

For the frequently accessed code or data in Flash range, it is a better option to to one of the SRAM blocks (preferrably SRAM_L).

Please let me know if you have more queries about FMC module and Kinetis Cache.

BTW: Unfortunately, so far there is no documents about best practices of Kinetis Cache.

Thank you for the attention.

Have a great day,

Ma Hui

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Peter,

That's true. For K65 without the system cache, there will missing the LEME_PSCCR and LEME_PSCRMR registers as K70 has.

The Flash operation performance could be enhanced with FMC module, which feature also be described at AN4745 document.

The FMC cache and prefetch speculation buffer allow the FMC to respond to flash accesses with no added wait states in many cases. Any time the requested information is available in the cache or prefetch buffer, the FMC responds with no added wait states.

For the frequently accessed code or data in Flash range, it is a better option to to one of the SRAM blocks (preferrably SRAM_L).

Please let me know if you have more queries about FMC module and Kinetis Cache.

BTW: Unfortunately, so far there is no documents about best practices of Kinetis Cache.

Thank you for the attention.

Have a great day,

Ma Hui

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for your answer which does NOT answer my most important question.

How can I acchieve the best flash execution performance on a K65 device?

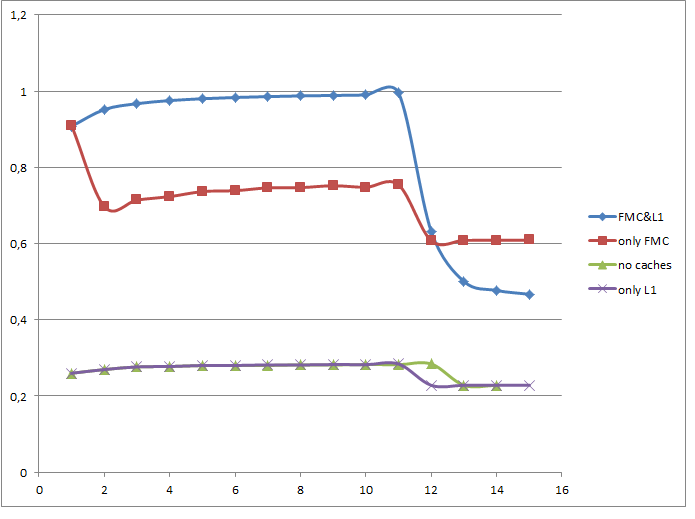

the following diagram shows the efficency (meaning looped instructions vs. needed cpu cycles) of flash code execution.

My concern is that from a specific code size, L1 cache introduces some serious disadvantages in execution performance.

the x- axis is not properly labeled. it should read from 100 looped instructions to 32k looped instructions.

maybe I'm going to open a new topic once I finish my examinations in comparison with a stm32 product which does not have L1 cache but also flash prefetch buffer.

hope to hear from you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Peter,

Our Kinetis product expert supports the same issue at thread: low flash performance on K6x , so I think we could close this thread now.

Thank you for the attention.

best regards,

Ma Hui