- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- Product Forums

- :

- Vybrid Processors

- :

- Query on PDB configuration for hardware tigger support

Query on PDB configuration for hardware tigger support

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Currently working on implementing hardware gpio trigger support in Linux using the IIO subsystem for the Vybrid ADC driver. Have got a working implementation ready, but, there are few things which are currently not clear to me on reading the Vybrid TRM when it comes to using multiple channels and my trial and error approach has not cleared my understanding.

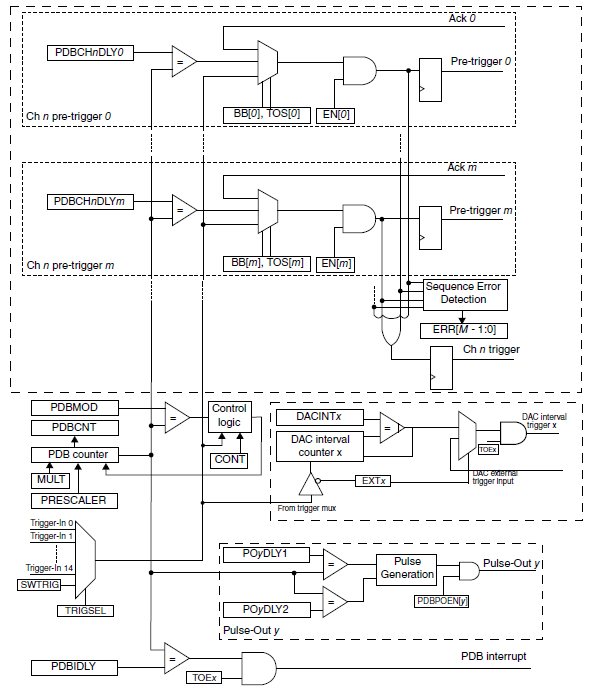

Trigger support for ADC requires configuration of the Programmable Delay Block peripheral. In the PDB block, there is a Channel n Control Register 1 in which there is the Pre Trigger output select and Pre trigger enable bit fields. There are two valid bit fields, however there configuration is currently not clear to me.

Is it possible to configure the PDB block for triggering and allow sampling of multiple channels? From the Page 1747 of the TRM which describes the register and the corresponding functional description on 1750, this would seem possible, however trying to configure the PDB currently gives me sequencing errors. The operations I currently perform are as follows

1. Set the bit 0 and 1 of the TOS and EN field of CH0C1 register

2. Set ADC_HC0 to one channel from ADC0 and ADC_HC1 to another channel from ADC0. For my case this is channel 8 and 9 with the ADC0 block.

3. Set a delay with the CH0DLY0 and CH0DLY1 registers.

4. Finally set PDBEIE, PDBEN and LDOK

This immediately raised the PDB sequencing error interrupt handler which I have configured when the hardware trigger is given with the GPIO. So my configuration seems wrong. What is the correct way to configure the PDB for multiple channels? From what I understand atleast two simultaneous channel readings should be possible and from what I read on two other posts which I found in the community, it should be doable?

Can someone clarify the PDB configuration to me for the above use case?

Also the so called back to back operation description does not help much, nor the one given on Page 1747 or the diagram on Page 146 of the TRM. Can someone shed some light on this as well?

Thanks & Regards,

Sanchayan Maity.

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

We are marking this post as solved, due to the either low activity or any reply marked as correct.

If you have additional questions, please create a new post and reference to this closed post.

NXP Community!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

We are marking this post as solved, due to the either low activity or any reply marked as correct.

If you have additional questions, please create a new post and reference to this closed post.

NXP Community!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Sanchayan,

Unfortunately, we do not have any examples for setting the PDB registers to allow sampling multiple channels. The Freescale Vybrid team may have some example configurations of this. If you can share your code modifications, we can review as well.

Thanks,

Timesys Support

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Alright. I am attaching the patches. These are not yet send to mainline as though I have GPIO trigger support now, I also intend to add continous sampling perhaps with software triggers and also DMA eventually.

The patch will apply cleanly only after the following patches are applied which take care of major clocking and sampling time bug fixes in the vf610_adc driver.

http://lkml.iu.edu/hypermail/linux/kernel/1503.3/00222.html

http://lkml.iu.edu/hypermail/linux/kernel/1505.3/02043.html

https://lkml.org/lkml/2015/6/24/97

Implementing the said functionality itself in the driver is not a question here, that we can do. The main query is with regards to PDB configuration concerning three points atleast.

1. Sampling multiple channels. There are two bits in registers like PDB_CHnC1. Exactly how they contribute to multiple channels is not clear. If I enable the two bits in both registers for fields like BB and TOS does that imply, four channels can be used in total?. As such in the ADC block only has ADC0_HC0 and ADC0_HC1 and so only two ADC channels can be specified one for ADC0 and one for ADC1 from what I can understand.

2. Continous Sampling. I guess this is to an extent clear to me however I did still like to have any inputs on this if possible. This should be doable through the continous mode enable and the counter/modulus register, hopefully straightforward.

Addendum: Continous sampling is working nicely.

3. The back to back operation which PDB_CHnC1 register mentions and also section 38.4.1.

Regards,

Sanchayan.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

The BB bit enables the back-to-back operation. if you refer to the below diagram:

You will notice that you have 3 possible options to enable the pre-trigger. When back to back is enabled the Ack signal that comes from the ADC_COCO triggers the pre-trigger signal. [BB = 1]. In this mode, when an ADC conversion is done, this trigger the other PDB channel which starts a new ADC conversion from other ADC module and channel.

Other mode is to bypass the channel. In this mode the signal selected by the TRIGSEL feeds the pre-trigger.

Or the pre-trigger may be fed by comparing the PDB counter with the PDBCHnDLYm.

Vybrid features 2 ADC modules ADC0 and ADC1. Each module has 2 set of control registers that you can use to sample 2 different channels, but not at the same time. This is because the ADC module has only 1 SAR unit.

All this means that with 2 ADC modules, you can only sample 2 ADC channels at the same time (one channel per ADC module).

But with the use of the second set of control registers and the PDB you can prepare the next conversion, so you will sample other 2 different channels when the first 2 are done.

Best Regards,

Alejandro

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Alejandro,

Thanks for the reply though late. I already had a working driver last week with hardware gpio triggers, software trigger, continuous sampling and back to back trigger mode supported.

However, as to whether two or four channels can be simulatenously sampled was not clear. Your input that each module has only one SAR unit throws some light on the matter.

From my own observations, with MOD_PERIOD as 0xFFFF, CH0_DLY as 0x07FF, CH1_DLY as 0xFFFF I can sample two channels one after the other from the same module ADC0 or ADC1 "OR" sample one channel from ADC0 and one from ADC1. Trying to configure two channels in both block to sample four channels does not seem to work. (It would have been nice if there was some more information on configuring the delays for the channels with respect to effect of/on different parameters except for just the peripheral clock cycle formula on Pg. 1751 of TRM, I guess I would have to eventually make them dynamic properly perhaps)

However the IIO trigger code somehow gives me the illusion of two channels from the same or different module being sampled simultaneously.

Regards,

Sanchayan.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

At the end each ADC module can sample one channel at the time. If you have 2 ADCs you can sample just 2 channels at the same time (using ADC0 and ADC1).

As you know each PDB channel is associated with one ADC module.

According to your comments above you used CH1_DLY and CH0_DLY, it seems that you used one pre-trigger for each PDB channel. But please check that you have PDB_CHnDLY0 and PDB_CHnDLY1, this means that you can trigger an ADC module and use ADC0_HC0 first and then ADC0_HC1 with PDB_CH0DLY0 and PDB_CH0DLY1 respectively.

Best Regards,

Alejandro

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Yes right. I typed it wrongly. PDB_CH0DLY and PDB_CH1DLY are used with 0x07FF and 0xFFFF respectively. However I cannot get two channels from the same block ADCx to reliably work. I keep getting PDB sequencing errors.

I even tried to dynamically set them based on the actual ADC cycles calculated from the ADC clock rate and sample rate. So if CH0DLY is adck_cycles, CH1DLY is 10 * adck_cycles. The prescaler divider and multiplier are also set accordingly. PDB clock is around 8 times the ADC clock rate so I set prescaler divisor to 16 and multiplier to 1.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yes, you have to make sure that the PDB counts are enough so the ADC conversion finishes.

Have you tried to change the external hardware trigger select when one conversion finishes?

So a different external hardware trigger is used:

From RM:

When the conversion is completed, the result is placed in the data registers associated

with the external hardware trigger received (active trigger selects ADC_Rn).

Best Regards,

Alejandro

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Yes, you have to make sure that the PDB counts are enough so the ADC conversion finishes.

Yes. And I have tried different values for both CH0DLY0 and CH0DLY1 from 0xA to 0xFFFF. Cannot find a value for both which works for all frequencies and both VF5xx and VF6xx.

Have you tried to change the external hardware trigger select when one conversion finishes? So a different external hardware trigger is used:

I did not understand this. A different hardware trigger select when once conversion finishes?

From RM:

When the conversion is completed, the result is placed in the data registers associated with the external hardware trigger received (active trigger selects ADC_Rn).

You are referring to the Note and paragraph at the end of section 37.8.4 I see. From what I understand, it implies that only particular external trigger should be used at a time. If this is what you are asking then yes, only one external trigger is used at a time for conversion. If I am using software trigger with continuous sampling, then trigger setting is not changed to hardware trigger while a particular conversion setting is in place for this.

In section 38.4.1, 6th paragraph goes like this

When a pre-trigger from a PDB channel n is asserted, the associated lock of the pre-trigger becomes active. The associated lock is released by the rising edge of the corresponding ADCnSC1[COCO]; the ADCnSC1[COCO] should be cleared after the conversion result is read, so that the next rising edge of ADCnSC1[COCO] can be generated to clear the lock later. The lock becomes inactive when:

• the rising edge of corresponding ADCnSC1[COCO] occurs,

• or the corresponding PDB pre-trigger is disabled,

• or the PDB is disabled

The channel n trigger output is suppressed when any of the locks of the pre-triggers in channel n is active. If a new pre-trigger m asserts when there is active lock in the PDB channel n, then a register flag bit CHnS[ERR[m]] (associated with the pre-trigger m) is set. If SC[PDBEIE] is set, then the sequence error interrupt is generated. A sequence error typically happens because the delay m is set too short and the pre-trigger m asserts

before the previously triggered ADC conversion finishes.

The last line above is quite understandable and expected. The lock thing is not clear however. I do not see ADCnSC1 registers either. The COCO bits are in ADCx_HS. Which lock and does ADCnSC1 refer to ADCx_HS? As such I clear ADCx_HS[COCOx] in the IRQ handler, so if Channel 0 was pretriggered and COCO0 was found to be set, after reading from ADC_R0 I clear ADCx_HS[COCO0].

Regards,

Sanchayan.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

alejandrolozano can you continue with the follow up?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

reminder

alejandrolozano can you continue with the follow up?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Sorry for the delay. Let me try to create a simple project. I will get back as soon as I get it done.

Alejandro

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

alejandrolozano do you have an update?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

reminder

alejandrolozano do you have an update?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I have not had time to finish the project. I will get it done this week.

/Alejandro

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

alejandrolozano any progress?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Sorry for the delay,

I just tried the below simple code and debugging with IAR I notice that both ADC_R0 and ARC_R1 are working with the PDB:

Please refer to it and let me know if that helps.

int main()

{

printf("Hello World!\n");

/*Enable ADC and PDB clocks*/

/*PDB setup Clocks*/

CCM->CCGR1 |= CCM_CCGR1_CG6(3);

/*ADC0 Clock*/

CCM->CCGR1 |= CCM_CCGR1_CG11(3);

/*Select one External Hardware Trigger*/

SRC->MISC1 &= ~(SRC_MISC1_MISC1_29_MASK);

SRC->MISC1 &= ~(SRC_MISC1_MISC1_28_MASK);//|= (SRC_MISC1_MISC1_28_MASK);

PDB->SC = PDB_SC_CONT_MASK // Contintuous, rather than one-shot, mode

| PDB_SC_PDBEN_MASK // PDB enabled

| PDB_SC_PRESCALER(0x5) // Slow down the period of the PDB for testing

| PDB_SC_TRGSEL(0xf) // Trigger source is Software Trigger to be invoked in this file

| PDB_SC_MULT(2); // Multiplication factor 20 for the prescale divider for the counter clock

PDB->IDLY = 0x0000;

PDB->MOD = 0XFFFF;

// channel 0 pretrigger 0 and 1 enabled and delayed

PDB->CH[0].C1 = PDB_C1_EN(0x01)

| PDB_C1_TOS(0x01)

| PDB_C1_EN(0x02)

| PDB_C1_TOS(0x02) ;

PDB->CH[0].DLY[0] = ADC0_DLYA ;

PDB->CH[0].DLY[1] = ADC0_DLYB ;

PDB->SC = PDB_SC_CONT_MASK // Contintuous, rather than one-shot, mode

| PDB_SC_PDBEN_MASK // PDB enabled

| PDB_SC_PDBIE_MASK // PDB Interrupt Enable

| PDB_SC_PRESCALER(0x5) // Slow down the period of the PDB for testing

| PDB_SC_TRGSEL(0xf) // Trigger source is Software Trigger to be invoked in this file

| PDB_SC_MULT(2) // Multiplication factor 20 for the prescale divider for the counter clock

| PDB_SC_LDOK_MASK; // Need to ok the loading or it will not load certain regsiters!

// the software trigger, PDB_SC_SWTRIG_MASK is not triggered at this time.

/*Enable Hardware Trigger*/

ADC0->CFG |= ADC_CFG_ADTRG_MASK;

/**/

ADC0->HC[0] = ADC0_CHANA;

ADC0->HC[1] = ADC0_CHANB;

PDB->SC |= PDB_SC_SWTRIG_MASK ;

for(;;)

{

while(!(ADC0->HS & (ADC_HS_COCO0_MASK)));

asm("nop");

while(!(ADC0->HS & (ADC_HS_COCO1_MASK)));

asm("nop");

}

return 0;

}

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Thank you for sharing your configuration. Sorry for the delay in reply as I got tied up with other things. Will try giving that a respin with your settings after cross checking.

Can you share the ADC0_DLYA and ADC0_DLYB values?

Thanks.

- Sanchayan.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

cyborgnegotiator can you share your comments?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

alejandrolozano are you able to help here?