- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- Unique Firmware for Kinetis MK60DN and MK60DX

Unique Firmware for Kinetis MK60DN and MK60DX

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I'm writing a firmware for Kinetis MK60DN256ZVLL10, but I want to adapt it for MCU MK60DX256VLL10. It is possible?

(I follow this post: https://community.freescale.com/thread/328325 )

I know that these MCUs have a different silicon version.

To get the silicon version of each MCU, I used this code:

switch((SIM_SDID & SIM_SDID_REVID(0xF))>>SIM_SDID_REVID_SHIFT)

{

case 0x0:

printf("Silicon rev 1.0\n");

break;

case 0x1:

printf("Silicon rev 1.1\n");

break;

case 0x2:

printf("Silicon rev 1.2\n");

break;

case 0x3:

printf("Silicon rev 1.4\n");

break;

case 0x7:

printf("Silicon rev 1.8\n");

break;

case 0xA:

printf("Silicon rev 2.2\n");

break;

case 0xC:

printf("Silicon rev 2.4\n");

break;

These are the results:

MK60DN256ZVLL10 --> Silicon Version: Rev. 1.4

MK60DX256VLL10 --> Silicon Version Rev. 2.2.

Unfortunately I can't found any datasheet, application note, ecc about the PK60DX256VLL10, thus I don' know the difference between these MCU.

What can I do to load my firmware into MK60DX256VLL10 ?

Thanks.

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

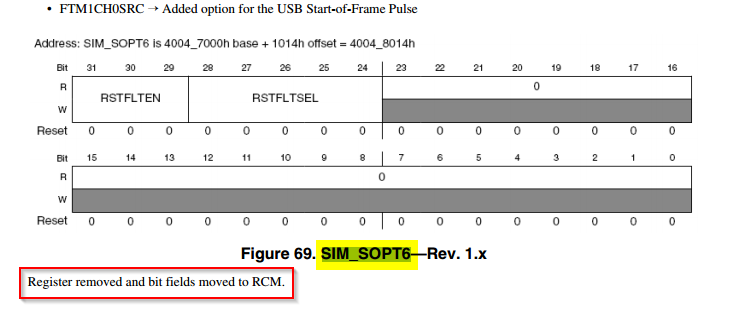

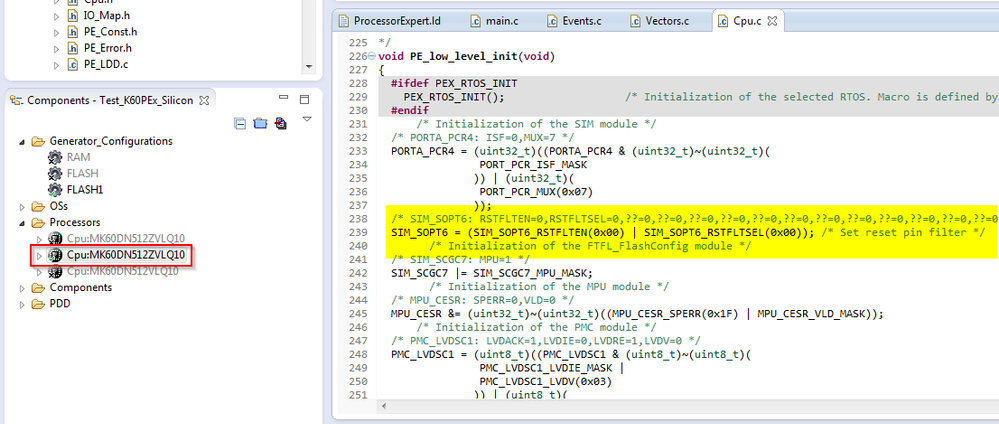

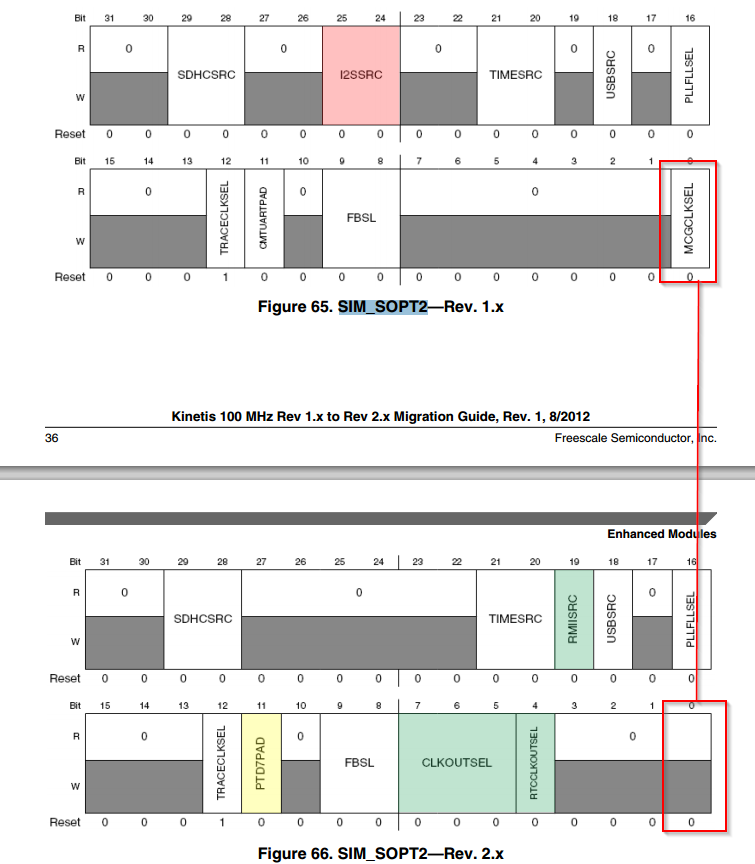

Just before the access to SIM_SCGC7, you are accessing SIM_SOPT6, which does no longer exist on Rev 2.x silicon.

You can get more detailed information between silicon rev 1.x (xN30D) and silicon rev 2.x (xN22D) in the following Application note:

http://cache.freescale.com/files/32bit/doc/app_note/AN4445.pdf

This is the code that is causing the hard fault:

SIM_SOPT6 = (SIM_SOPT6_RSTFLTEN(0x00) | SIM_SOPT6_RSTFLTSEL(0x00)); /* Set reset pin filter */

/* Initialization of the FTFL_FlashConfig module */

/* SIM_SCGC7: MPU=1 */

SIM_SCGC7 |= SIM_SCGC7_MPU_MASK;

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The only important difference between the 2 parts is the amount of flash ROM and Flex NVM available. The N256 version has 256K of Flash and no flex NVM functionality. The X256 has 512K of flash and the Flex NVM functionality. Your program will work exactly the same on both MCUs, If your application doesn't use flex NVM and is less than 256K in size. The only other differences in the parts should be different errata in effect. Both parts have the same data sheets.

You should be able to load the same program on both parts and have it work. If it doesn't you will need to look at the errata for each mask run.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for the reply Norm,

in this post https://community.freescale.com/thread/328325 the author suggests to disable all Flash caching & Speculation. Is it correct?

I created my project for K60DN256 with Process Expert, but when I debug the same code with K60DX256, I get an error in void PE_low_level_init(void) function.

After the execution of:

/* SIM_SCGC7: MPU=1 */

SIM_SCGC7 |= SIM_SCGC7_MPU_MASK;

the debug stuck in this function:

PE_ISR(Cpu_Interrupt)

{

/* This code can be changed using the CPU component property "Build Options / Unhandled int code" */

PE_DEBUGHALT();

}

I think that this problem is due to silicon revision. K60DN256 has Rev. 1.x and K60DX256 has Rev. 2.x.

Any suggestions?

Could you help me?

Thanks in advance

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

It is advisable to disable cache and speculation on Rev.1 K60s but is is not necessary on Rev.2 parts.

There are no differences between the MPU clock gating and control on any of the parts or revisions. Therefore there should be no problems with access to SIM_SCGC7 - the MPU bit is set at reset anyway. Therefore it is not logical that the instruction causes the interrupt to take place - I would check for other code that was executed just before this instruction to see whether a probem there is misleading to believe that it is the SIM_SCGC7 access.

Regards

Mark

Kinetis: µTasker Kinetis support

K60: µTasker Kinetis TWR-K60N512 support / µTasker Kinetis TWR-K60D100M support / µTasker Kinetis TWR-K60F120M support

For the complete "out-of-the-box" Kinetis experience and faster time to market

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Mark, thanks for the reply.

This is my CPU.c configuration file, where you can see the instruction above SIM_SCGC7 init.

/* ###################################################################

** THIS COMPONENT MODULE IS GENERATED BY THE TOOL. DO NOT MODIFY IT.

** Filename : Cpu.c

** Project : ProcessorExpert

** Processor : MK60DN256ZVLL10

** Component : MK60N512LL100

** Version : Component 01.001, Driver 01.04, CPU db: 3.00.001

** Datasheet : K60P144M100SF2RM, Rev. 5, 8 May 2011

** Compiler : CodeWarrior ARM C Compiler

** Date/Time : 2014-06-30, 15:03, # CodeGen: 37

** Abstract :

**

** Settings :

**

** Contents :

** No public methods

**

** Copyright : 1997 - 2013 Freescale Semiconductor, Inc. All Rights Reserved.

** SOURCE DISTRIBUTION PERMISSIBLE as directed in End User License Agreement.

**

** http : www.freescale.com

** mail : support@freescale.com

** ###################################################################*/

/*!

** @file Cpu.c

** @version 01.04

** @brief

**

*/

/*!

** @addtogroup Cpu_module Cpu module documentation

** @{

*/

/* MODULE Cpu. */

/* {Default RTOS Adapter} No RTOS includes */

#include "PTB.h"

#include "PTC.h"

#include "PTD.h"

#include "SPI1.h"

#include "usb_device.h"

#include "USB_LDD.h"

#include "usb_cdc.h"

#include "SysTick.h"

#include "UART0.h"

#include "PTE.h"

#include "SPI2.h"

#include "TIMER0.h"

#include "PE_Types.h"

#include "PE_Error.h"

#include "PE_Const.h"

#include "IO_Map.h"

#include "Events.h"

#include "Cpu.h"

#ifdef __cplusplus

extern "C" {

#endif

/* Global variables */

volatile uint8_t SR_reg; /* Current value of the FAULTMASK register */

volatile uint8_t SR_lock = 0x00U; /* Lock */

/*

** ===================================================================

** Method : Cpu_SetBASEPRI (component MK60N512LL100)

**

** Description :

** This method sets the BASEPRI core register.

** This method is internal. It is used by Processor Expert only.

** ===================================================================

*/

void Cpu_SetBASEPRI(register uint32_t Level);

/*

** ===================================================================

** Method : Cpu_INT_NMIInterrupt (component MK60N512LL100)

**

** Description :

** This ISR services the Non Maskable Interrupt interrupt.

** This method is internal. It is used by Processor Expert only.

** ===================================================================

*/

PE_ISR(Cpu_INT_NMIInterrupt)

{

Cpu_OnNMIINT();

}

/*

** ===================================================================

** Method : Cpu_Cpu_Interrupt (component MK60N512LL100)

**

** Description :

** This ISR services an unused interrupt/exception vector.

** This method is internal. It is used by Processor Expert only.

** ===================================================================

*/

PE_ISR(Cpu_Interrupt)

{

/* This code can be changed using the CPU component property "Build Options / Unhandled int code" */

PE_DEBUGHALT();

}

/*** !!! Here you can place your own code using property "User data declarations" on the build options tab. !!! ***/

/*lint -esym(765,__init_hardware) Disable MISRA rule (8.10) checking for symbols (__init_hardware). The function is linked to the EWL library */

/*lint -esym(765,Cpu_Interrupt) Disable MISRA rule (8.10) checking for symbols (Cpu_Interrupt). */

void __init_hardware(void)

{

/*** !!! Here you can place your own code before PE initialization using property "User code before PE initialization" on the build options tab. !!! ***/

/*** ### MK60DN256ZVLL10 "Cpu" init code ... ***/

/*** PE initialization code after reset ***/

SCB_VTOR = (uint32_t)(&__vect_table); /* Set the interrupt vector table position */

/* SIM_SCGC6: RTC=1 */

SIM_SCGC6 |= SIM_SCGC6_RTC_MASK;

if ((RTC_CR & RTC_CR_OSCE_MASK) == 0u) { /* Only if the OSCILLATOR is not already enabled */

/* RTC_CR: SC2P=0,SC4P=0,SC8P=0,SC16P=0 */

RTC_CR &= (uint32_t)~(uint32_t)(

RTC_CR_SC2P_MASK |

RTC_CR_SC4P_MASK |

RTC_CR_SC8P_MASK |

RTC_CR_SC16P_MASK

);

/* RTC_CR: OSCE=1 */

RTC_CR |= RTC_CR_OSCE_MASK;

/* RTC_CR: CLKO=0 */

RTC_CR &= (uint32_t)~(uint32_t)(RTC_CR_CLKO_MASK);

}

/* Disable the WDOG module */

/* WDOG_UNLOCK: WDOGUNLOCK=0xC520 */

WDOG_UNLOCK = WDOG_UNLOCK_WDOGUNLOCK(0xC520); /* Key 1 */

/* WDOG_UNLOCK: WDOGUNLOCK=0xD928 */

WDOG_UNLOCK = WDOG_UNLOCK_WDOGUNLOCK(0xD928); /* Key 2 */

/* WDOG_STCTRLH: ??=0,DISTESTWDOG=0,BYTESEL=0,TESTSEL=0,TESTWDOG=0,??=0,STNDBYEN=1,WAITEN=1,STOPEN=1,DBGEN=0,ALLOWUPDATE=1,WINEN=0,IRQRSTEN=0,CLKSRC=1,WDOGEN=0 */

WDOG_STCTRLH = WDOG_STCTRLH_BYTESEL(0x00) |

WDOG_STCTRLH_STNDBYEN_MASK |

WDOG_STCTRLH_WAITEN_MASK |

WDOG_STCTRLH_STOPEN_MASK |

WDOG_STCTRLH_ALLOWUPDATE_MASK |

WDOG_STCTRLH_CLKSRC_MASK;

/* System clock initialization */

/* SIM_CLKDIV1: OUTDIV1=0,OUTDIV2=1,OUTDIV3=3,OUTDIV4=3,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0 */

SIM_CLKDIV1 = SIM_CLKDIV1_OUTDIV1(0x00) |

SIM_CLKDIV1_OUTDIV2(0x01) |

SIM_CLKDIV1_OUTDIV3(0x03) |

SIM_CLKDIV1_OUTDIV4(0x03); /* Set the system prescalers to safe value */

/* SIM_SCGC5: PORTE=1,PORTD=1,PORTC=1,PORTB=1,PORTA=1 */

SIM_SCGC5 |= SIM_SCGC5_PORTE_MASK |

SIM_SCGC5_PORTD_MASK |

SIM_SCGC5_PORTC_MASK |

SIM_SCGC5_PORTB_MASK |

SIM_SCGC5_PORTA_MASK; /* Enable clock gate for ports to enable pin routing */

/* SIM_CLKDIV1: OUTDIV1=0,OUTDIV2=0,OUTDIV3=1,OUTDIV4=1,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0 */

SIM_CLKDIV1 = SIM_CLKDIV1_OUTDIV1(0x00) |

SIM_CLKDIV1_OUTDIV2(0x00) |

SIM_CLKDIV1_OUTDIV3(0x01) |

SIM_CLKDIV1_OUTDIV4(0x01); /* Update system prescalers */

/* SIM_CLKDIV2: USBDIV=0,USBFRAC=0 */

SIM_CLKDIV2 &= (uint32_t)~(uint32_t)(

SIM_CLKDIV2_USBDIV(0x07) |

SIM_CLKDIV2_USBFRAC_MASK

); /* Update USB clock prescalers */

/* SIM_SOPT2: PLLFLLSEL=1 */

SIM_SOPT2 |= SIM_SOPT2_PLLFLLSEL_MASK; /* Select PLL as a clock source for various peripherals */

/* SIM_SOPT1: OSC32KSEL=0 */

SIM_SOPT1 &= (uint32_t)~(uint32_t)(SIM_SOPT1_OSC32KSEL_MASK); /* System oscillator drives 32 kHz clock for various peripherals */

/* PORTA_PCR18: ISF=0,MUX=0 */

PORTA_PCR18 &= (uint32_t)~(uint32_t)((PORT_PCR_ISF_MASK | PORT_PCR_MUX(0x07)));

/* Switch to FBE Mode */

/* MCG_C2: ??=0,??=0,RANGE=2,HGO=0,EREFS=0,LP=0,IRCS=0 */

MCG_C2 = MCG_C2_RANGE(0x02);

/* OSC_CR: ERCLKEN=1,??=0,EREFSTEN=0,??=0,SC2P=0,SC4P=0,SC8P=0,SC16P=0 */

OSC_CR = OSC_CR_ERCLKEN_MASK;

/* SIM_SOPT2: MCGCLKSEL=0 */

SIM_SOPT2 &= (uint32_t)~(uint32_t)(SIM_SOPT2_MCGCLKSEL_MASK);

/* MCG_C1: CLKS=2,FRDIV=5,IREFS=0,IRCLKEN=1,IREFSTEN=0 */

MCG_C1 = (MCG_C1_CLKS(0x02) | MCG_C1_FRDIV(0x05) | MCG_C1_IRCLKEN_MASK);

/* MCG_C4: DMX32=0,DRST_DRS=0 */

MCG_C4 &= (uint8_t)~(uint8_t)((MCG_C4_DMX32_MASK | MCG_C4_DRST_DRS(0x03)));

/* MCG_C5: ??=0,PLLCLKEN=0,PLLSTEN=0,PRDIV=0x18 */

MCG_C5 = MCG_C5_PRDIV(0x18);

/* MCG_C6: LOLIE=0,PLLS=0,CME=0,VDIV=0 */

MCG_C6 = MCG_C6_VDIV(0x00);

while((MCG_S & MCG_S_IREFST_MASK) != 0x00U) { /* Check that the source of the FLL reference clock is the external reference clock. */

}

while((MCG_S & 0x0CU) != 0x08U) { /* Wait until external reference clock is selected as MCG output */

}

/* Switch to PBE Mode */

/* MCG_C6: LOLIE=0,PLLS=1,CME=0,VDIV=0 */

MCG_C6 = (MCG_C6_PLLS_MASK | MCG_C6_VDIV(0x00));

while((MCG_S & 0x0CU) != 0x08U) { /* Wait until external reference clock is selected as MCG output */

}

while((MCG_S & MCG_S_LOCK_MASK) == 0x00U) { /* Wait until locked */

}

/* Switch to PEE Mode */

/* MCG_C1: CLKS=0,FRDIV=5,IREFS=0,IRCLKEN=1,IREFSTEN=0 */

MCG_C1 = (MCG_C1_CLKS(0x00) | MCG_C1_FRDIV(0x05) | MCG_C1_IRCLKEN_MASK);

while((MCG_S & 0x0CU) != 0x0CU) { /* Wait until output of the PLL is selected */

}

/*** End of PE initialization code after reset ***/

/*** !!! Here you can place your own code after PE initialization using property "User code after PE initialization" on the build options tab. !!! ***/

}

/*

** ===================================================================

** Method : Cpu_SetBASEPRI (component MK60N512LL100)

**

** Description :

** This method sets the BASEPRI core register.

** This method is internal. It is used by Processor Expert only.

** ===================================================================

*/

/*lint -save -e586 -e950 Disable MISRA rule (2.1,1.1) checking. */

#ifdef _lint

#define Cpu_SetBASEPRI(Level) /* empty */

#else

asm void Cpu_SetBASEPRI(register uint32_t Level) {

MSR BASEPRI,R0;

MOV PC,LR

}

#endif

/*lint -restore Enable MISRA rule (2.1,1.1) checking. */

/*

** ===================================================================

** Method : PE_low_level_init (component MK60N512LL100)

**

** Description :

** Initializes beans and provides common register initialization.

** The method is called automatically as a part of the

** application initialization code.

** This method is internal. It is used by Processor Expert only.

** ===================================================================

*/

void PE_low_level_init(void)

{

#ifdef PEX_RTOS_INIT

PEX_RTOS_INIT(); /* Initialization of the selected RTOS. Macro is defined by the RTOS component. */

#endif

/* Initialization of the SIM module */

/* PORTA_PCR4: ISF=0,MUX=7 */

PORTA_PCR4 = (uint32_t)((PORTA_PCR4 & (uint32_t)~(uint32_t)(

PORT_PCR_ISF_MASK

)) | (uint32_t)(

PORT_PCR_MUX(0x07)

));

/* SIM_SOPT6: RSTFLTEN=0,RSTFLTSEL=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0 */

SIM_SOPT6 = (SIM_SOPT6_RSTFLTEN(0x00) | SIM_SOPT6_RSTFLTSEL(0x00)); /* Set reset pin filter */

/* Initialization of the FTFL_FlashConfig module */

/* SIM_SCGC7: MPU=1 */

SIM_SCGC7 |= SIM_SCGC7_MPU_MASK;

/* Initialization of the MPU module */

/* MPU_CESR: SPERR=0,VLD=0 */

MPU_CESR &= (uint32_t)~(uint32_t)((MPU_CESR_SPERR(0x1F) | MPU_CESR_VLD_MASK));

/* Initialization of the PMC module */

/* PMC_LVDSC1: LVDACK=1,LVDIE=0,LVDRE=1,LVDV=0 */

PMC_LVDSC1 = (uint8_t)((PMC_LVDSC1 & (uint8_t)~(uint8_t)(

PMC_LVDSC1_LVDIE_MASK |

PMC_LVDSC1_LVDV(0x03)

)) | (uint8_t)(

PMC_LVDSC1_LVDACK_MASK |

PMC_LVDSC1_LVDRE_MASK

));

/* PMC_LVDSC2: LVWACK=1,LVWIE=0,LVWV=0 */

PMC_LVDSC2 = (uint8_t)((PMC_LVDSC2 & (uint8_t)~(uint8_t)(

PMC_LVDSC2_LVWIE_MASK |

PMC_LVDSC2_LVWV(0x03)

)) | (uint8_t)(

PMC_LVDSC2_LVWACK_MASK

));

/* PMC_REGSC: TRAMPO=0,??=0,BGBE=0 */

PMC_REGSC &= (uint8_t)~(uint8_t)(

PMC_REGSC_TRAMPO_MASK |

PMC_REGSC_BGBE_MASK |

0x02U

);

/* MC_PMPROT: ??=0,??=0,AVLP=0,ALLS=0,??=0,AVLLS3=0,AVLLS2=0,AVLLS1=0 */

MC_PMPROT = 0x00U; /* Setup Power mode protection register */

/* Common initialization of the CPU registers */

/* NVICIP88: PRI88=0 */

NVICIP88 = NVIC_IP_PRI88(0x00);

/* NVICIP89: PRI89=0 */

NVICIP89 = NVIC_IP_PRI89(0x00);

/* NVICIP90: PRI90=0 */

NVICIP90 = NVIC_IP_PRI90(0x00);

/* NVICIP91: PRI91=0 */

NVICIP91 = NVIC_IP_PRI91(0x00);

/* NVICIP20: PRI20=0 */

NVICIP20 = NVIC_IP_PRI20(0x00);

/* PORTB_DFCR: CS=0 */

PORTB_DFCR &= (uint32_t)~(uint32_t)(PORT_DFCR_CS_MASK);

/* PORTB_DFWR: FILT=0 */

PORTB_DFWR &= (uint32_t)~(uint32_t)(PORT_DFWR_FILT(0x1F));

/* PORTB_PCR2: ISF=0,MUX=1 */

PORTB_PCR2 = (uint32_t)((PORTB_PCR2 & (uint32_t)~(uint32_t)(

PORT_PCR_ISF_MASK |

PORT_PCR_MUX(0x06)

)) | (uint32_t)(

PORT_PCR_MUX(0x01)

));

/* PORTB_PCR3: ISF=0,MUX=1 */

PORTB_PCR3 = (uint32_t)((PORTB_PCR3 & (uint32_t)~(uint32_t)(

PORT_PCR_ISF_MASK |

PORT_PCR_MUX(0x06)

)) | (uint32_t)(

PORT_PCR_MUX(0x01)

));

/* PORTB_PCR9: ISF=0,MUX=1 */

PORTB_PCR9 = (uint32_t)((PORTB_PCR9 & (uint32_t)~(uint32_t)(

PORT_PCR_ISF_MASK |

PORT_PCR_MUX(0x06)

)) | (uint32_t)(

PORT_PCR_MUX(0x01)

));

/* PORTB_PCR18: ISF=0,MUX=1 */

PORTB_PCR18 = (uint32_t)((PORTB_PCR18 & (uint32_t)~(uint32_t)(

PORT_PCR_ISF_MASK |

PORT_PCR_MUX(0x06)

)) | (uint32_t)(

PORT_PCR_MUX(0x01)

));

/* PORTB_PCR19: ISF=0,MUX=1 */

PORTB_PCR19 = (uint32_t)((PORTB_PCR19 & (uint32_t)~(uint32_t)(

PORT_PCR_ISF_MASK |

PORT_PCR_MUX(0x06)

)) | (uint32_t)(

PORT_PCR_MUX(0x01)

));

/* PORTC_DFCR: CS=0 */

PORTC_DFCR &= (uint32_t)~(uint32_t)(PORT_DFCR_CS_MASK);

/* PORTC_DFWR: FILT=0 */

PORTC_DFWR &= (uint32_t)~(uint32_t)(PORT_DFWR_FILT(0x1F));

/* PORTC_PCR18: ISF=0,MUX=1 */

PORTC_PCR18 = (uint32_t)((PORTC_PCR18 & (uint32_t)~(uint32_t)(

PORT_PCR_ISF_MASK |

PORT_PCR_MUX(0x06)

)) | (uint32_t)(

PORT_PCR_MUX(0x01)

));

/* PORTD_DFCR: CS=0 */

PORTD_DFCR &= (uint32_t)~(uint32_t)(PORT_DFCR_CS_MASK);

/* PORTD_DFWR: FILT=0 */

PORTD_DFWR &= (uint32_t)~(uint32_t)(PORT_DFWR_FILT(0x1F));

/* PORTD_PCR0: ISF=0,MUX=1 */

PORTD_PCR0 = (uint32_t)((PORTD_PCR0 & (uint32_t)~(uint32_t)(

PORT_PCR_ISF_MASK |

PORT_PCR_MUX(0x06)

)) | (uint32_t)(

PORT_PCR_MUX(0x01)

));

/* PORTD_PCR1: ISF=0,MUX=1 */

PORTD_PCR1 = (uint32_t)((PORTD_PCR1 & (uint32_t)~(uint32_t)(

PORT_PCR_ISF_MASK |

PORT_PCR_MUX(0x06)

)) | (uint32_t)(

PORT_PCR_MUX(0x01)

));

/* PORTD_PCR5: ISF=0,MUX=1 */

PORTD_PCR5 = (uint32_t)((PORTD_PCR5 & (uint32_t)~(uint32_t)(

PORT_PCR_ISF_MASK |

PORT_PCR_MUX(0x06)

)) | (uint32_t)(

PORT_PCR_MUX(0x01)

));

/* SCB_SHPR3: PRI_15=0 */

SCB_SHPR3 &= (uint32_t)~(uint32_t)(SCB_SHPR3_PRI_15(0xFF));

/* PORTE_DFCR: CS=0 */

PORTE_DFCR &= (uint32_t)~(uint32_t)(PORT_DFCR_CS_MASK);

/* PORTE_DFWR: FILT=0 */

PORTE_DFWR &= (uint32_t)~(uint32_t)(PORT_DFWR_FILT(0x1F));

/* PORTE_PCR6: ISF=0,MUX=1 */

PORTE_PCR6 = (uint32_t)((PORTE_PCR6 & (uint32_t)~(uint32_t)(

PORT_PCR_ISF_MASK |

PORT_PCR_MUX(0x06)

)) | (uint32_t)(

PORT_PCR_MUX(0x01)

));

/* ### Init_GPIO "PTB" init code ... */

PTB_Init();

/* ### Init_GPIO "PTC" init code ... */

PTC_Init();

/* ### Init_GPIO "PTD" init code ... */

PTD_Init();

/* ### USB_DEVICE_STACK "usb_device" init code ... */

/* Write code here ... */

/* ### USB_CDC_CLASS "usb_cdc" init code ... */

/* Write code here ... */

/* ### Init_SysTick "SysTick" init code ... */

SysTick_Init();

/* ### Init_GPIO "PTE" init code ... */

PTE_Init();

/* Enable interrupts of the given priority level */

Cpu_SetBASEPRI(0U);

}

/* Flash configuration field */

/* Pragma to place the flash configuration field on correct location defined in linkler file. */

#pragma define_section cfmconfig ".cfmconfig" ".cfmconfig" ".cfmconfig" far_abs R

static __declspec(cfmconfig) uint8_t _cfm[0x10] = {

/* NV_BACKKEY3: KEY=0xFF */

0xFFU,

/* NV_BACKKEY2: KEY=0xFF */

0xFFU,

/* NV_BACKKEY1: KEY=0xFF */

0xFFU,

/* NV_BACKKEY0: KEY=0xFF */

0xFFU,

/* NV_BACKKEY7: KEY=0xFF */

0xFFU,

/* NV_BACKKEY6: KEY=0xFF */

0xFFU,

/* NV_BACKKEY5: KEY=0xFF */

0xFFU,

/* NV_BACKKEY4: KEY=0xFF */

0xFFU,

/* NV_FPROT3: PROT=0xFF */

0xFFU,

/* NV_FPROT2: PROT=0xFF */

0xFFU,

/* NV_FPROT1: PROT=0xFF */

0xFFU,

/* NV_FPROT0: PROT=0xFF */

0xFFU,

/* NV_FSEC: KEYEN=1,MEEN=3,FSLACC=3,SEC=2 */

0x7EU,

/* NV_FOPT: ??=1,??=1,??=1,??=1,??=1,??=1,EZPORT_DIS=1,LPBOOT=1 */

0xFFU,

/* NV_FEPROT: EPROT=0xFF */

0xFFU,

/* NV_FDPROT: DPROT=0xFF */

0xFFU

};

/* END Cpu. */

#ifdef __cplusplus

} /* extern "C" */

#endif

/*!

** @}

*/

/*

** ###################################################################

**

** This file was created by Processor Expert 10.3 [05.08]

** for the Freescale Kinetis series of microcontrollers.

**

** ###################################################################

*/

Thanks for your help!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Just before the access to SIM_SCGC7, you are accessing SIM_SOPT6, which does no longer exist on Rev 2.x silicon.

You can get more detailed information between silicon rev 1.x (xN30D) and silicon rev 2.x (xN22D) in the following Application note:

http://cache.freescale.com/files/32bit/doc/app_note/AN4445.pdf

This is the code that is causing the hard fault:

SIM_SOPT6 = (SIM_SOPT6_RSTFLTEN(0x00) | SIM_SOPT6_RSTFLTSEL(0x00)); /* Set reset pin filter */

/* Initialization of the FTFL_FlashConfig module */

/* SIM_SCGC7: MPU=1 */

SIM_SCGC7 |= SIM_SCGC7_MPU_MASK;

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you very much!

I comment the code "SIM_SOPT6 = (SIM_SOPT6_RSTFLTEN(0x00) | SIM_SOPT6_RSTFLTSEL(0x00)); /* Set reset pin filter */" and everything works!

Can I set the SIM_SOPT6's bits moved into RCM?

I have another question: I build my project with Processor Expert setting the target to MK60DN256ZVLL10 but now I want to load the same project into two boards one with MK60DN256ZVLL10 and one with MK60DX256VLL10 ( in particular my MCU report PK60DX256VLL10, I checked the its revision is 2.2). Do I modify some Processor Expert settings to make formware compatibility through the board?

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

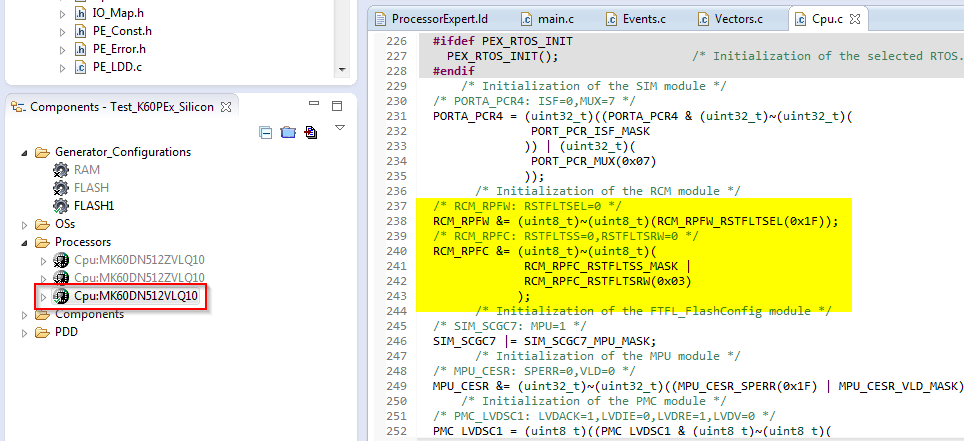

You can add the two MCUs to Processor Expert's CPU section and it will take care of the changes between the two silicons, as you can see in the following images. But of you want to do a single binary file that can be used for both boards in production, then you will need to add if else conditions to write in one or the other register.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for the explanation!

I have some problem with Processor Expert during the generation the new MCU type.

I added this IF statement to my code:

if(MCU_ID == MK60DN256ZVLL10){

/* SIM_SOPT6: RSTFLTEN=0,RSTFLTSEL=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0 */

SIM_SOPT6 = (SIM_SOPT6_RSTFLTEN(0x00) | SIM_SOPT6_RSTFLTSEL(0x00)); /* Set reset pin filter */

}else{

/* RCM_RPFW: RSTFLTSEL = 0 */

RCM_RPFW &= (uint8_t)~(uint8_t)(RCM_RPFW_RSTFLTSEL(0x1F));

/* RCM_RPFC: RSTFLTSS = 0, RSTFLTSRW = 0 */

RCM_RPFC &= (uint8_t)~(uint8_t)(RCM_RPFC_RSTFLTSS_MASK | RCM_RPFC_RSTFLTSRW(0x03));

}

Could you tell me the value of this define: RCM_RPFW, RCM_RPFC, RCM_RPFW_RSTFLTSEL, RCM_RPFC_RSTFLTSS_MASK, RCM_RPFC_RSTFLTSRW?

Thank you very much

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

The values you ask for are defined in the header files that Freescale creates for each MCU. For example, in some point of your project, there is an #include <MK60DZ10.h>. This include tells the compiler to look at the file MK60DZ10.h, which is in the following path:

<KDS_INSTALL_PATH>\eclipse\ProcessorExpert\Config\PE\CPE\wizard_data\wizards\kds\MK60DZ10\Include

The reason why the RCM_RPFW and RCM_RPFC are not defined there is because those fields of the RCM register didn't exist in the Rev 1.x of the silicon (MK60DZ parts) but do exist on the Rev 2.x.

The rev 2.x (MK60D parts, without the Z) header file can be found in:

<KDS_INSTALL_PATH>\eclipse\ProcessorExpert\Config\PE\CPE\wizard_data\wizards\kds\MK60D10\Include

Hope this helps,

Santiago

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Good Morning and thanks for the reply Santiago.

Now I'm going to test your solution!

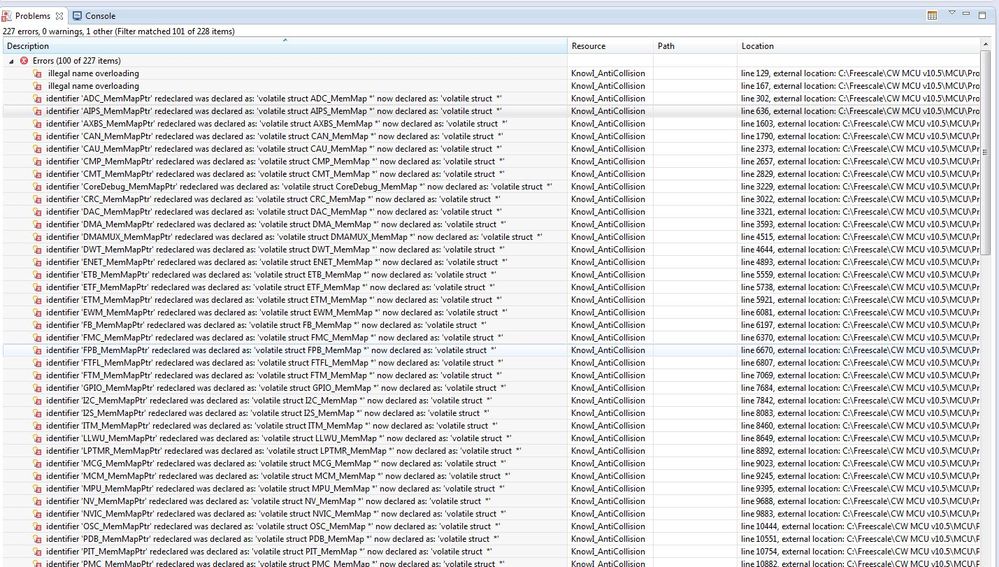

I use CodeWarrior 10.5 to develop my project, and when I include "MK60D10.h" I get some error regarding the redeclaration of some struct due to the inclusion of MK60D10 library.

Do I make an error if I add manually the define that I need (RCM_RPFW and RCM_RPFC) ?

Thanks for your time

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Federi,

Is it mandatory that the same binary file works in both boards? Because if not, a much more simple solution can be implemented:

#define REV_1

//#define REV_2

#ifdef REV_1

#include <MK60DZ10.h>

#elif REV_2

#include <MK60D10.h>

#endif

Regards,

Santiago

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Santiago,

Initially I would develop one firmware that is compatible with the two silicon version at the same time, because I use boot-loader to upload the firmware to the board. Thus I prefer an "adaptive"firmware.

But if this way is too complex, I'm looking for a more simple solution.

What do you think about that?

Thanks

Federico

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Of course the easiest solution is to have two binaries, and upload each one to the corresponding board. But if you want to have only one binary, you need to take care to the differences in the registers and define them correctly. It will add some work that you can avoid with two binaries and one if-else condition.

Is up to you :smileyhappy:.

Regards,

Santiago

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I think that I will follow easiest solution ![]()

I develop my project with Processor Expert and I can't find the include of "MK60DZ10.h" ( I looked into IO_Map.h and CPU.h).

I add this code in "Cpu.h":

//#define SILICON_VERSION_1_X

#define SILICON_VERSION_2_X

#ifdef SILICON_VERSION_1_X

#include <MK60DZ10.h>

#else

#include <MK60D10.h>

#endif

When i build the project and I include <MK60D10.h> I give some errors due to a re-declaration of some identifier (I attached an image of the errors).

Thanks for your help Santiago

/************************************ UPDATE ************************************/

Using the define to include <MK60D10.h> or <MK60DZ10.h> doesn't solve my problem.

The file IO_Map.h contain the list of define for the selected microcontroller, and this file is built by ProcessorExpert. I say this because I compare <IO_Map.h> and <MK60DZ10.h> and these two library are the same. Thus, if I include <MK60D10.h>, the compiler give me some errors because the microcontroller define are just defined in <IO_Map.h>.

My solution consist of add the content of <MK60D10.h> at the bottom of <IO_Map.h> and use two #ifdef two select the right portion of code.

Now the compiler give me new errors about undefined identifier ( MC_PMPROT, MCG_S_LOCK_MASK, PMC_REGSC_TRAMPO_MASK, SIM_SOPT2_MCGCLKSEL_MASK, WDOG_STCTRLH_STNDBYEN_MASK).

I think that this error is due to a registers modification applied in the silicon version 2 of MCU.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

If the compiler is reporting those as undefined identifiers, is because it is not able of find them. You need to make sure that they are defined in IO_Map or in the header you're finally using, and that you are including the header in the proper place.

I've checked and, for example, SIM_SOPT2_MCGCLKSEL_MASK, exists in Rev 1.x but not in 2.x. So if you try to use that code while you have SILICON_VERSION_2_X defined, you will get that compiler error.

Regards,

Santiago

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Santiago,

I follow your instruction and now my system with the other MCU can work.

But I have a new problem :smileycry:

The peripheral doesn't work.

To generate the correct CPU.h file for the MK60DX256 MCU, I copied my ProcessorExpert's components to a new project and then I join the two CPU.c files (one for MK60DN256Z and one for MK60DX256). I made the same thing for the IO_Map.h.

The system run and I do a debug, but the peripheral (3 on SPI) doesn't communicate whit the MCU.

Have you any suggestions?

I attach the CPU.c and IO_Map.

Thanks for your time

Federico

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Federico,

I have no idea without seeing the whole project and looking into the code, but the SPI module is the same in both MCUs, so if it works in one, it should work in the other.

I would check the clocks, the pin muxing registers and the SPI peripheral initialization.

Regards,

Santiago

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Santiago,

I ported my firmware for DN256Z to DX256 through the creation of a new CodeWarriror Project.

But now I have an Hard Fault during the initialization of the Virtual Com Port.

void USB_CDC_Init(void)

{

uint_32 i;

uint_8 error;

//recv_size = 0;

//send_size = 0;

rx_overflow = FALSE;

send_complete = TRUE;

rx_front = rx_rear = -1;

tx_front = tx_rear = -1;

DisableInterrupts;

/* Initialize the USB interface */

error = USB_Class_CDC_Init(CONTROLLER_ID,USB_App_Callback,

NULL,USB_Notify_Callback);

if(error != USB_OK)

{

/* Error initializing USB-CDC Class */

return;

}

EnableInterrupts;

/* delay for a while */

for(i=0; i<100000; i++){}

}

The debug stuck in Hard Fault at this instruction:

error = USB_Class_CDC_Init(CONTROLLER_ID,USB_App_Callback, NULL,USB_Notify_Callback);

During debugging I noticed that the Hard Fault occurs in the while cycle of this function:

void PE_FillMemory(register void* SourceAddressPtr, register uint8_t c, register uint32_t len)

{

register uint8_t *ptr = (uint8_t*)SourceAddressPtr;

if (len > 0U) {

while (len--) {

*ptr++ = c;

}

}

}

I think that this problem in related to the new revision of MCU, because on MK60DN256Z the USB Init works well.

What do you think about this error?

Thanks very much!

Regards

Federico

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Federico,

That error seems like an out of memory error, but I cannot assure it without debbuging the code. Can you tell me the two exact Part numbers of the Kinetis devices you are using? Do they have the same amount of RAM memory?

There is also a change in the USBSTBY bit in SIM_SOPT1 register that could generate some problems when using the same USB code in the two different platforms. I would have a look into that bit also.

Regards,

Santiago

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Santiago,

thanks for your Reply!

My first firmware was developed for MK60DN256ZVLL10 but now I want to adapt the firmware to MK60DX256VLL10 (my sample has this code: PK60DX256VLL10.

Thanks for your time

Federico