- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Re: Custom IMX28 board, no boot

Custom IMX28 board, no boot

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I design my own board with an imx28 CPU. I configured the board (resistors on LCD_D0 to LCD_05) to boot on SSP0 (SD card).

When I try to boot without SD card connected, I have the 0x8020a014 error code on the debug console. So it seems it want to boot on Sd card. So it's good.

But when I connect the SD card, I have absolutely nothing on the debug console.

I measured voltage and everything is good except VDD4P2. It equal to 0.8V !!!!!

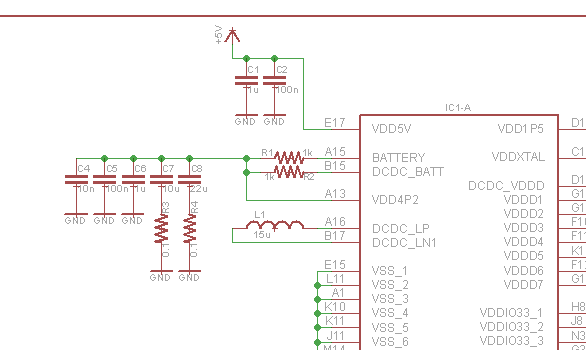

This is the schematic :

Can you help me ?

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

In order to close this topic, please find attached my patch for VDD5V Only and the patch for my DDR2 (Samsung K4T51163QQ-BCE7).

Finaly, these patchs are very simple.

To explain what my patches do :

In spl_power_init.c, I set DROPOUT_CTRL (in HW_POWER_DCDC4P2 register) to "DcDc Converter power source is DCDC_4P2 regardless of BATTERY voltage" instead of "DcDc converter selects either VDD4P2 or BATTERY, which ever is higher."

In spl_mem_init.c, I set CS_MAP (in HW_DRAM_CTL29 register) to 1 instead of 16 (?) and I set EIGHT_BANK_MODE (in HW_DRAM_CTL31 register) to "Memory devices have 4 banks" instead of "Memory devices have 8 banks".

In mx28evk.h, I set "define PHYS_SDRAM_1_SIZE" to 0x04000000 (64MB) instead of 0x40000000 (1GB).

Now, everything is fully stable. After 200 loops of 30MB test with memtester I have 0 error. All the supply from the IMX a solid and with a correct voltage.

Many thanks for all your help during these 3 months. This is the culmination :).

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

No it change every time.

My board completely boot once. And it was fully operational.

But sometimes, kernel don't start at all :

CPU: Freescale i.MX28 rev1.2 at 454 MHz

BOOT: SSP SD/MMC #0, 3V3

SPI: ready

DRAM: 64 MiB

NAND: 0 MiB

MMC: MXS MMC: 0

*** Warning - bad CRC, using default environment

Video: MXSFB: 'videomode' variable not set!

In: serial

Out: serial

Err: serial

Net: FEC0 [PRIME], FEC1

Warning: FEC1 using MAC address from net device

Hit any key to stop autoboot: 0

switch to partitions #0, OK

mmc0 is current device

reading boot.scr

** Unable to read file boot.scr **

reading zImage

3535824 bytes read in 1103 ms (3.1 MiB/s)

Booting from mmc ...

reading imx28-evk.dtb

19231 bytes read in 32 ms (585.9 KiB/s)

Kernel image @ 0x42000000 [ 0x000000 - 0x35f3d0 ]

## Flattened Device Tree blob at 41000000

Booting using the fdt blob at 0x41000000

Loading Device Tree to 43b2a000, end 43b31b1e ... OK

fdt_chosen: FDT_ERR_BADMAGIC

ERROR: /chosen node create failed - must RESET the board to recover.

FDT creation failed! hanging...### ERROR ### Please RESET the board ###

Sometimes it's a kernel panic :

0.702761] pps_core: LinuxPPS API ver. 1 registered

[ 0.707899] pps_core: Software ver. 5.3.6 - Copyright 2005-2007 Rodolfo Giometti <giometti@linux.it>

[ 0.717314] PTP clock support registered

[ 0.725267] Switched to clocksource mxs_timer

[ 0.773922] ------------[ cut here ]------------

[ 0.778662] WARNING: CPU: 0 PID: 1 at :-1067730340 debug_mutex_unlock+0x184/0x1ac()

[ 0.786435] Modules linked in:

[ 0.789539] CPU: 0 PID: 1 Comm: swapper Tainted: G W 3.17.4-fslc+g783addb #2

[ 0.797709] [<c000e22c>] (unwind_backtrace) from [<c000c590>] (show_stack+0x10/0x14)

[ 0.805519] [<c000c590>] (show_stack) from [<c0016c30>] (warn_slowpath_common+0x6c/0x8c)

[ 0.813658] [<c0016c30>] (warn_slowpath_common) from [<c0016c80>] (warn_slowpath_fmt+0x30/0x40)

[ 0.822409] [<c0016c80>] (warn_slowpath_fmt) from [<c003f198>] (debug_mutex_unlock+0x184/0x1ac)

[ 0.831172] [<c003f198>] (debug_mutex_unlock) from [<c00f2280>] (inode_init_once+0x48/0x50)

[ 0.839577] [<c00f2280>] (inode_init_once) from [<c00d2e70>] (new_slab+0x260/0x33c)

[ 0.847280] [<c00d2e70>] (new_slab) from [<c00d53ec>] (__slab_alloc.constprop.72+0x274/0x320)

[ 0.855849] [<c00d53ec>] (__slab_alloc.constprop.72) from [<c00d642c>] (kmem_cache_alloc+0xe8/0x168)

[ 0.865024] [<c00d642c>] (kmem_cache_alloc) from [<c00f25f4>] (alloc_inode+0x54/0x9c)

[ 0.872898] [<c00f25f4>] (alloc_inode) from [<c00f40c8>] (new_inode_pseudo+0x8/0x40)

[ 0.880677] [<c00f40c8>] (new_inode_pseudo) from [<c00f4110>] (new_inode+0x10/0x28)

[ 0.888388] [<c00f4110>] (new_inode) from [<c023d960>] (debugfs_mknod.part.10.constprop.15+0x1c/0x110)

[ 0.897739] [<c023d960>] (debugfs_mknod.part.10.constprop.15) from [<c023db44>] (__create_file+0xf0/0x1dc)

[ 0.907434] [<c023db44>] (__create_file) from [<c007ce74>] (trace_create_file+0x18/0x40)

[ 0.915568] [<c007ce74>] (trace_create_file) from [<c00854e4>] (event_create_dir+0x100/0x4dc)

[ 0.924138] [<c00854e4>] (event_create_dir) from [<c066c1c0>] (event_trace_init+0x174/0x244)

[ 0.932616] [<c066c1c0>] (event_trace_init) from [<c00088c4>] (do_one_initcall+0x80/0x1d4)

[ 0.940924] [<c00088c4>] (do_one_initcall) from [<c0662c70>] (kernel_init_freeable+0xf8/0x1b8)

[ 0.949588] [<c0662c70>] (kernel_init_freeable) from [<c0474b28>] (kernel_init+0x8/0xec)

[ 0.957721] [<c0474b28>] (kernel_init) from [<c0009620>] (ret_from_fork+0x14/0x34)

[ 0.965309] ---[ end trace cb88537fdc8fa201 ]---

[ 0.969958] Unable to handle kernel NULL pointer dereference at virtual address 00000000

[ 0.978064] pgd = c0004000

[ 0.980783] [00000000] *pgd=00000000

[ 0.984394] Internal error: Oops: 5 [#1] ARM

[ 0.988682] Modules linked in:

[ 0.991774] CPU: 0 PID: 1 Comm: swapper Tainted: G W 3.17.4-fslc+g783addb #2

[ 0.999887] task: c3438000 ti: c3434000 task.ti: c3434000

[ 1.005324] PC is at debug_mutex_unlock+0x124/0x1ac

[ 1.010228] LR is at debug_mutex_unlock+0x184/0x1ac

[ 1.015127] pc : [<c003f138>] lr : [<c003f198>] psr: 200000d3

[ 1.015127] sp : c3435d40 ip : 400000d3 fp : 00000000

[ 1.026621] r10: c00f25f4 r9 : 00000008 r8 : 00000000

[ 1.031860] r7 : c3fddf80 r6 : c0ec7100 r5 : 00000000 r4 : c30fcf4c

[ 1.038402] r3 : c05bba3c r2 : 00000200 r1 : c06e7580 r0 : 00000000

[ 1.044945] Flags: nzCv IRQs off FIQs off Mode SVC_32 ISA ARM Segment kernel

[ 1.052442] Control: 0005317f Table: 40004000 DAC: 00000017

[ 1.058201] Process swapper (pid: 1, stack limit = 0xc34341c0)

[ 1.064048] Stack: (0xc3435d40 to 0xc3436000)

[ 1.068439] 5d40: c30fce38 00000000 c30fc000 c00f2280 c00f2288 c3401380 c30fce38 c00d2e70

[ 1.076645] 5d60: 00004080 00000000 00000000 c3f60370 60000053 c3401380 000000d0 c00d53ec

[ 1.084851] 5d80: 00000001 00000000 c00eed94 000f000f 00000001 00000000 00000000 c00eed94

[ 1.093057] 5da0: 00000000 c3434008 60000053 000f000f 00000000 c30f56dc c30f56dc c30f52e0

[ 1.101263] 5dc0: c05d4a28 c3401380 00000000 000000d0 c00f25f4 c06b940c c30d1398 c0662518

[ 1.109468] 5de0: c0ec37b0 c00d642c c30d1398 c0662518 c30f56dc c30f5678 c3449000 c30f5678

[ 1.117675] 5e00: 00008124 c06b940c c30d1398 c00f25f4 c06b6e68 c30f5678 c30f52e0 c00f40c8

[ 1.125882] 5e20: c06b6e68 c30f5678 c30f52e0 c00f4110 c30f5678 c023d960 bfd128d4 00000006

[ 1.134088] 5e40: c05d4a28 c30f5678 c30f52e0 00000124 c30fb450 c06b940c c30d1398 c023db44

[ 1.142294] 5e60: c04876b0 00000000 c3474840 c05d4a28 c04876b0 c05c13c4 c0ec3828 c007ce74

[ 1.150500] 5e80: c04876b0 c023dc74 00000000 c3474840 c06b940c c00854e4 c04876b0 c066c04c

[ 1.158706] 5ea0: c359af80 c359af80 c0692f8c c0ec37b0 00000000 c3474840 c0ec3830 c066c04c

[ 1.166910] 5ec0: 00000000 c0662518 c0692f8c c066c1c0 00000004 00000001 00000000 c00d4ed4

[ 1.175117] 5ee0: c06a87c0 c06a87c0 c06a87c0 c3582f80 c3434038 c00088c4 600000d3 c06ac864

[ 1.183321] 5f00: 60000053 c003bb94 00000000 00000000 00000000 00000000 00000000 c06ac864

[ 1.191527] 5f20: 60000053 00000001 00000072 c063c210 c3f696ae c002eda8 c05bc800 c3f696b6

[ 1.199732] 5f40: 00000005 00000005 00000000 c069c098 00000005 c06e7260 00000072 c06e7260

[ 1.207938] 5f60: c0692f98 c0662518 c0692f8c c0662c70 00000005 00000005 c0662518 24d59a0f

[ 1.216141] 5f80: 00000000 00000000 c0474b20 00000000 00000000 00000000 00000000 00000000

[ 1.224345] 5fa0: 00000000 c0474b28 00000000 c0009620 00000000 00000000 00000000 00000000

[ 1.232549] 5fc0: 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000

[ 1.240752] 5fe0: 00000000 00000000 00000000 00000000 00000013 00000000 fe1ff7e3 dfadffff

[ 1.248995] [<c003f138>] (debug_mutex_unlock) from [<c00f2280>] (inode_init_once+0x48/0x50)

[ 1.257401] [<c00f2280>] (inode_init_once) from [<c00d2e70>] (new_slab+0x260/0x33c)

[ 1.265106] [<c00d2e70>] (new_slab) from [<c00d53ec>] (__slab_alloc.constprop.72+0x274/0x320)

[ 1.273677] [<c00d53ec>] (__slab_alloc.constprop.72) from [<c00d642c>] (kmem_cache_alloc+0xe8/0x168)

[ 1.282854] [<c00d642c>] (kmem_cache_alloc) from [<c00f25f4>] (alloc_inode+0x54/0x9c)

[ 1.290727] [<c00f25f4>] (alloc_inode) from [<c00f40c8>] (new_inode_pseudo+0x8/0x40)

[ 1.298506] [<c00f40c8>] (new_inode_pseudo) from [<c00f4110>] (new_inode+0x10/0x28)

[ 1.306210] [<c00f4110>] (new_inode) from [<c023d960>] (debugfs_mknod.part.10.constprop.15+0x1c/0x110)

[ 1.315561] [<c023d960>] (debugfs_mknod.part.10.constprop.15) from [<c023db44>] (__create_file+0xf0/0x1dc)

[ 1.325255] [<c023db44>] (__create_file) from [<c007ce74>] (trace_create_file+0x18/0x40)

[ 1.333386] [<c007ce74>] (trace_create_file) from [<c00854e4>] (event_create_dir+0x100/0x4dc)

[ 1.341952] [<c00854e4>] (event_create_dir) from [<c066c1c0>] (event_trace_init+0x174/0x244)

[ 1.350431] [<c066c1c0>] (event_trace_init) from [<c00088c4>] (do_one_initcall+0x80/0x1d4)

[ 1.358736] [<c00088c4>] (do_one_initcall) from [<c0662c70>] (kernel_init_freeable+0xf8/0x1b8)

[ 1.367390] [<c0662c70>] (kernel_init_freeable) from [<c0474b28>] (kernel_init+0x8/0xec)

[ 1.375519] [<c0474b28>] (kernel_init) from [<c0009620>] (ret_from_fork+0x14/0x34)

[ 1.383122] Code: e5933000 e3530000 0a000013 e594302c (e5952000)

[ 1.389244] ---[ end trace cb88537fdc8fa202 ]---

[ 1.394118] Kernel panic - not syncing: Attempted to kill init! exitcode=0x0000000b

[ 1.394118]

[ 1.403309] ---[ end Kernel panic - not syncing: Attempted to kill init! exitcode=0x0000000b

[ 1.403309]

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Right, this random behaviour is probably due to incorrect DDR ininitialization.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

The patch is almost finished, but I test the compatibility between U-Boot 2013, 2014 and 2015.

I try to test with yocto dizzy, so I've made :

repo init -u https://github.com/Freescale/fsl-community-bsp-platform -b dizzy

repo sync

But when I ran

bitbake core-image-minimal-dev

bitbake hangs forever on

0: linux-fslc-3.17+gitAUTOINC+783addbf53-r0 do_fetch (pid 2565)

It's the same with yocto Daisy.

Is the git down ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I don't use Yocto to build U-boot. I just build it manually, so I can't help you with this Yocto issue, sorry.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

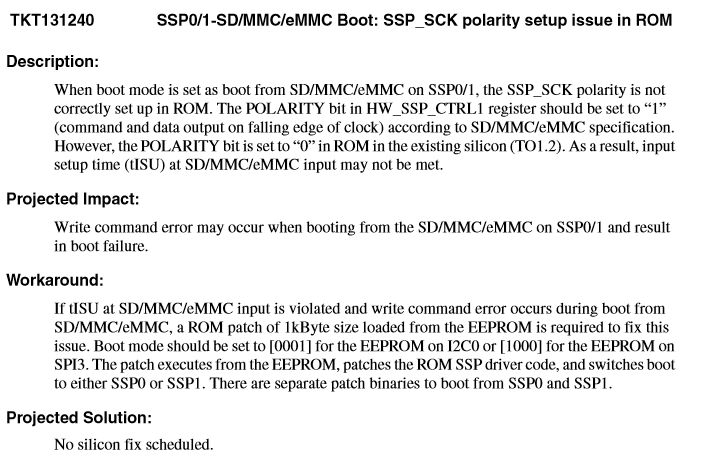

Please take a look at the iMX28 errata TKT131240.

It turns out that the polarity of the clock signal is inverted by the internal ROM and the input setup time may not be met.

The fix may require an additional EEPROM with a patch to correct the clock polarity.

Also, this link might be useful: mx28 boot issues with SSP (SD card)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

It works with iMX28EVK, so I think this is not the problem ? Isn't it ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

First thing you need to debug is why VDD4P2 only outputs 0.8V.

I would suggest following the VDD4P2 circuitry as in mx28evk or apf28 circuit that you pointed to.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

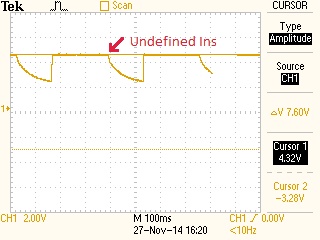

I'm sorry, I didn't update you about that.

Since I patched uboot for VDD5V only, all voltages are good.

I've solid 5V, 3V3 and 1V8.

But when I've the "Undefined ins" message, the imx28 reset and 4V2 fall down (we can see the capacitor discharge curve on the scope).

Then, when the imx28 restart, 4V2 goes directly to the 4.2V target voltage.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Ok, got it.

Then the next step is to understand why you get "Undefined ins".

This could be due to:

- Wrong toolchain: for example building with a toolchain for mx6, which is an armv7. That can cause Undefined Ins on a mx28, which is arm926ejs.

- Incorrect DDR initialization: if your DDR model is not the same as the mx28evk, then you probably need to adapt the DDR settings to match the required ones as per your DDR datasheet.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Many thanks for your help.

I use : arm-none-linux-gnueabi (generated by yocto) and my U-boot works on the imx28EVK so i think this is not the problem.

But effectively, I didn't use the same DDR (my board is 512Mb and EVK is 128Mb) so it could be the problem.

Do you have a tutorial or a procedure to change the ddr settings ?

Thank you

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Try this link:

Memory controller setup for i.MX28 and i.MX50

, and search for 'MX28_DDR2_register_programming_aid_v0.1.xlsx'

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Many thanks for your help.

So, I did :

1 : Applied VDD5V only patch

2 : Edit ltib/rpm/BUILD/imx-bootlets-src-2.6.35.3-1.1.0/linux_prep/include/mx28/platform.h

set SDRAM_SIZE to 0x20000000 (for 512Mb)

3 : Edit rpm/BUILD/imx-bootlets-src-2.6.35.3-1.1.0/boot_prep/init-mx28.c

Edit all registers value in DDR2EmiController_EDE1116_200MHz according to you excel sheet

4 : Rebuild LTIB

5 : Copy U-Boot on my SD-Card and plug the card into my board.

Now I've this :

PowerPrep start initialize power...

Configured for 5v only power source. Battery powered operation disabled.

Nov 28 201414:29:26

FRAC 0x92925552

SAMSUNG 512Mb (32Mb x16) DDR2-800 5-5-5 configuration

memory type is DDR2

Wait for ddr ready 1power 0x00820710

Frac 0x92925552

start change cpu freq

hbus 0x00000003

cpu 0x00010001

start test memory accress

ddr2 0x40000000

finish simple test

U-Boot 2009.08 (Nov 28 2014 - 11:01:45)

Freescale i.MX28 family

CPU: 454 MHz

BUS: 151 MHz

EMI: 205 MHz

GPMI: 24 MHz

DRAM: 128 MB

MMC: IMX_SSP_MMC: 0, IMX_SSP_MMC: 1

*** Warning - bad CRC or MMC, using default environment

In: serial

Out: serial

Err: serial

Net: got MAC address from IIM: 00:04:00:00:00:00

FEC0

Hit any key to stop autoboot: 0

It sounds very good :smileyhappy:.

The little issue is that U-boot tells me that my DDR is 128Mb instead of 512Mb (DRAM: 128 MB), do I need to edit another file ?

and my last question, I tried to port these modifications on Yocto (First on Uboot 2015.01-rc2), so I edited :

- arch/arm/cpu/arm926ejs/mxs/spl_power_init.c (for VDD5V only)

- arch/arm/cpu/arm926ejs/mxs/spl_mem_init.c (for DDR settings)

I edited only the structure static uint32_t dram_vals

but it doesn't work. Did I forget something ?

Again many thanks for all your help, you get me out of a tricky situation :smileyhappy:

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Damien,

Good news!

In order to fix the reported RAM size, edit include/configs/mx28_evk.h in your U-boot source and change the following lines:

#define CONFIG_NR_DRAM_BANKS 1 /* 1 bank of DRAM */

#define PHYS_SDRAM_1 0x40000000 /* Base address */

#define PHYS_SDRAM_1_SIZE 0x08000000 /* 128 MB */

Then I would suggest you to boot the kernel and then run a userspace utility called 'memtester' to make sure that your RAM is stable.

We can also try to fix this properly in U-boot 2015.01-rc. Please post your changes so that we can review them.

The only mx28 hardware that I have access to is the mx28evk, and so I could never reproduce this 'VDD5V only' issue.

It would be really nice if we could fix this in U-boot so that we help other folks from suffering from this same pain over and over.

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for your answer.

Il will try this, but it's on the new U-boot. I don't have include/configs/mx28_evk.h in my LTIB folder.

So I will first try to port my LTIB bootlets modification on U-boot, but until now it doesn't work.

I took the patch on this topic :

i.MX28 u-boot vs. bootlets - VDD5V Source Only

But I have exactly the same problem that the one describe by Ankur Patel (7 avr. 2014 01:21), on the debug console I have :

HTLLC

Configured for 5v only power source.

mxs_powHTLLC

Configured for 5v only power source.

mxs_powHTLLC

Configured for 5v only power source.

mxs_po▒HTLLC

Configured for 5v only power source.

mxs_pow

etc...

So I will try to fix it and then create a patch with all my modifications.

But i saw on the thread that you asked this guy to send his patch ? Did he ? Otherwise, I will try to fix this issue.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Unfortunately I have not seen a U-boot patch for this. If you are able to do it, please share it so we can upstream it.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Damien,

Do you plan to fix this issue with mainline U-boot? If so, please share your patch so that we can review it.

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yes I plan to fix it but it may take a little time because Bootlet in LTIB and U-boot are quite different.

But If I manage to do it, I will send you the patch.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Please look at my comments below.

The problem may be concerned with the low available current from internal i.MX28

regulators in default (start) configuration. This may take place when external parts

(say, DDR) are fed from i.MX28 PMU. Perhaps it makes sense to test the board (only)

with i.MX28 (+ minimal USB) mounted.

You may try connecting a diode between VDD5V main and the DCDC_BATT/BATTERY signals,

this made the power supply stabilized. If this approach will be tested - please pay

attention on maximum allowed voltage on the BATTERY pin (4.2 V).

The cod 0x8020A014 means ERROR_DDI_SD_MMC_DEVICE_NOT_SUPPORTED,

that is, the device is not supported, or the device cannot be seen.

Perhaps, the SSP_SCK Polarity issue in ROM also takes place here.

Instability in SD read may cause the error. Special patch for this issue

should be applied.

Have a great day,

Yuri

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Yuri,

Many thanks for your answer.

Unfortunately, I don't have the possibility to connecting a Diode because I use small SMD package so it will be very difficult.

I have the error code only when the SD card is not in place. So, I think that means Bootmode is well define on SSP0.

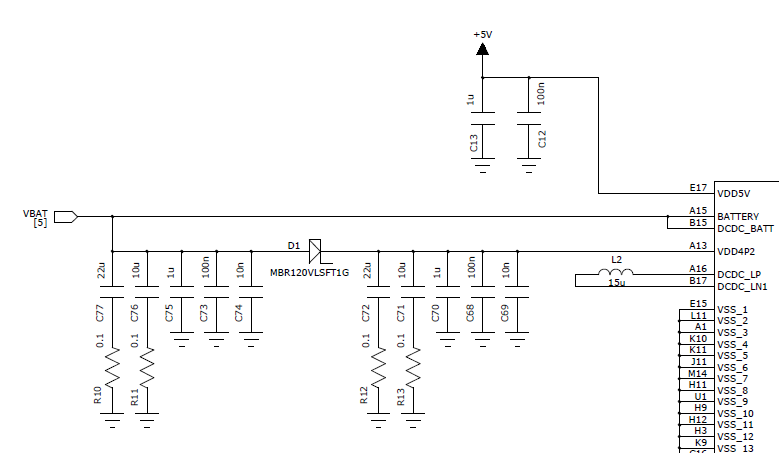

I used the reference Design from APF28. If I use the APF28 instead of my own CPU board, everything works fine and the only difference is the CPU power : See the AP28 : schematic below :

All the rest is the same between my own board :

Same U-Boot, same Kernel, same rootfs, same schematic (except power circuit).Is not the same RAM memory but it's 100% pin to pin compatible.

Is it possible that the problem comes from the imx-bootlets configuration ? I didn't set the config to VDD5V only because I use Yocto and I don't know how to do that.

Many thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Damien, good day !

Your configuration meets the app note AN4199 (Figure 9. Hardware connections for VDD5V-only applications).

According to the section "Limitations" under the Figure :

"During the early stage of device startup, before on-chip ROM execution, the input current on

VDD5V is limited to 100 mA.

The device is running on internal LinRegs on power up, and it needs to wait for the software to set

up the 4P2 rail before switching to the DC-DC converter as the power supply. The output current

from LinRegs is much lower than that of the DC-DC converter.

It is strongly suggested to use the i.MX28 power supply to power the i.MX28 ..."

From section 4.1.2.2 (VDD5V source only: software configuration) :

"For an application that uses the VDD5V source only, NO_DCDC_BATT_SOURCE must be defined on

power_prep.c in the bootlet codes. Additionally, the programmer should ensure that

NO_VDD5V_SOURCE is not defined".

Perhaps it makes sense to use the bootlets of the L2.6.35_1.1.0 release, where such

configuration is supported.

For more information please take a look at the next thread :

Custom HW based on imx28 unable to boot from linux-3.14 (yocto)

Regards,

Yuri.