- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- Re: MK20DX128vlh7 reseting

MK20DX128vlh7 reseting

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

MK20DX128vlh7 reseting

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

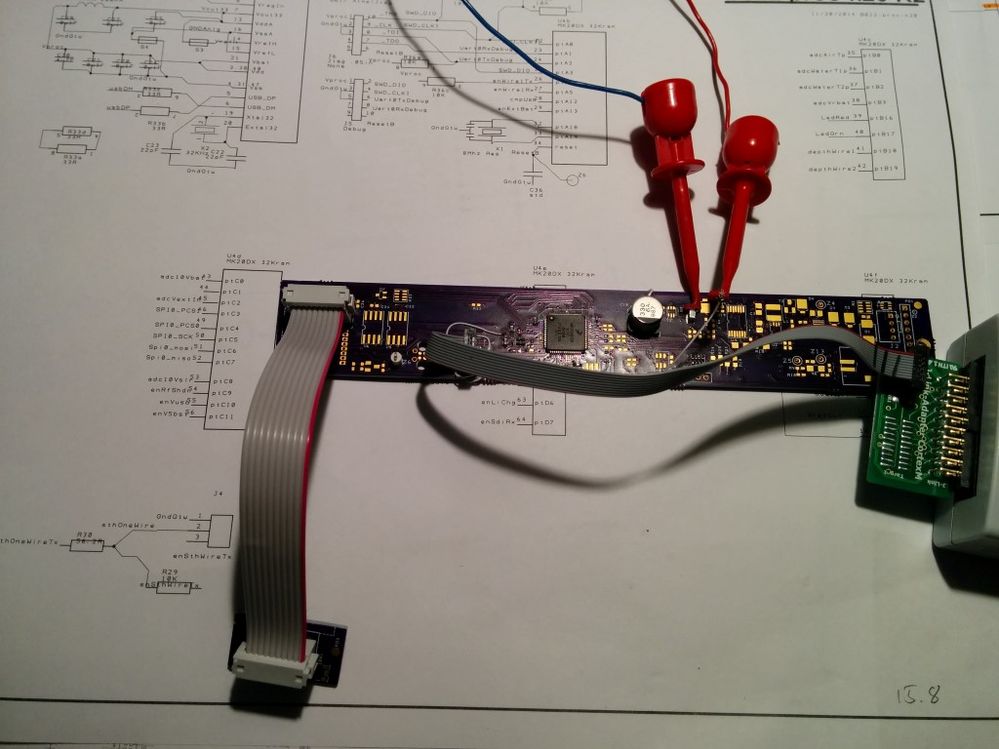

Hi, I'm bring up a new board with an MK20DX128VLH7 2N36B

The reset line RESET_b/pin34 is continuously asserting for 50uS, releasing ~2us, and then asserting.

I have a

R=10K toV3v on EZP_CS/NMI_b/PTA4 pin 26

R=100K to V3v SWD_DIO /Pta3 pin 25

I've verified the Power - Vout33 goes to VddA/VRefH/0.1uF, then 47nH to Vbat/Vdd with 0.1uF on each pin - noise on all pwr sply appears less than 5mV

No funny/50uS signals on any other pin.

If I force the EZP-CS low - then it doesn't continuously reset, I guess having entered the EZPort boot.

Should I be forcing any other pins to a known state to prevent it reseting?

Any insights appreciated.

Once it stops resetting I have a Segger JLink to program it, however currently the JLink can't access it.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Amit

Thanks for the pointer and writing it up.

After I did the post I found your online documentation, and fantastic to find someone else discussing the same problem - and since then found it mentioned deep inside AN4835..

For the J-LInk they have something called Chip Erase - which possibly is the same as the "Mass Erase"

The J-Link I have isn't communicating with my custom board MK20DX128xxx7 when in reset. I have been trying to figure out why and will try some more options tomorrow (its late here)

I have been able to have the J-Link communicate/recognize the FRDM-K64 onboard MK20DX128xx5 - but it doesn't recognize the K64 on board - so a bit puzzling. The FRDM-K64 comes populated with debug connectors for those two devices.

I 've tried setting the communications frequency to 5Khz, and keeping the reset active low, then I get back from JFlash

"Connecting ...

- Connecting via USB to J-Link device 0

- J-Link firmware: V1.20 (J-Link V9 compiled Oct 28 2014 19:25:34)

- Target interface speed: 5 kHz (Fixed)

- ERROR: Too few devices on the JTAG bus. IRPos: 0, TotalIRLen: 0

Bad JTAG communication: Write to IR: Expected 0x1, got 0x0 (TAP Command : 10) @ Off 0x1.

- ERROR: Failed to connect"

and when command to Erase Chip

- Connecting ...

- ERROR: Too few devices on the JTAG bus. IRPos: 0, TotalIRLen: 0

Bad JTAG communication: Write to IR: Expected 0x1, got 0x0 (TAP Command : 10) @ Off 0x1.

- ERROR: Failed to connect

- ERROR: Could not erase chip, not connected

This is the same error sequence if the reset line is not held low.

I think the JTAG operates while the MK20 device is in reset - so I'm wondering why the instruction to release the reset?

regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Neil

I don't have JTAG to test so I cant help u in this. For Multilink , it took me lots of time to resolve the issue. hope in ur case u get the early solution.

Kind Regards

Amit

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Amrit, No luck after trying different solutuons based on your email discussion. I've order some different cables and another set of parts to try it on the FRDM-MK20 boards and I'll build another of my development board. I'd budgeted 4 hours for this and its getting onto be three days. Real bummer.

Its a speculative product development where I'm checking out the whole tool chain. Broadcom has an M4 chip set that is also of interest so though I like the broad range of kinetis devices, really not sure why the development environment is so painful, is it just bad luck or something deeper.

cheers

Neil

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Neil,

I check you are using 100K ohm Pull-up resistor connects with SWD_IO/PTA3 pin, please use 10K ohm or 4.7Kohm instead.

Freescale provides TWR-K20D72M board, about JTAG/SWD debug interface, please refer TWR-K20D72M board schematics.

TWR-K20D72M board schematics could be downloaded from below link:

http://cache.freescale.com/files/32bit/hardware_tools/schematics/TWR-K20D72M_SCH1.pdf

Wish it helps.

best regards

Ma Hui

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Ma thanks for the reply.

I've built a 2nd minimal board built, with just a focus on the processor and left off the Xtals that are close to the SWD/JTAG lines.

I've attached 10K pullup to PTA3/SWDIO PTA2/JTAG_TDO pulldown to PTA0/SWD_CLK and pullup to PTA4/NMI

I've just got the JLINK talking to it over 4" Segger 9pin cable.

The JLINK/Commander was able to read the registers.

Then through KDS1.1.1 I've been able to download a blinkey to my board.

Not sure how the MASS ERASE happened, I tried a manual approaches over JLINK, then thought I'd locked the board, and finally KDS worked.

Its not clear why my #1board is not working - it seems exactly the same. Later I'll cut off the processor on it and try another one

I also tried a USBDM/FRDM-MK20D50 - but so far this only works with its paired processor and not when I take it off via the same cable to my custom board.

So to summarize, in the past I've used an Atmel custom JLINK on bringing up an Atmel Mega2560 processor - and it just worked.

This time, I took the same path using a general segger JLINK - and its been very painful - what I hoped would take 0.5day bringup took a week.

My #1 board showed the Reset line pulsing and it was the only indication the silicon was working.

When I laid out the board, I paid attention to the application and my analog circuitry- looked at the FRDM-K20 /FRDM-KL25z boards and documents and didn't read up on the JLINK and Kinetis. I briefly scanned AN4835 - but has no sample diagrams.

I've had a crash course in JTAG/SWD - from the community.freescale, mbed.org and Segger JLINK - Segger has poor documentation and a wide range of silicon processors (probably all have device specific anomalies) to support, the JTAG/SWD interface requirements are buried in text, and they obviously have a hope of selling all their advanced trace equipment and IMHO the scripting language descriptions are painful to figure out.

I really used the the FRDM-K20D50 /KL25z proof of concept boards to prototype my core software using KDS over OSDB2.1 over SWD and even more faster mbed.org on a FRDM-KL25z

I really like the USBDM on rom based OSBDM way ahead for building a fast productive integration target environment.

I really appreciate the postings on the community board - and a big thanks to Amit and Pgo and other people who have posted.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Neil

I think Your microcontroller is not programmed at all so for 1st time programming ur uc, follow this post. Factory programmed uc comes with watchdog enabled and so it keeps on resetting. The below post describe how to deal with that using PE Multilink but you can check with the J link.

https://community.freescale.com/docs/DOC-99609

Hope It helps

Kind Regards

Amit