- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- Product Forums

- :

- Vybrid Processors

- :

- Re: about Errata 7293

about Errata 7293

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, Vybrid expert

in Vybrid_1N02G, we descript 7293 as follows:

e7293: XTAL: ROM code may fail to boot and return to safe mode due to insufficient

warm up time for the crystal oscillator

Errata type: Errata

Description: On occasion the xtal oscillator may not get sufficient time to stabilize. In this case, the boot

code will jump to safe mode and will continue to operate from the internal RC clock.

Workaround: Use an external clock/oscillator module to clock to the processor, ensuring the clock signal is

stable no more than 1.2 msecs after reset is released.

so my question is:

can I understand this errata that customer MUST add a external clock/oscillator if they want to be safe ( I think it's a normal requirment)?

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi John,

on rev 1.2 default wait time was increased to 4ms.

Delay time is clocked by SIRC. 1/32000 * 256 = 8ms counting SIRC (128kHz /4). Maximal wait time for XTAL is 8ms (SCNT = 255).

Deadline is counted by PIT counting IRC (24MHz) with deadline time 1.5 * delay time.

Please program just OSC_TUNED Bank 0, Word7, byte 3 to 0xFF.

Programming project is part of Vybrid sample code freescale.com/vybrid ( http://www.freescale.com/webapp/sps/site/prod_summary.jsp?code=TWR-VF65GS10&fpsp=1&tab=Design_Tools_...)

Modify \src\projects\ocotp_fuses\ocotp_fuses.c in ocotp_fuses project. (my In attachment).

Final binary ...\build\ds5\projects\ocotp_fuses\Debug\ocotp_fuses.axf (my binary is in attachment also)

/Jiri

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

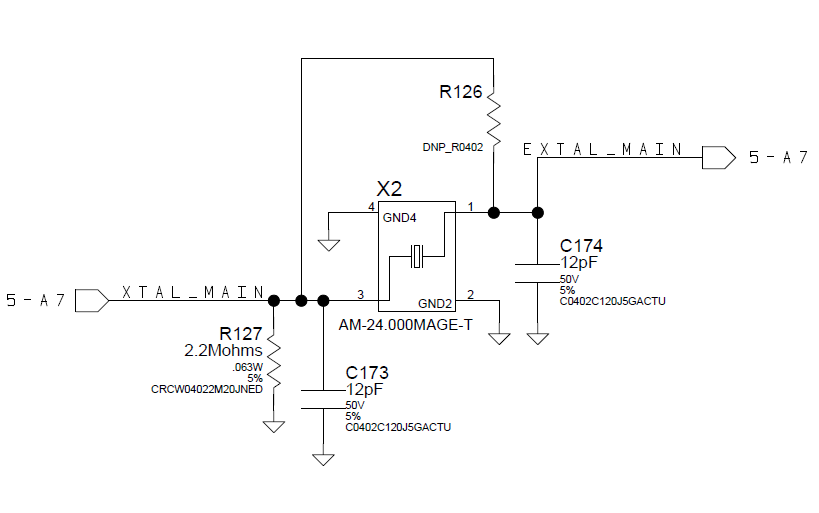

Very good point, Weisong! This 2.2M resistor is indeed added to shorten the crystal start-up process (see "Errata" for details).

Thanks!

John,

Perhaps it makes sense to post the relevant schematic fragment with the oscillator circuit and the scope screenshots to illustrate the crystal oscillator behavior on your board, please?

(IMO, it is not the stray capacitance added to the limp load capacitors - lowering them down to 3.9pF does not help, as per your tests.)

BTW, how critical is the crystal start-up duration for you? Do you need it to be really fast?

The point here is that, as far as I remember, with the default setting of what is called something like "crystal wait time", which is 4ms, it should work. At the same time, there should be an option for the latest Vybrid to extend it up to 8ms.

jiri-b36968 kindly agreed to help with this issue - thanks in advance for that!

Sincerely yours, Naoum Gitnik.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

See the attached image for the schematic. The 2.2M resistor is in the circuit. If I grab a scope shot of the behavior, what do you want to see? 3.3V, Reset, and the Xstal?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Yes, John - mandatory Pwr-On-Reset and Xtal Output on the same screen, 3.3V being "nice-to-have", and if possible for both passing and failing cases (with temperatures mentioned, I guess...).

- Still no reply regarding lengthening "crystal wait time" if possible for your application...

/Naoum.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear John,

Thanks for the details provided, I will share them with my colleague currently investigating this issue. IMO, it will take several days.

A bit about timing...

Since the crystal oscillator is halted with Vybrid Power-On-Reset asserted, the time count starts when it is de-asserted. At the same time (and in our favor), power to the components, including an external 24MHz oscillator (if used), is applied without Vybrid Power-On-Reset delay, so you may easily provide enough time for the external oscillator to start-up.

A bit about external 24MHz oscillator type and connections...

Please, review Re: Workaround for unreliable boot from SD? to find a solution "ready for consumption"!

Regards, Naoum Gitnik.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, Naoum

Many thanks for your reply.

hopefully get the final result soon. :smileyhappy:

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

We tried smaller load capacitor value on the crystal. No difference with 3.9pF or 6.8pF. About half the time it won't boot.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello John,

Thanks for important information!

Yes, 2N02G looks like the latest revision.

Let me check this issue for you with the other teams.

Regards, Naoum Gitnik.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

We were just given 5 new production level parts by the FAE. They are supposed to be the latest silicon with the Vbat current problem fixed. We were told by the FAE that the version number portion of the part number on top would be no different than what we had before, but that these are updated silicon.

The part number on top is MVF61NS151CMK50. The other two lines on the part say, 2N02G and PTXCTAA1349N if that helps.

To differentiate the Vybrid's we have, we read the cpu version register using code provided with the Tower.

The CPU version register = 0x00000080

n = snprintf(p, n, "%d.%d\r\n",(*(int *)0x00000080 & 0x000F0)>>4,(*(int *)0x00000080 & 0x0000F));

The result is version = 1.3

Apparently version 1.2 was not entirely successful.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Weisong,

The Vybrid revision currently on the market has this issue fixed (the Errata document is a bit lagging, sorry...), so feel free to not read beyond this point :smileyhappy:

If you interested in the problem history and/or need a really precise clock, please, take a look at the below threads:

- https://community.freescale.com/message/351803#351803

- https://community.freescale.com/message/342197#342197

Regards, Naoum Gitnik.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, we just received production level V1.3 parts. We are still having problems reliably booting the Vybrid at cold temps (-20C is our products spec).

Looking at the crystal, we see that 3.2ms after 3.3V is applied, the Vybrid starts to drive the crystal. It takes about 800 us beyond that for the crystal to begin oscillating. This is true for room temp, or cold cases. We are only having the boot issue at cold.

We are booting from QSPI. When there is a boot failure, there is no indication that the Vybrid attempted to access the QSPI, so perhaps it is in safe mode.

How can we tell if the Vybrid is in safe mode? Is there an external flag of some kind?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello John,

Are you sure this is the latest Vybrid revision?

What is written on the component top, please? - Either copy it or send a photo, please.

(BTW, if it is the same revision as the Errata document on our site, it is still the previous one - with the Errata document we are still one revision behind (sorry...).)

Yes, there is a bit indicating where Vybrid is booting from (please, refer to the Reference Manual for details).

Regards, Naoum Gitnik.