- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Re: gpt0 Source ID not owned in Imx8qxp

gpt0 Source ID not owned in Imx8qxp

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Linux kernel 4.19.35

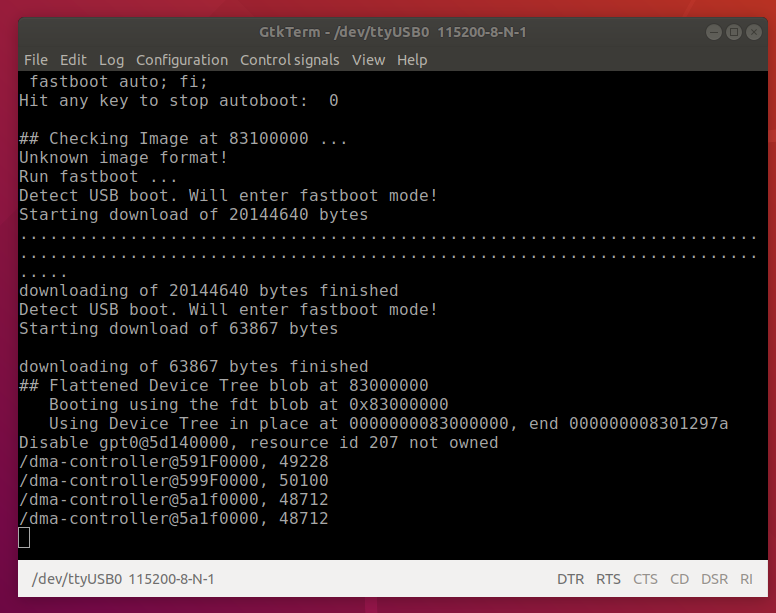

Currently, I am flashing kernel 4.19.35 and my custom device tree in the imx8qxp custom board via fastboot.

UUU command:

CFG: FB: -vid 0x1fc9 -pid 0x012f

FB: ucmd setenv fastboot_buffer ${loadaddr}

FB: download -f Image

FB: ucmd setenv fastboot_buffer ${fdt_addr}

FB: download -f fsl-imx8qxp-mek.dtb

FB: download -f unimog-imx8qxp-sthu.dtb

FB: acmd booti ${loadaddr} - ${fdt_addr}

FB: done

SCFW:

SCFW only uses gpt4 for M4.

ATF:

imx8qx_bl31_setup.c handles the gpt0 . Only change made in ATF firmware was changing from uart0 to uart1, as the custom boards handles.

As the bl31 firmware handles the gpt0 for linux kernel, while booting my device tree and Image, why is gpt0 not owned by A35 kernel?

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Hossain

one can look at

i.MX8 Boot process and creating a bootable image

verify that proper scfw version was used : i.MX Software and Development Tools | NXP

https://www.nxp.com/webapp/Download?colCode=L4.19.35_1.1.0_SCFWKIT-1.2.7.1&appType=license

also what is chip revision ? if C0 (suffix "AC") - L4.19.35 should not be used. Try L4.14.98_2.3.0 or L5.4.3

Best regards

igor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Mosaddek

seems gpt0 is intended for usage with M4 MCUXpresso SDK SDK_2.7.0_MEK-MIMX8QX

and one can build it on Welcome | MCUXpresso SDK Builder

Also one can look at

System Controller Firmware 101 - Resource management service

System Controller Unit (SCU) Introduction for i.MX 8QXP MEK - i.MXDev Blog

Best regards

igor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Igor,

Thanks for the reply.

SCFW:

board.c file is my custom scfw .c file for my custom board pmic configuration based on imx8qxp-mek board.c.

Only GPT4 is used as a resource for m4.

BRD_ERR(rm_set_resource_movable(pt_boot, SC_R_GPT_4, SC_R_GPT_4, SC_TRUE));

ATF:

The ATF-firmware bl31 handles the SC_R_GPT_0 for the linux kernel.

It initializes the GPT_0. Please check the attachment imx8qx_bl31_setup.c and sec_rsrc.h

/* Turn on GPT_0's power & clock for non-secure OS/Hypervisor */ sc_pm_set_resource_power_mode(ipc_handle, SC_R_GPT_0, SC_PM_PW_MODE_ON); sc_pm_clock_enable(ipc_handle, SC_R_GPT_0, SC_PM_CLK_PER, true, 0); mmio_write_32(IMX_GPT0_LPCG_BASE, mmio_read_32(IMX_GPT0_LPCG_BASE) | (1 << 25));

I am not understanding why resource id is not owned in linux device tree as it is configured in atf firmware.

Device Tree also used in imx8qxp-mek:

gpt0: gpt0@5d140000 {

compatible = "fsl,imx8qxp-gpt";

reg = <0x0 0x5d140000 0x0 0x4000>;

interrupts = <GIC_SPI 80 IRQ_TYPE_LEVEL_HIGH>;

clocks = <&clk IMX8QXP_CLK_DUMMY>, <&clk IMX8QXP_GPT_3M>;

clock-names = "ipg", "per";

power-domains = <&pd_lsio_gpt0>;

};

I hope you have an overview now on my configuration, after checking the files.

According to my understanding my configuration does not allow gpt0 to be used in m4. Please let me know how can I handle the issue and where I am making the mistake.

Kind Regards,

Hossain

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Mosaddek

one can try to add the same codes for gpt0 as for gpt4 in board.c, with

different owner - a35 instead m4.

>Only GPT4 is used as a resource for m4.

>BRD_ERR(rm_set_resource_movable(pt_boot, SC_R_GPT_4, SC_R_GPT_4, SC_TRUE));

This shall print a list of partitions, resources, memory regions and pads owned by the various partitions.

>$ dump rm

Also may be useful:

Moving CAN to A core - i.MX8QX - L4.19.35-1.1.0 BSP

https://community.nxp.com/thread/507460

Best regards

igor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hallo Igor,

I am facing an unusual problem. When I changed and generated new bl31.bin. Created a new flash.bin. Flashing via SDPS the flash.bin in the board. The UART stops working. The console sends data to putty but I cannot write. When I flash again the old flash.bin the UART is not working.

I tried it with a new board. Flashing the old binary and the uart is working. after I am flashing the new flash.bin the uart stops working also for the old binary.

I am not understanding how it is killing the tx of uart from board.

Do you have any idea regarding this issue.

Kind Regards,

Hossain

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Hossain

one can look at

i.MX8 Boot process and creating a bootable image

verify that proper scfw version was used : i.MX Software and Development Tools | NXP

https://www.nxp.com/webapp/Download?colCode=L4.19.35_1.1.0_SCFWKIT-1.2.7.1&appType=license

also what is chip revision ? if C0 (suffix "AC") - L4.19.35 should not be used. Try L4.14.98_2.3.0 or L5.4.3

Best regards

igor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks a lot for the support.

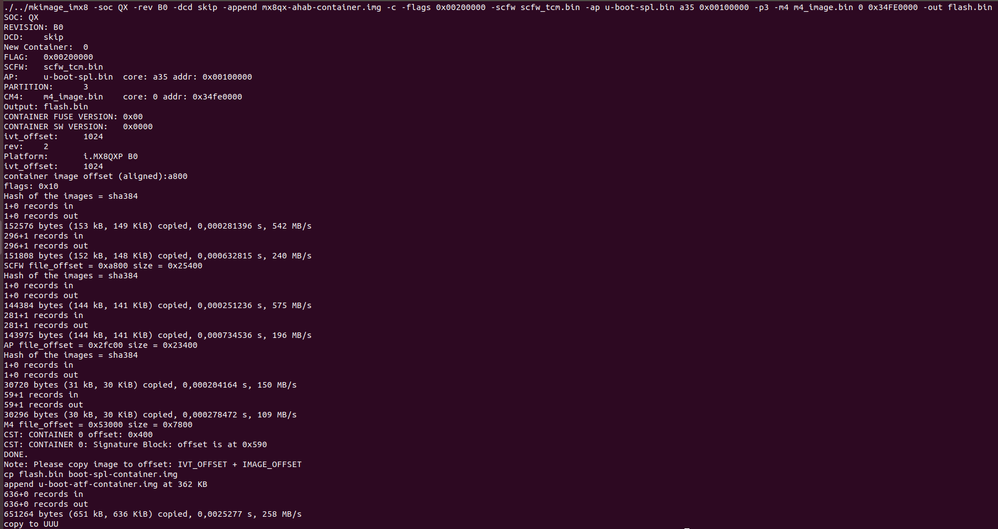

Currently my scfw configured with partitioning. Your reference helped me to build the scfw correctly.

make SOC=iMX8QX flash_linux_m4

SCU console: (provided also in attachment)

Partition 0: --> SCU

Partion 1:-> A35 "In partition 1 gpt_0 is enabled"

GPT_0

GPT_1

GPT_2

GPT_3

But with this flash.bin file, my bootloader is not flashing I think this due to addressing issue. The reason is flash_linux_m4 does not use:

AP: u-boot-atf.bin core: a35 addr: 0x80000000

Do you think also the same?

Thanks a lot for your informations.

Kind Regards,

Hossain

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

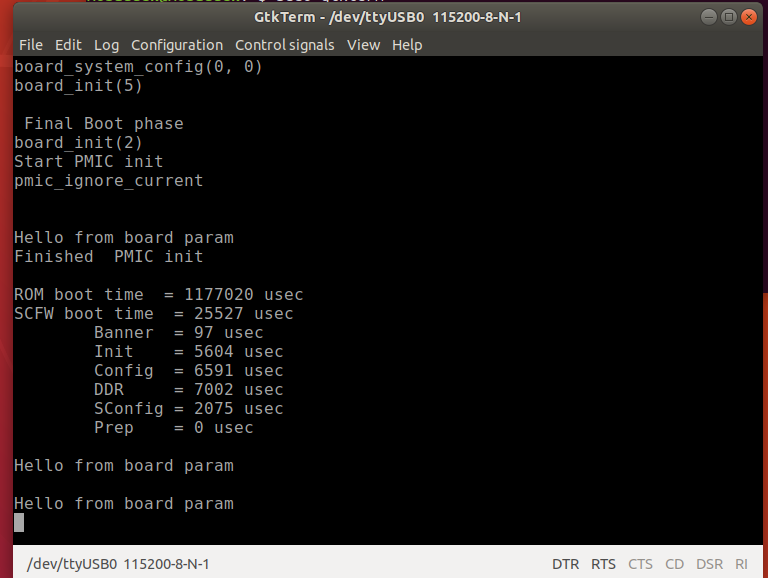

Thanks for the reply.

I have made the following changes in board.c file. Currently I disabled m4 resource.

sc_err_t board_system_config(sc_bool_t early, sc_rm_pt_t pt_boot)

{

sc_err_t err = SC_ERR_NONE;

/* This function configures the system. It usually partitions

resources according to the system design. It must be modified by

customers. Partitions should then be specified using the mkimage

-p option. *//* Note the configuration here is for NXP test purposes */

sc_bool_t alt_config = SC_FALSE;

sc_bool_t no_ap = SC_FALSE;

/* Get boot parameters. See the Boot Flags section for defintition

of these flags.*/

(void) boot_get_data(NULL, NULL, NULL, NULL, NULL, NULL, &alt_config,

NULL, NULL, &no_ap);board_print(3, "board_system_config(%d, %d)\n", early, alt_config);

/* Configure initial resource allocation (note additional allocation

and assignments can be made by the SCFW clients at run-time */

if (alt_config != SC_FALSE)

{

sc_rm_pt_t pt_a35;#ifdef BOARD_RM_DUMP

rm_dump(pt_boot);

#endif/* Mark all resources as not movable */

BRD_ERR(rm_set_resource_movable(pt_boot, SC_R_ALL, SC_R_ALL,

SC_FALSE));

BRD_ERR(rm_set_pad_movable(pt_boot, SC_P_ALL, SC_P_ALL,

SC_FALSE));/* Allocate A35 partition */

BRD_ERR(rm_partition_alloc(pt_boot, &pt_a35, SC_FALSE, SC_TRUE,

SC_FALSE, SC_TRUE, SC_FALSE));/* Mark all A35 subsystem resources as movable */

BRD_ERR(rm_set_subsys_rsrc_movable(pt_boot, SC_R_A35,

SC_TRUE));BRD_ERR(rm_set_resource_movable(pt_boot, SC_R_GPT_0,

SC_R_GPT_0, SC_TRUE));/* Move partition to be owned by SC */

BRD_ERR(rm_set_parent(pt_boot, pt_a35, SC_PT));/* Move boot to be owned by a35 0 */

if (no_ap != SC_FALSE)

{

BRD_ERR(rm_set_parent(SC_PT, pt_boot, pt_a35));

}#ifdef BOARD_RM_DUMP

rm_dump(pt_boot);

#endif

}

else

{

err = SC_ERR_UNAVAILABLE;

}return err;

I am unable to write on the UART for SCU.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content