- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- QorIQ Processing Platforms

- :

- Layerscape

- :

- 1021a board bring up replace CPLD with Atmega328P

1021a board bring up replace CPLD with Atmega328P

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

1021a board bring up replace CPLD with Atmega328P

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Guys,

I have a standalone ls1021a, eMMC, a Atemega328P chipset on the board and a JTAG interface. I want to bring the board up to initiates the power-on reset flow. I am trying to implement the CPLD logic into C using Atemega328P to achieve the board initialization stage.

Does any one know how many signals do I need to consider which I need to trigger them in the right sequence?

According to the QorIQ LA1021A Reference Manual.

I also have a question specifically during the POR sequence,

Do I have to give a signal to the cfg_eng_use0 or once the POR starts everything will be handled by itself.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

It is reasonable to refer to the TWR-LS1021A design documents (including CPLD source) available at:

QorIQ® LS1021A Tower® System Module | NXP

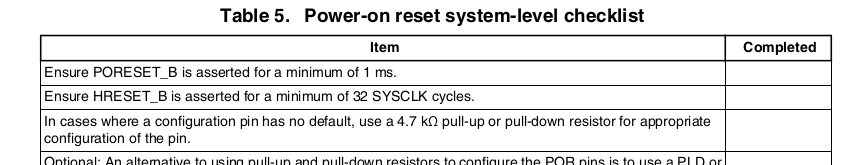

The cfg_eng_use0 has to be connected as stated in the AN4878 - QorIQ LS1021A Design Checklist, Table 8. LS1021A reset configuration signals. Also in this application note 4.3.1 Configuration signals sampled at reset it is written:

"Reset configuration signals are sampled at the negation of PORESET_B. However, there is a setup and hold time for these signals relative to the rising edge of PORESET_B, as described in the chip's data sheet."

So this is the board designer's responsibility to properly strap (by resistor) the cfg_eng_use0.

> Do I have to give a signal to the cfg_eng_use0

After PORESET_B is deasserted the pin function is IFC_WE0_B which is pure output, so it is not possible to drive the signal externally during normal operation.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

(1) "Reset configuration signals are sampled at the negation of PORESET_B" --------------------------> does negation mean the falling edge of this signal then to low?

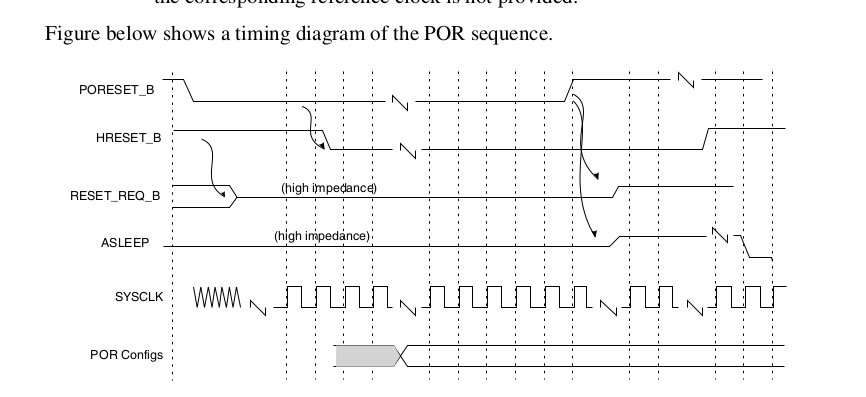

According to the data sheet Section 4.4.1 of LS1021a reference manual:

6. External system logic negates PORESET_B after its required hold time and after

POR configuration inputs have been valid for their required setup times.

7. The device samples the RCW source POR configuration inputs (cfg_rcw_src[0:n])

on deassertion of PORESET_B to determine the RCW source. Note that the POR --------------------------> does deassertion means rising edge then to high

configuration inputs are sampled only on a PORESET_B.

(2)so basically after drive the PORESET_B to high for 1ms minimum, it will start validate the POR inputs to determine the boot source, so all I need to do is to drive this pin high for 1ms high then low for amount of time after the POR configuration inputs have been valid for their required setup times then what should I do after?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

1) PORESET_B is an active-low cignal (_B), thus:

negation = deassertion = low->high edge

2) Not correct - see 1) and refer to the POR sequence from the processor's RM.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

so basically :

4.3 Power-on reset recommendations

Various chip functions are initialized by sampling certain signals during the assertion of PORESET_B. These power-on reset

(POR) inputs are pulled either high or low during this period. While these pins are generally output pins during normal

operation, they are treated as inputs while PORESET_B is asserted. When PORESET_B de-asserts, the configuration pins

are sampled and latched into registers, and the pins then take on their normal output circuit characteristics.

so by saying asserted in this case means the signal is active low?

Just want to double confirm with you last time:

So basically this signal is active low and then if I make it stays low for 1ms then after 4 system clocks drive it to high (the falling edge requires max 1 sys clock cycle) then it will start sampling the boot source cfg_rcw_src[0:n]?

before asserting this PORESET_B signal do I need to perform a toggling event on this pin?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

> so by saying asserted in this case means the signal is active low?

Yes.

> So basically this signal is active low and then if I make it stays low for 1ms

> drive it to high (the falling edge requires max 1 sys clock cycle) then it will start

> sampling the boot source cfg_rcw_src[0:n]?

Correct - also refer to the LS1021A Data Sheet, Table 24. RESET initialization timing specifications

> before asserting this PORESET_B signal do I need to perform a toggling event on this pin?

No.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

how about the power reset control signal from the PMIC?

is this be asserted automatically once PORESET_B is high?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

> is this be asserted automatically once PORESET_B is high?

What do you mean?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi ufedor,

Any specific singal requirements before the ls1021a standalnoe prototype to detect the codewarrior tap via the usb interface?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Sorry, the request is not clear.

What does it mean "to detect the codewarrior tap via the usb interface"?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

> asleep signals goes high at the point when PORESET_B goes low

This is OK considering that ASLEEP is tri-stated and has a pull-up.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

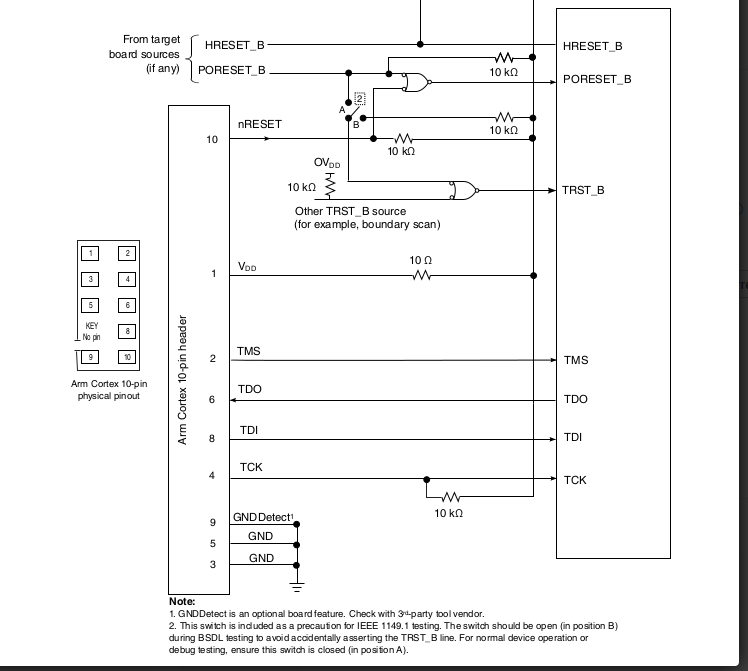

can you take a look at his regarding the JTAG/COP port is used case

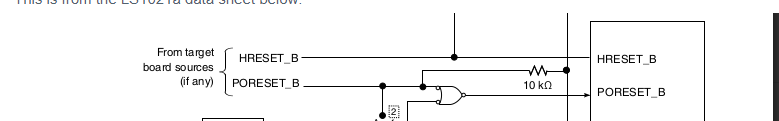

This is from the LS1021a data sheet below:

Figure - A

Figure - B

Figure - C

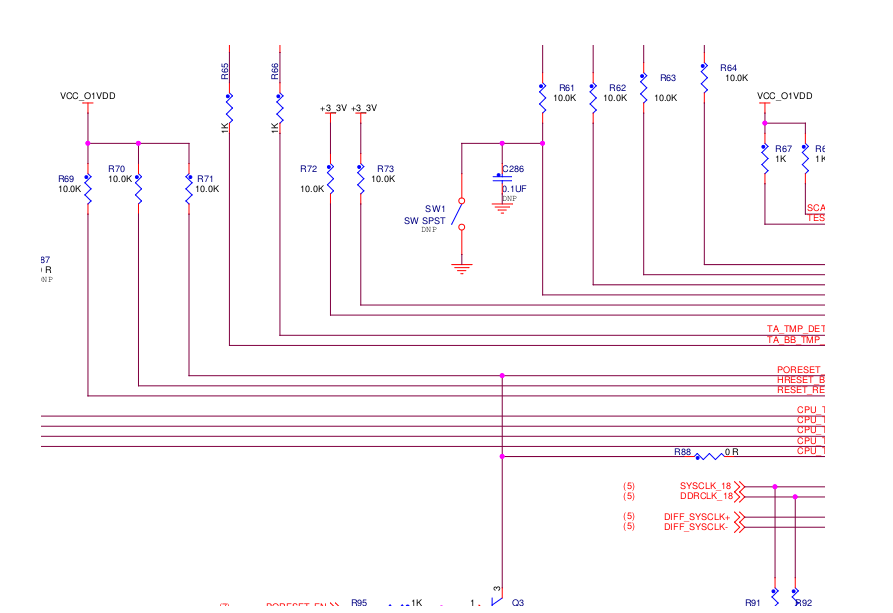

(1)I used a resistor R88 to connect TRST and POWER RESET Line does this

match the requirements as shown in Figure A? These two pins are then pulled up by a 10k resistor to Vcc_O1VDD, my design does not have HRESET_B pin.

(2)So as picture shows below: why there are HRESET_B and PORESET_B on the left side what source triggers them?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The R88 is OK, but you have to consider the QorIQ LS1021A Data Sheet, Table 24. RESET initialization timing specifications:

"Maximum rise/fall time of PORESET_B is 1 SYSCLKs"

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

(1)by saying that because I use c logic to implement the start up logic what I am doing is before asserting the PORESET_B, I drive it to high then low (asserted) for 50ms (tho only needs 1ms min) then I de-assert PORESET_B then I did DDR reset, PCIE reset some I/O interface enabled. How am I able to manage the rise/fall time via the C code on AVR studio IDE which I am using to flash the code into the atmega on my board

(2) What is the relation between PORESET_B and TRST_B

seems like HRESET_B and TRST_B has relation but TRST_B and PORESET_B does not according to the CPLD code on the TWR-LS1021A eva board:

/CPU, DDR and peripheral devices reset

assign poreset_b_18 = pwr_hrst_n && jtag_rst_b_18 && sw_rst_n;

assign cpu_trst_b_18 = pwr_hrst_n && k20_trst_b_18;

assign rst_flsh_n = pwr_hrst_n;

assign elev_rstout = hreset_b_18;

assign ddr_rst_b = hreset_b_18;

assign ethphy_rst_b = hreset_b_18;

assign rst_usbhub = hreset_b_18;

assign hdmi_rst_b = hreset_b_18;

assign rst_pcie_n = hreset_b_18;

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

1) The question was not about the CPLD, but about the transistor which is used to assert the PORESET_B - in thia case the Data Sheet requirement can't be fulfilled.

2) The question is not clear.

assign poreset_b_18 = pwr_hrst_n && jtag_rst_b_18 && sw_rst_n;

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi ufedor,

Do I have to design a hreset_b_18 signal too? what gonna happen if I did not consider this signal on my PCB, I only have poreset_b_18 in my design consideration

In other words,

Does HRESET_B needs to be part of the design?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Only PORESET_B is essential during POR sequence - refer to the QorIQ LS1021A Reference Manual, 4.4.1 Power-on reset sequence.

HRESET_B is not needed for JTAG interface proper operation.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

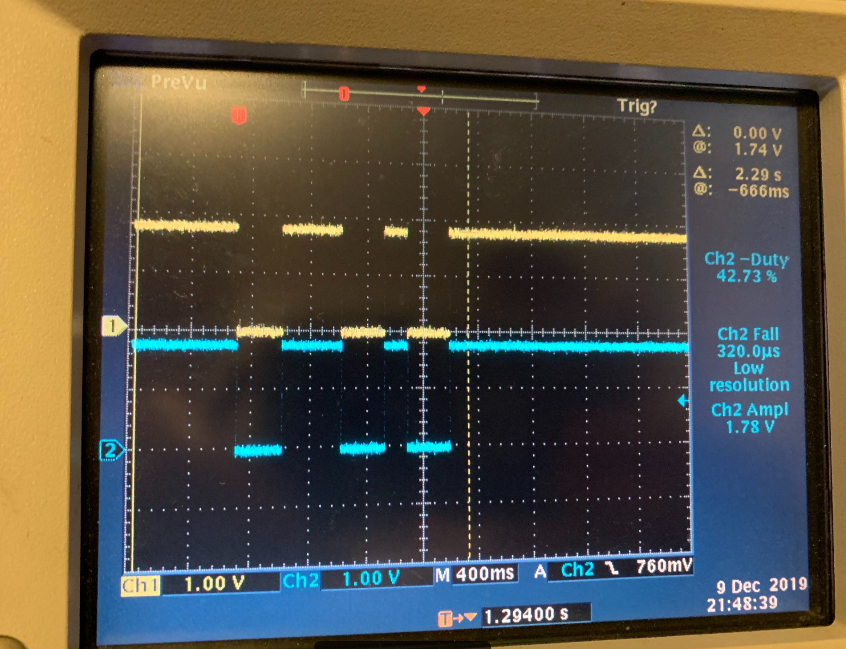

We used oscilloscope to scope the signal of JTAG_RESET and PORESET_B we found this on the eva board

The power reset gets triggered 3 times whenever you try to run the debug mode from the CW via JTAG interface.

Do I have to trigger the same sync wave forms on my atmega328p ? remember I replaced CPLD controller with atemega328p on my device

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The JTAG interface must be implemented as shown in the AN4878 - LS1021A Design Checklist, Figure 32. JTAG interface connection.

The debugger asserts nRESET several timed to establish connection.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I understand that my only question here is do they have to match the signal synchronization like the one in the pic I shared that part of the thing I could not tell from Figure 32