- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- General Purpose Microcontrollers

- :

- LPC Microcontrollers

- :

- Re: LPC51U68: Need help with SPI slave bytes shift issue

LPC51U68: Need help with SPI slave bytes shift issue

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

LPC51U68: Need help with SPI slave bytes shift issue

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello my friends:

I’m new for LPC51U68. Now I’m migrating from LPC111x to LPC51U68 and encounters some issues, one of major issue is SPI slave byte shift.

Environment:

1.Modified LPC1114 example SSPMaster, sends 64 Bytes per frame and 82ms idle between 2 frames(in a while loop).

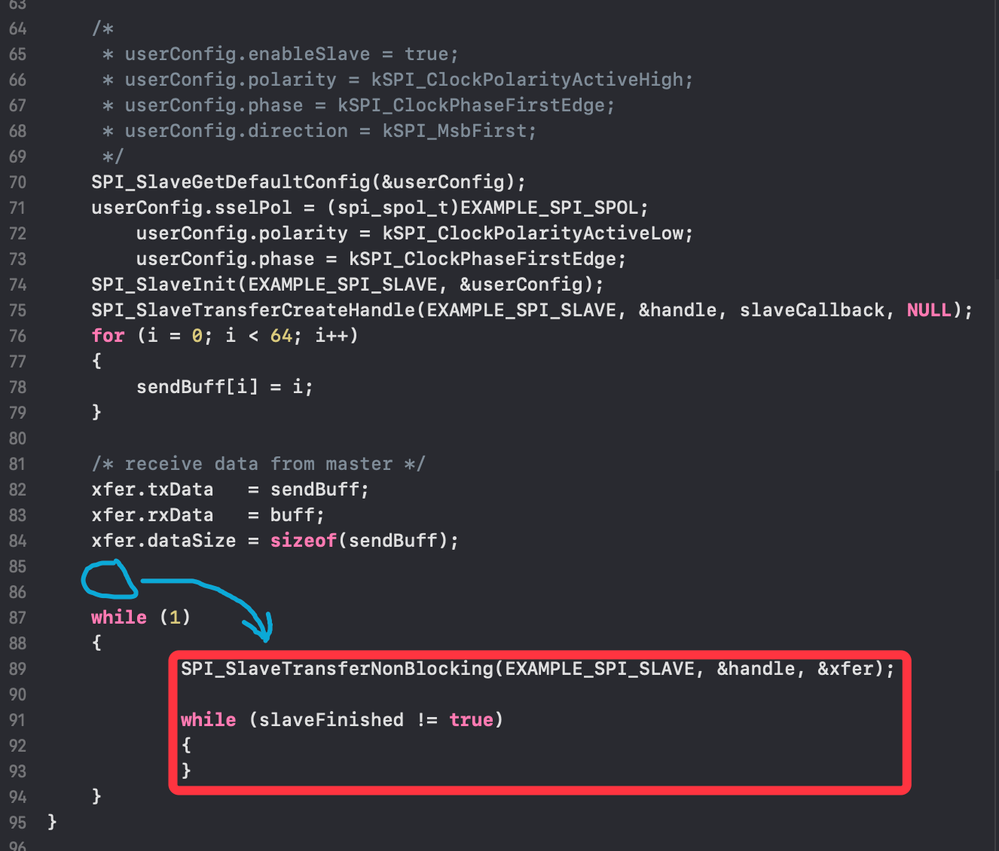

2.Modified LPC51U68 NXP example spi_polling_b2b_transfer_slave ,64 Bytes per frame, and data starts from 0x00, 0x01 till 0x3F. I also put transfer statements into while loop.( following screen capture shows what I have changed from the original file)

3.Connect LPC1114 Pin 0.6 to LPC51U68 P0.11, and conn P0.4 on LPC51U68 to GND and power up both boards then captures transfer with Saleae.

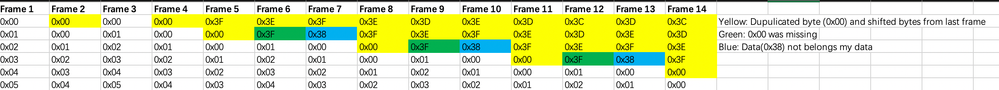

51U68 slave data always shifts header byte(1 or 2 bytes) from the second transfer in while loop.(Only 3rd frame corrects one time)

How can I fix this make SPI slave always starts from 0x0 and ends with 0x3F? Thanks a lot!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, John,

For your first question, pls refer to the link, which describes the DMA Ping-Pong mode.

For your second question, yes, if the SPI master can toggle /CS pin for each byte transfer, the spi slave byte shift issue does not appear.

hope it can help you

BR

XiangJun Rong

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, John,

Before the spi slave transfers data, you have to fill the transmitter FIFO of spi slave with dummy data, otherwise, there is issue, on the master side, you can discard the dummy data.

After you initialize the spi slave, you can use the code to fill the FIFO.

Hope it can help you

BR

Xiangjun Rong

void enableSPI(void)

{

uint8_t testIndex=10;

uint32_t ctrl = 0x70e0000;

//spi3 enable

SPI->CFG|=0x01;

//clear the transmitter and receiver FIFO

SPI->FIFOCFG|=0xC0000;

//The FIFO size is 8,

//write the dummy data to SPI slave transmitter FIFO

//The spi master has to remove the 8 dummy data

do

{

SPI->FIFOWR = ctrl|testIndex;

testIndex++;

}while(SPI->FIFOSTAT&0x20);

}

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Rong:

Thank you for your reply. After few tweaks, this code worked like a charm!!

Really appreciate for your help!

Now I have encountered a new issue for DMA SPI slave. Shall we continue discuss in this topic?

After reading the UM, I've learned DMA has a 1k buffer limit, so if I want transmit data larger than 1024, I should change the "link to next descriptor" after last descriptor is exhausted.

The example which called SPI_MasterTransferDMA(), after 1024 bytes transmit, and it stops.

So how can I manage this code to work with data like over 8k bytes?

I'm new to DMA (which LPC111x do not has this)

Thank you!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, John,

Because the DMA XFERCOUNT bits(25::16) in Channel transfer configuration registers is limited to 1024, so the DMA transfer count is limited to 1024. If the transfer data size is greater than 1024, you can reinitialize the DMA Channel transfer configuration register, and restart DMA in DMAcallback function.

BTW, for the first question that SPI slave byte shift issue, I suggest the master spi toggles /CS signal for each byte, in this way, the issue never happens.

Of course, using "link to next descriptor" is an alternative for large size data transfer.

BR

XiangJun Rong

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Rong:

Thanks for your reply!

Here’s my situation:

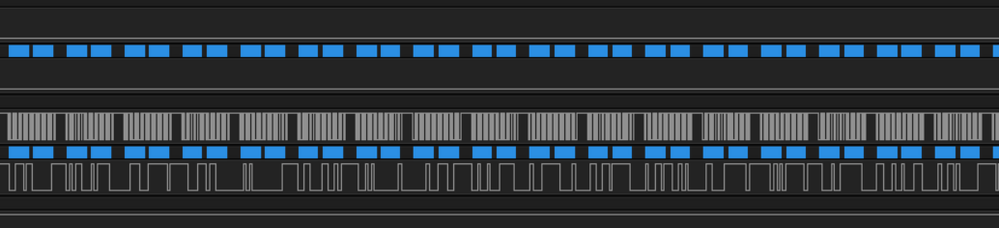

- For DMA SPI slave, I have to transmit about 8k bytes in a high clock rate(12Mhz) and almost without breaks(less than 0.3 us, as shown below) between every 2 bytes. It requires very fast respond in case of missing any data. So I think "link to next descriptor" would be a nice solution. Please help.

- Both SPI poll mode and DMA mode, the master device not came from me, I just have to adapt to it. It does not have CS signal, but I could use other GPIO pin as a trigger to pull the CS at the end of frame (not between bytes). Does this helps?

Thank you!