- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Re: IMX6 BT656 output on LCD

IMX6 BT656 output on LCD

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

IMX6 BT656 output on LCD

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I use the IMX6 with toradex apalis main board. I make a host card to use ADV7393 on the LCD interface.

I use the 2.7 linux kernel for imx6 here :

| 2.7 | toradex_4.1-2.0.x-imx |

My first attempt was to use an AD723 on the VGA output with this patch : L4.9_HDMI_Interlaced_Mode_Patch.tar.bz2 The patch apply very well but not give the result i want.

So with the ADV7393 i want to use this patch : L3.0.35_4.1.0_GA_bt656_output_patch_2017-03-10.zip

but the patch don't apply due to files not exist...

Example : the file imx6_defconfig doesn't exist only apalis_imx6_defconfig

How can i found a patch for my kernel with ADV7393 support.

adv@adv-VirtualBox:~/linux-toradex$ sudo git am 0001-Support-BT656-and-BT1120-output-for-iMX6-ipuv3.patch

[sudo] password for adv:

Applying: Support BT656 and BT1120 output for iMX6 ipuv3.

.git/rebase-apply/patch:41: trailing whitespace.

.ipu_id = 0,

.git/rebase-apply/patch:42: trailing whitespace.

.disp_id = 0,

.git/rebase-apply/patch:282: trailing whitespace.

.git/rebase-apply/patch:296: trailing whitespace.

.git/rebase-apply/patch:479: trailing whitespace.

static void _ipu_dc_setup_bt656_interlaced(struct ipu_soc *ipu,

error: arch/arm/configs/imx6_defconfig: does not exist in index

error: arch/arm/mach-mx6/board-mx6q_sabresd.c: does not exist in index

error: arch/arm/mach-mx6/devices-imx6q.h: does not exist in index

error: arch/arm/plat-mxc/include/mach/ipu-v3.h: does not exist in index

error: drivers/media/video/mxc/output/mxc_vout.c: does not exist in index

error: patch failed: drivers/mxc/ipu3/ipu_common.c:356

error: drivers/mxc/ipu3/ipu_common.c: patch does not apply

error: patch failed: drivers/mxc/ipu3/ipu_disp.c:47

error: drivers/mxc/ipu3/ipu_disp.c: patch does not apply

error: patch failed: drivers/mxc/ipu3/ipu_regs.h:706

error: drivers/mxc/ipu3/ipu_regs.h: patch does not apply

error: drivers/video/mxc/Kconfig: does not exist in index

error: drivers/video/mxc/Makefile: does not exist in index

error: drivers/video/mxc/mxc_ipuv3_fb.c: does not exist in index

error: patch failed: include/linux/ipu.h:97

error: include/linux/ipu.h: patch does not apply

error: patch failed: include/linux/mxcfb.h:153

error: include/linux/mxcfb.h: patch does not apply

Patch failed at 0001 Support BT656 and BT1120 output for iMX6 ipuv3.

The copy of the patch that failed is found in: .git/rebase-apply/patch

When you have resolved this problem, run "git am --continue".

If you prefer to skip this patch, run "git am --skip" instead.

To restore the original branch and stop patching, run "git am --abort".

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

With the patch L4.9_HDMI_Interlaced_Mode_Patch.tar.bz2 based on your patch :

https://community.nxp.com/docs/DOC-100657

I have a picture on my display but i have some glitch.

video with gstreamer

NTSC gstreamer glitch - YouTube

The configuration is :

setenv vidargs video=mxcfb0:dev=lcd,LCD-480I60,if=RGB24,bpp=32 video=mxcfb1:off video=mxcfb2:off video=mxcfb3:off fbmem=32M

The ADV7393 is configured with an fpga with the table 77 of his datasheet.

i2c_register_full_write(0x17,0x02); i2c_register_full_write(0x00,0x1C); i2c_register_full_write(0x01,0x00); i2c_register_full_write(0x80,0x10); i2c_register_full_write(0x82,0xCB); i2c_register_full_write(0x87,0x80); i2c_register_full_write(0x88,0x10); i2c_register_full_write(0x8A,0x0C);

Do you have any idea how i can resolve my problem.

I think this is due to the Apalis/IMX6 because i have an occured error which coincide with the glitch.

[ 3641.557302] mxc_sdc_fb fb@0: 1440x480 h_sync,r,l: 124,38,114 v_sync,l,u: 6,8,31 pixclock=27000000 Hz

[ 3641.673368] mxc_sdc_fb fb@0: 1440x480 h_sync,r,l: 124,38,114 v_sync,l,u: 6,8,31 pixclock=27000000 Hz

[ 3641.793425] mxc_sdc_fb fb@0: 1440x480 h_sync,r,l: 124,38,114 v_sync,l,u: 6,8,31 pixclock=27000000 Hz

[ 3647.268810] mxc_sdc_fb fb@0: 1440x480 h_sync,r,l: 124,38,114 v_sync,l,u: 6,8,31 pixclock=27000000 Hz

[ 3647.317294] mxc_sdc_fb fb@0: 1440x480 h_sync,r,l: 124,38,114 v_sync,l,u: 6,8,31 pixclock=27000000 Hz

[ 3647.416656] mxc_sdc_fb fb@0: 1440x480 h_sync,r,l: 124,38,114 v_sync,l,u: 6,8,31 pixclock=27000000 Hz

[ 3647.533398] mxc_sdc_fb fb@0: 1440x480 h_sync,r,l: 124,38,114 v_sync,l,u: 6,8,31 pixclock=27000000 Hz

Regards.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The LCD-480I60 is for 1440*480i60, for adv7393, I think you can use LCD-NTSC mode.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

HI Qiang_FSL

I tried this config from the other patch L3.0.35_4.1.0_GA_bt656_output_patch_2017-03-10.zip :

"LCD-PAL", 50, 720, 576, 37037, 22, 2, 23, 2, 288, 1,

0,

FB_VMODE_INTERLACED,

FB_MODE_IS_DETAILED,},

But that make this error:

[ 146.620958] imx-ipuv3 2400000.ipu: IPU Warning - IPU_INT_STAT_10 = 0x00100000

[ 146.711483] imx-ipuv3 2400000.ipu: IPU Warning - IPU_INT_STAT_5 = 0x00800000

[ 146.711492] mxc_sdc_fb fb@0: 720x576 h_sync,r,l: 288,2,22 v_sync,l,u: 1,2,23 pixclock=27000000 Hz

The output frequency is good. Do you think this is a possible solution if i resolve the error?

Error meaning :

IPU_INT_STAT_5[23] IDMAC IDMAC_NFB4EOF_ERR_23 YES -

IPU_INT_STAT_10[20] DI1 DI1_SYNC_DISP_ERR YES -

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The patch "L3.0.35_4.1.0_GA_bt656_output_patch" is used for BT656 interface, which just used 1 clock and 9 data lines, no signals output from VSYNC and HSYNC, you can't use that timing parameter to the "L3.0.35_4.1.0_GA_HDMI_Interlaced_Mode_Patch".

The "L3.0.35_4.1.0_GA_HDMI_Interlaced_Mode_Patch" is used for VSYNC+HSYNC+Pixel clock mode, and it is used for 16bits data line interface.

They are two different use case. Based on your hardware interface, you need select the correct patch.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I Qiang_FSL

I've read this description for L3.0.35_4.1.0_GA_bt656_output_patch.

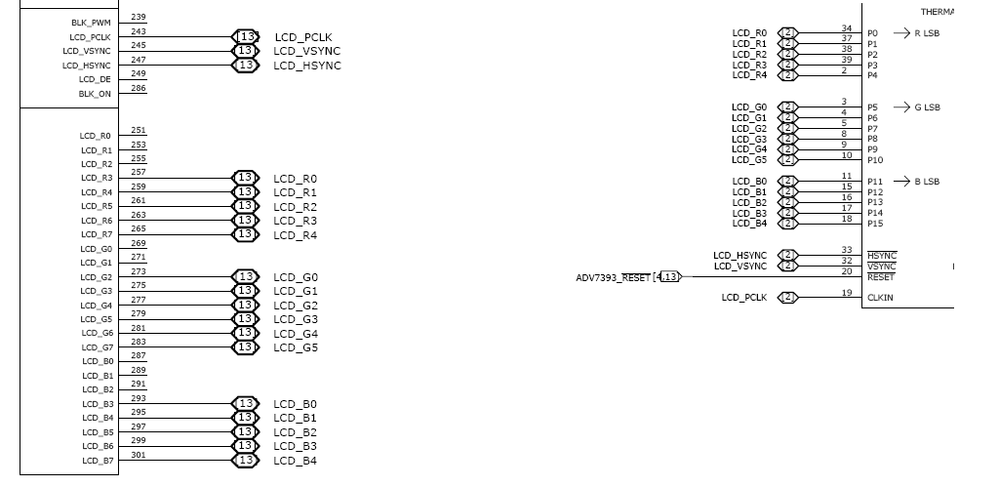

"L3.0.35_1.1.0_GA_bt656_output_patch.zip" is the patch for Freescale L3.0.35_1.1.0_GA_iMX6DQ BSP. "r13.4.1_bt656_output_patch.zip" is the patch for Freescale Android R13.4.1 BSP.1. Features supported: 1) Support BT656(8 bits) and BT1120 (16 bits)interlaced output on display port.2) Support both RGB and YUV frame buffer for BT656/BT1120 output.3) Support PAL and NTSC mode.4) Support on the fly switch between PAL and NTSC mode.5) Support CVBS output based on adv7391 TV encoder.2. Hardware link between iMX6 and adv7391 TV encoder chip.IPU1_DI0_DISP_CLK connected to adv7391 CLKIN pin.IPU1_DISP0_DAT_23~DISP0_DAT_16 connected to adv7391 P7~P0 pins.IPU1_DI0_PIN2 connected to adv7391 HSYNC pin. (option)IPU1_DI0_PIN4 connected to adv7391 VSYNC pin. (option)

That's my hardware:

PCLK connected => need 27MHz pix clock to work

HSYNC VSYNC connected

16 bits data line interface

But i can't apply this patch on my kernel.

So i tried this one L3.0.35_4.1.0_GA_HDMI_Interlaced_Mode_Patch which is easy to modified for my kernel.

And I used it with the AD723.

Can we pay for your support?

I think I'm very close but I do not have the skill for the end of the job

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

For your 16 bits data line + HSYNC + VSYNC + pixel clock use case, I think you can use the L3.0.35_4.1.0_GA_HDMI_Interlaced_Mode_Patch. But you need select a video mode for your AD723.

For 27M pixel clock, the followed two modes can be tried:

{

/* 1440x576i @ 50 Hz , pixel clk @ 27MHz */

"LCD-576I50", 50, 1440, 576, 37037, 138, 24, 39, 4, 126, 6,

0,

FB_VMODE_INTERLACED,

0,},

/* 1440x480i @ 60 Hz , pixel clk @ 27MHz */

"LCD-480I60", 60, 1440, 480, 37037, 114, 38, 31, 8, 124, 6,

0,

FB_VMODE_INTERLACED,

0,},

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

thats exactly what i've done.The result is not good.

i have an IMU information message with glitch in video output:

video with gstreamer

NTSC gstreamer glitch - YouTube

The configuration is :

setenv vidargs video=mxcfb0:dev=lcd,LCD-480I60,if=RGB24,bpp=32 video=mxcfb1:off video=mxcfb2:off video=mxcfb3:off fbmem=32M

The ADV7393 is configured with an fpga with the table 77 of his datasheet.

i2c_register_full_write(0x17,0x02); i2c_register_full_write(0x00,0x1C); i2c_register_full_write(0x01,0x00); i2c_register_full_write(0x80,0x10); i2c_register_full_write(0x82,0xCB); i2c_register_full_write(0x87,0x80); i2c_register_full_write(0x88,0x10); i2c_register_full_write(0x8A,0x0C);

Do you know where i can make a mistake?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

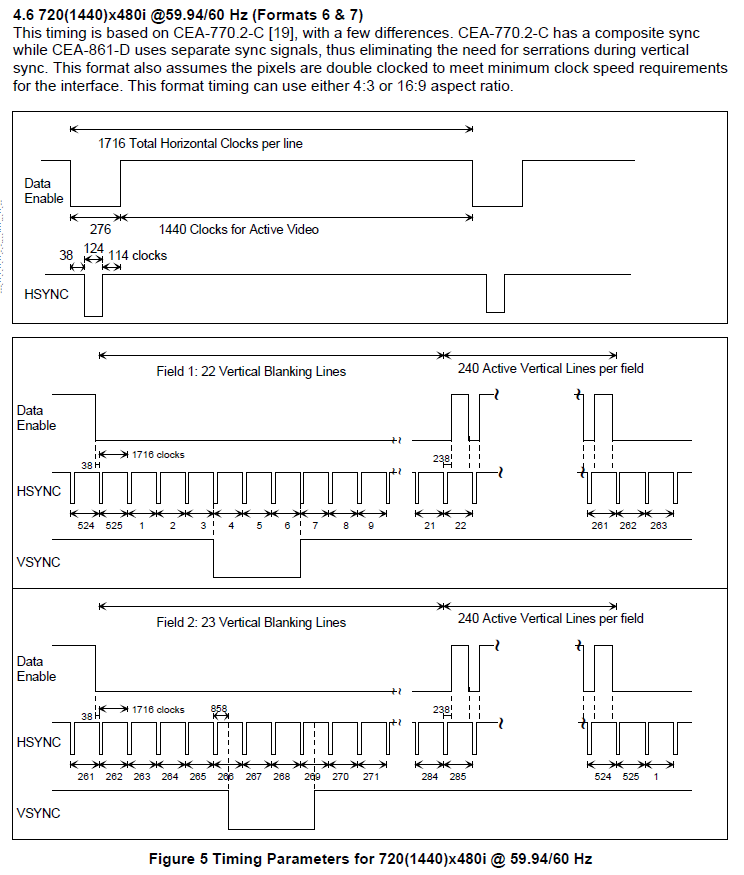

The current LCD-480I60 (1440*480i60) display mode is from CEA-861 specification, "720(1440)x480i @59.94/60 Hz (Formats 6 & 7)". I think you need check with adv7393 vendor and measure the signals to identify why it can't work.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for your reply

that's because the CEA-861 is not in the standard suported by ADV7393.

The list is here :

ITU-R BT.601/656

NTSC square pixel

PAL square pixel

SMPTE 293M

BTA T-1004

ITU-R BT.1358

ITU-R BT.1358

ITU-R BT.1362

ITU-R BT.1362

Do you think i can go to one of this standard with the L3.0.35_4.1.0_GA_HDMI_Interlaced_Mode_Patch patch and updating the timing parts ?

(i get the example timing in the L3.0.35_4.1.0_GA_bt656_output_patch patch but we have already said that it can not work.)

{

/* 1440x576i @ 50 Hz , pixel clk @ 27MHz */

"LCD-576I50", 50, 1440, 576, 37037, 138, 24, 39, 4, 126, 6,

0,

FB_VMODE_INTERLACED,

0,},+ /* PAL Interlaced output */

+ "BT656-PAL", 50, 720, 576, 37037,

+ 22, 2,

+ 23, 2,

+ 288, 1,

+ FB_SYNC_HOR_HIGH_ACT | FB_SYNC_VERT_HIGH_ACT,

+ FB_VMODE_INTERLACED,

+ FB_MODE_IS_DETAILED,},

Can we pay for this driver development?

Regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

No, you can't use the timing parameters from L3.0.35_4.1.0_GA_bt656_output_patch. That is not the standard timing parameters.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I understand what i can not do.

But i don't know what i can...

For information when i used the L3.0.35_4.1.0_GA_HDMI_Interlaced_Mode_Patch patch the 27MHz clock is not stabilized.

With LCD-576I50 or LCD-480I60 i have warning.

The video is not that bad when the ipu work.(youtube video)

How can i know the error source?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

In normal case, you need adjusting the timing parameters to meet your TVin chip's requirement. You'd better get the required waveform from vendor, then measure the current waveform to identify the issue.

Use CEA-861 as example:

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I take a look on the signal generated by 1440x480 and the first change i need to make is not only parameter in "mxc_lcdif.c" file

The ADV7393 datasheet "Figure 6. SD Input, 16-Bit 4:4:4 RGB, Input Mode 000" show that RBG shall be change at 13.5MHz with clock at 27MHz and HSYNC/VSYNC synchronized on this 27MHz clock.

Do you think i can change the width parameter in active pixel?

+ /* Active Pixel */

+ apixel_cnt = DI_SYNC_APIXEL;

+ _ipu_di_sync_config(ipu,

+ disp, /* display */

+ DI_SYNC_APIXEL, /* counter */

+ 0, /* run count */

+ DI_SYNC_CLK, /* run_resolution */

+ h_start_width + h_sync_width, /* offset */

+ DI_SYNC_CLK, /* offset resolution */

+ width, /* repeat count */ => 2* width

+ DI_SYNC_ALINE, /* CNT_CLR_SEL */

+ 0, /* CNT_POLARITY_GEN_EN */

+ DI_SYNC_NONE, /* CNT_POLARITY_CLR_SEL */

+ DI_SYNC_NONE, /* CNT_POLARITY_TRIGGER_SEL */

+ 0, /* COUNT UP */

+ 0 /* COUNT DOWN */

+ );

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The clock repeat mode (two pixel clocks transfer one pixel data is not supported in IPU driver), but from hardware interface, it should be the same signals with 1440*480@27MHz

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thx for the reply,

I tried this because you write that :

CEA format 5: 1920x1080i @60Hz

CEA format 6&7: 720(1440)x480i @60Hz

CEA format 20: 1920x1080i @50Hz

CEA format 21&22: 720(1440)x576i @50Hz

i tried the LCD-NTSC mode but no video output.

i think is because the pixel clock is 13.5MHz

+ /* 720x480i @ 60 Hz , pixel clk @ 13.5MHz */

+ "LCD-NTSC", 60, 720, 480, 74074, 114, 38, 31, 8, 124, 6,

+ 0,

+ FB_VMODE_INTERLACED,

+ 0,},

For me is more an ipu stability issue.

The glitch and the error message are related.

Q1 : Which input should be the easier to generate?

Active Resolution I/P1 Frame Rate (Hz) Clock Input (MHz) Standard

720 × 480 I 29.97 27 ITU-R BT.601/656

720 × 576 I 25 27 ITU-R BT.601/656

640 × 480 I 29.97 24.54 NTSC square pixel

768 × 576 I 25 29.5 PAL square pixel

I tried the first 2, but maybe the 2 others are easier to generate...

Q2 :

Do you think i can make something like this?

+ /* 1440x480i @ 60 Hz , pixel clk @ 27MHz */

+ "LCD-480I60", 60, 1440, 480, 37037, 114, 38, 31, 8, 124, 6,

+ 0,

+ FB_VMODE_INTERLACED,

+ 0,},

=>

+ /* 720x480i @ 30 Hz , pixel clk @ 27MHz */

+ "LCD-480I60", 30, 720, 480, 37037, 114, 38, 31, 8, 124, 6,

+ 0,

+ FB_VMODE_INTERLACED,

+ 0,},

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi morel

toradex boards and software are supported by toradex support and one can find answers for adv7393 :

IMX6Q carrier board design - Toradex Community

There are some third party software which has ADV7393 support, for example

openwrt_rtk/imx6dl-gw53xx.dts at master · cgoder/openwrt_rtk · GitHub

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Igor,

Sorry but the two links doesn't help me :

the first link is me asking for support on toradex,

the second link, i don't understand the use of it .

I don't remember where i find my patch L4.9_HDMI_Interlaced_Mode_Patch.tar.bz2

Now they provide L3.0.35_4.1.0_GA_HDMI_Interlaced_Mode_Patch_2016-05-20.zip which seem to do the same but it's not compatible with my apalis...