- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- Product Forums

- :

- MPC5xxx

- :

- TXBRP is in Pending state

TXBRP is in Pending state

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

TXBRP is in Pending state

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

After ‘M_CAN_1.TXBAR.R = 0x1;’, the M_CAN_1.TXBRP.R value is always 1, and M_CAN_1 send nothing.

I transplant the code Example MPC5777M MCAN simple TX/RX GHS614 on S32ds, I check many times, but find no register config problem. I have studied MPC5777M RM for TXBRP register.Still I am not able to understand why it is becoming.PetrS

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

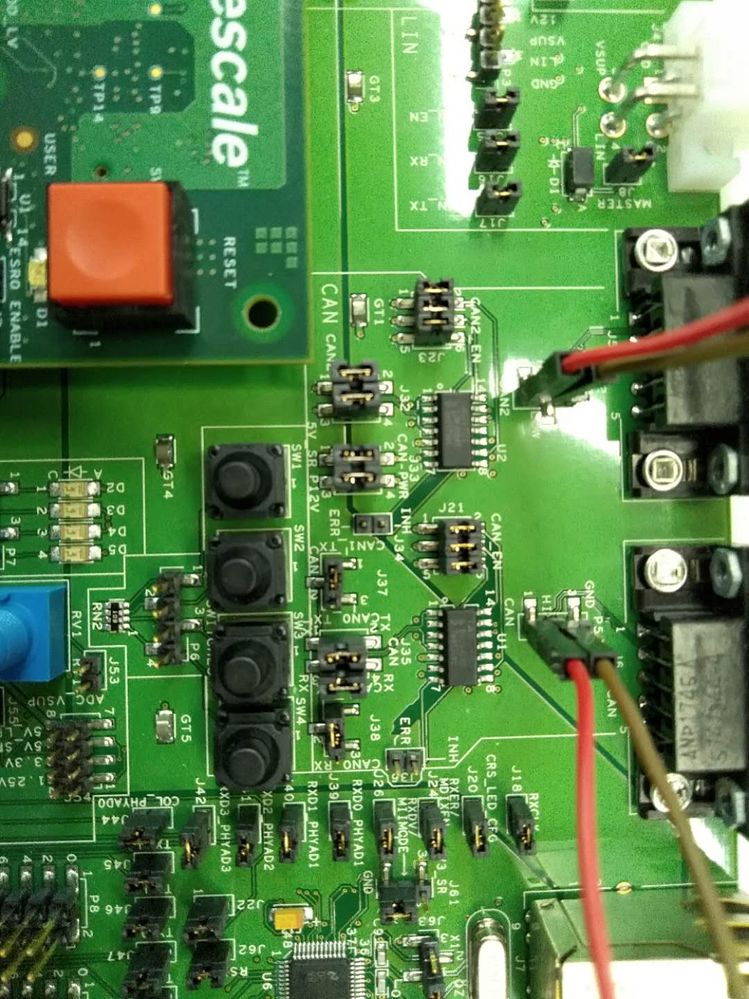

I met the same problem when I debug the Example MPC5777M MCAN simple TX/RX GHS614 in the SRAM on MPC57xx Motherboard.

I debug this project in S32DS.

I added other module like LINFlex_Uart in this project , and it works normally , so I confirmed the project debug correctly.

Then I set the MCAN1 as external loop back mode , it works normally . I measured MCAN1TX and MCAN1 RX when I using Oscilloscope , I get the same wave in MCAN1RX and MCAN1TX , according to MCAN section in MPC577M RM , it seems like working correctly in external loopback mode.

But when I connect the MCAN1 TX RX and MCAN2 TX RX pin to TJA1041T , I met the same problem like the author met . The MCAN1 TX is pending when I send the second frame. And the MCAN TX and RX have no wave . The CANH and CANL pin keep 2.5V all the time.

I measured the VI/O , VBAT , VCC, WAKE , STB , EN pin voltage in two TJA1041T on board , it seems nothing unnormal.

I try to set baudrate as 250kbps , 500kbps , nothing changed.

I guess it may be a HW problem , then I change another board , but I get the same appearance.

Please give me some advice checking the problem ,Thx!!!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I try to fix this problem for a week. Maybe I have sloved this problem. But it's confused me. b55689 PetrS may I have your help?

1. According to debug on MPC5777M EVB, I found that M_CAN_1.CCCR.B.INIT will be set as 1 while start sending first MCAN msg with M_CAN_1.TXBAR.R = 0x01 command, I add some code to reset M_CAN_1.CCCR.B.INIT, but it can't work while ECR, IR show many errors.

2. I have no idea about this. So I re plug J21 and J23 because there is EN port of transceivers. I re debug on board, and MCAN codes works on board.

3. Once this problem appears again. I can fix it by 2 step. After fixing it for several times, I found thart sometiomes it is repeatable after power off. But most of time it works fine. very strange. i find no rules for now.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

it seems that sometimes after power on the TJA1041 on the EVB detects a failure or similar and so disable transmitter. The MCAN module then detects a bit error and goes to Bus Off and stays in Init mode.

You should check the local failures flags on ERR output of the transceiver and clear it if needed so the transmitter can be enabled again. The /STB and EN pin of the transceiver are used for this purpose. See more in TJA1041 datasheet http://www.nxp.com/documents/data_sheet/TJA1041.pdf and AN00094http://www.nxp.com/documents/application_note/AN00094.pdf.

Once this is done, MCAN can enter normal mode again.

BR, Petr

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I'm confused for several days, I transplant from Example MPC5777M MCAN simple TX/RX GHS614 , but it can't work on MPC5777M EVB

void SysClk_Init(void)

{

MC_CGM.AC3_SC.B.SELCTL = 0x01; //connect XOSC to the PLL0 input

MC_CGM.AC4_SC.B.SELCTL = 0x01; //connect XOSC to the PLL1 input// Set PLL0 to 300 MHz with 40MHz XOSC reference

PLLDIG.PLL0DV.R = 0x4002100F; // PREDIV = 1, MFD = 15, RFDPHI = 2, RFDPHI1 = 8MC_ME.RUN_MC[0].R = 0x00130070; // RUN0 cfg: IRCON,OSC0ON,PLL0ON,syclk=IRC

// Mode Transition to enter RUN0 mode:

MC_ME.MCTL.R = 0x40005AF0; // Enter RUN0 Mode & Key

MC_ME.MCTL.R = 0x4000A50F; // Enter RUN0 Mode & Inverted Key

while (MC_ME.GS.B.S_MTRANS) {}; // Wait for mode transition to complete

while(MC_ME.GS.B.S_CURRENT_MODE != 4) {}; // Verify RUN0 is the current mode// Set PLL1 to 600 MHz with 40MHz XOSC reference

PLLDIG.PLL1DV.R = 0x0001001E; // MFD = 30, RFDPHI = 1MC_ME.RUN_PC[0].R = 0x000000FE; // enable peripherals run in all modes

MC_ME.RUN_MC[0].R = 0x001300F4; // RUN0 cfg: IRCON, OSC0ON, PLL1ON, syclk=PLL1MC_CGM.SC_DIV_RC.R = 0x00000001; //! System clock divider ratios will change with next update. Not required for Cut 1.

MC_CGM.DIV_UPD_TYPE.R = 0x80000000; //! System clock divider ratios updated on writing MC_CGM.DIV_UPD_TRIG. Not required for Cut 1.MC_CGM.SC_DC2.R = 0x800B0000; // PBRIDGEA/PBRIDGEB_CLK at syst clk div by 12 ... (50 MHz)

MC_CGM.SC_DC1.R = 0x80050000; // SXBAR_CLK at syst clk div by 6 ... (100 MHz)

MC_CGM.SC_DC0.R = 0x80020000; // FXBAR_CLK, BD_CLK, IOP_CLK at syst clk div by 3 (200 MHz)

MC_CGM.SC_DC3.R = 0x80010000; // COMP/CHKR_CLK at syst clk div by 2 ... (300 MHz)

MC_CGM.SC_DC4.R = 0x800A0000; // CLKOUT at syst clk div by 11 ... (54.55 MHz)MC_CGM.DIV_UPD_TRIG.R = 0xfeedface; //! System clock divider ratio updates triggered. Not required for Cut 1.

while (MC_CGM.DIV_UPD_STAT.B.SYS_UPD_STAT == 1) //! Wait for System Clock Divider Update Status == 0. Not required for Cut 1.

{}

MC_ME.PCTL15.R = 0;

MC_ME.PCTL70.R = 0;

MC_ME.PCTL69.R = 0;

MC_ME.PCTL74.R = 0;// Mode Transition to enter RUN0 mode:

MC_ME.MCTL.R = 0x40005AF0; // Enter RUN0 Mode & Key

MC_ME.MCTL.R = 0x4000A50F; // Enter RUN0 Mode & Inverted Key

while (MC_ME.GS.B.S_MTRANS) {}; // Wait for mode transition to complete

while(MC_ME.GS.B.S_CURRENT_MODE != 4) {}; // Verify RUN0 is the current modeMC_CGM.AC0_SC.R = 0x02000000; // Select PLL0 for auxiliary clock 0

MC_CGM.AC0_DC0.R = 0x80050000; // PER_CLK : Enable aux clk 0 div by 6 (50 MHz)

MC_CGM.AC8_SC.R = 0x01000000; // Select XOSC for auxiliary clock 8

MC_CGM.AC8_DC0.R = 0x80000000; // CAN_CLK : Enable aux clk 8 div by 1 (40 MHz)

}static void MCAN_MSG_RAM_Init(void)

{

int i;

uint32_t *pMsgRAM = (uint32_t*)MCAN_MSG_RAM_BASE_ADDR;for(i=0;i<MCAN_MSG_RAM_LENGTH/4;i++)

{

*pMsgRAM++ = 0x0;

}

}static void M_CAN_1_Init(void)

{

/* 1. put module to Init mode*/M_CAN_1.CCCR.B.INIT = 0x1;

while(M_CAN_1.CCCR.B.INIT == 0)

{}

//2. enable CCE bit to change config

M_CAN_1.CCCR.B.CCE = 0x1;

while(M_CAN_1.CCCR.B.CCE==0)

{}

M_CAN_1.CCCR.B.CMR = 0x0; //No CAN FD

M_CAN_1.CCCR.B.CME = 0x0;//M_CAN_1.BTP.R = 0x00011E77; // Set time quanta for 0.5Mbps SYNC=1, TSEG1=30+1, TSEG2=7+1, SJW=7+1

M_CAN_1.BTP.R = 0x000117DD; // Set time quanta for 0.5Mbps SYNC=1, TSEG1=23+1, TSEG2=13+1, SJW=13+1

M_CAN_1.GFC.R = (0

| 3<<4 // Reject non-matching standard frames in Rx FIFO 0

| 3<<2 // Reject non-matching extended frames in Rx FIFO 1

| 1<<1 // Reject Remote Frames Standard

| 1); // Reject Remote Frames Extended

M_CAN_1.TXBC.R = (0 // tx buffer

| 2 << 16 // space for 2 messages

| MCAN1_TXBC_TBSA); // starting at offset MCAN0_TXBC_TBSAM_CAN_1.RXESC.R = 0x00000000; //set for 8 data bytes both RX FIFO 0 and FIFO 1

M_CAN_1.TXESC.R = 0x00000000; //set for 8 data bytes tx bufferM_CAN_1.CCCR.B.CCE = 0x0;

M_CAN_1.CCCR.B.INIT = 0x0; //re-enable CCCR protection

while((M_CAN_1.CCCR.R & 0x1)==1)

{}

}static void M_CAN_2_Init(void)

{// put module to Init mode

M_CAN_2.CCCR.B.INIT = 0x1;

while(M_CAN_2.CCCR.B.INIT == 0)

{}

// enable CCE bit to change config

M_CAN_2.CCCR.B.CCE = 0x1;

while(M_CAN_2.CCCR.B.CCE==0)

{}

M_CAN_2.CCCR.B.CMR = 0x0; //no CAN FD

M_CAN_2.CCCR.B.CME = 0x0;//M_CAN_2.BTP.R = 0x00011E77; // Set time quanta for 0.5Mbps SYNC=1, TSEG1=30+1, TSEG2=7+1, SJW=7+1

M_CAN_2.BTP.R = 0x000117DD; // Set time quanta for 0.5Mbps SYNC=1, TSEG1=23+1, TSEG2=13+1, SJW=13+1M_CAN_2.GFC.R = (0

| 0<<4 // Accept non-matching standard frames in Rx FIFO 0

| 1<<2 // Accept non-matching extended frames in Rx FIFO 1

| 1<<1 // Reject Remote Frames Standard

| 1); // Reject Remote Frames Extended

M_CAN_2.SIDFC.R = (0

| 2 << 16 // 2 standard message ID filter elements

| MCAN2_SIDFC_FLSSA); // filter list starting from offset MCAN1_SIDFC_FLSSAM_CAN_2.XIDFC.R = (0

| 2 << 16 // 2 Extended ID's filter used in this network

| MCAN2_XIDFC_FLESA); // filter list starting from offset MCAN1_XIDFC_FLESAM_CAN_2.RXF0C.R = (0

| 1 << 31 // FIFO0 overwrite

| 2 << 16 // hold 2 messages

| MCAN2_RXF0C_F0SA); // starting at offset MCAN1_RXF0C_F0SAM_CAN_2.RXF1C.R = (0

| 1 << 31 // FIFO1 overwrite

| 2 << 16 // hold 2 messages

| MCAN2_RXF1C_F1SA); // starting at offset MCAN1_RXF1C_F1SAM_CAN_2.RXESC.R = 0x00000000; //set for 8 data bytes both RX FIFO 0 and FIFO 1

M_CAN_2.TXESC.R = 0x00000000; //set for 8 data bytes tx bufferM_CAN_2.CCCR.B.CCE = 0x0;

M_CAN_2.CCCR.B.INIT = 0x0; //re-enable CCCR protection

while((M_CAN_2.CCCR.B.INIT & 0x1)==1)

{}

}

void MCAN_ID_init()

{//MCAN2 std ID table MCAN1_SIDFC_FLSSA

WRITE_MSG_RAM( MCAN2_SIDFC_FLSSA,

0 // Standard Message ID filter element 1

| 0x2<<30 // Classic filter: SFID1 = filter (ID), SFID2 = mask

| 0x1<<27 // Store in Rx FIFO 0 if filter matches

| 0x123<<16 // ID = 0x123

| 0x7FF); // mask = 0x7FF

WRITE_MSG_RAM( MCAN2_SIDFC_FLSSA + 0x04,

0 // Standard Message ID filter element 2

| 0x2<<30 // Classic filter: SFID1 = filter (ID), SFID2 = mask

| 0x1<<27 // Store in Rx FIFO 0 if filter matches

| 0x456<<16 // ID = 0x456

| 0x7FF); // mask = 0x7FF//MCAN1 ext ID table at offset MCAN2_XIDFC_FLESA

WRITE_MSG_RAM( MCAN2_XIDFC_FLESA,

0 // extended Message ID filter element 1, word F0

| 0x2<<29 // Store in Rx FIFO 1 if filter matches

| 0x123); // ID = 0x123WRITE_MSG_RAM( MCAN2_XIDFC_FLESA + 0x04,

0 // extended Message ID filter element 1, word F1

| 0x2<<30 // Classic filter: EFID1 = filter (ID), EFID2 = mask

| 0x1FFFFFFF); // mask = 0x1FFFFFFFWRITE_MSG_RAM( MCAN2_XIDFC_FLESA + 0x08,

0 // extended Message ID filter element 2, word F0

| 0x2<<29 // Store in Rx FIFO 1 if filter matches

| 0x456); // ID = 0x123WRITE_MSG_RAM( MCAN2_XIDFC_FLESA + 0x0C,

0 // extended Message ID filter element 2, word F1

| 0x2<<30 // Classic filter: EFID1 = filter (ID), EFID2 = mask

| 0x1FFFFFFF); // mask = 0x1FFFFFFF

}static void M_CAN_1_TransmitMsg(uint8_t ext, uint32_t ID, uint8_t lenght)

{

uint32_t txID;if (ext==0) txID = ID<<18;

else txID = ID;if (M_CAN_1.TXBRP.R == 0)

{int z;

WRITE_MSG_RAM( MCAN1_TXBC_TBSA,

0 // Tx Buffer 0 T0 word

| ext<<30 // standard ID

| 0<<29 // transmit data frame

| txID); // message IDWRITE_MSG_RAM( MCAN1_TXBC_TBSA + 4,

0 // Tx Buffer 0 T1 word

| 0<<23 // do not store TX event

| (lenght << 16)); // dlc... data lengthfor(z = 0; z < lenght; z+=4) // fill rest of Tx Buffer 0 Tn words with data

{

WRITE_MSG_RAM( MCAN1_TXBC_TBSA + 8 + z, M_CAN_1_data[z] | (M_CAN_1_data[z+1]<<8) | (M_CAN_1_data[z+2]<<16) | (M_CAN_1_data[z+3]<<24));

}M_CAN_1.TXBAR.R = 0x1; // start transmission for M_CAN0 TX buffer 0

}

}static void M_CAN_2_Read_RXFIFO(uint8_t fifo)

{

uint32_t temp = 0;

uint8_t dlc,i=0,j=3;

uint8_t get_index; // index of FIFO element to be read

uint16_t fifo_item_offset ; // real offset in msg RAM, 2 word + 8 bytes of data

uint8_t *pRXdata = &M_CAN_2_data[0];if(fifo)

{

get_index = M_CAN_2.RXF1S.B.F1GI; // index of FIFO element to be read

fifo_item_offset = MCAN2_RXF1C_F1SA + 16 * get_index; // real offset in msg RAM, 2 word + 8 bytes of data

}

else

{

get_index = M_CAN_2.RXF0S.B.F0GI; // index of FIFO element to be read

fifo_item_offset = MCAN2_RXF0C_F0SA + 16 * get_index; // real offset in msg RAM, 2 word + 8 bytes of data

}// read message word R0 from RXFIFO 0

temp = READ_MSG_RAM( fifo_item_offset + 0);

// read message word R1 from RXFIFO 0

temp = READ_MSG_RAM( fifo_item_offset + 4);dlc = (temp&0x000F0000)>>16; // get number of received bytes

while(dlc--) // read dlc bytes from FIFO

{

*pRXdata++ = READ_MSG_RAM_8bit( fifo_item_offset + 8 + i + j);

if(j==0) j=4,i+=4;

j--;

}if(fifo) M_CAN_2.RXF1A.R = get_index; // acknowledge the reading of RXFIFO "get_index" element

else M_CAN_2.RXF0A.R = get_index; // acknowledge the reading of RXFIFO "get_index" element/* do someting with the received data */

/* drive the output pin with the received data */

SIUL2.GPDO[4].R = M_CAN_2_data[0];

}