- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- QorIQ Processing Platforms

- :

- QorIQ

- :

- Re: ls1020a disable SERDES module

ls1020a disable SERDES module

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

ls1020a disable SERDES module

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

connect SerDes PLL1 and SerDes PLL2 to GND,the ls1020 boot failure.

or

set the RCW control word like this,1020 boot failure too.

#PBL preamble and RCW header

aa55aa55 01ee0100

#enable IFC, disable QSPI and DSPI

bit0-127

0608000c 00000000 00000000 00000000

bit128-255

FF000000 08C08028 60040a00 81046000

(00000000 08408028 60040a00 81046000,the configration of RCW bit128 to255,normal boot )

00000000 00000000 00000000 0002a800

80000100 0004b548 00000000 00000000

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Have a great day,

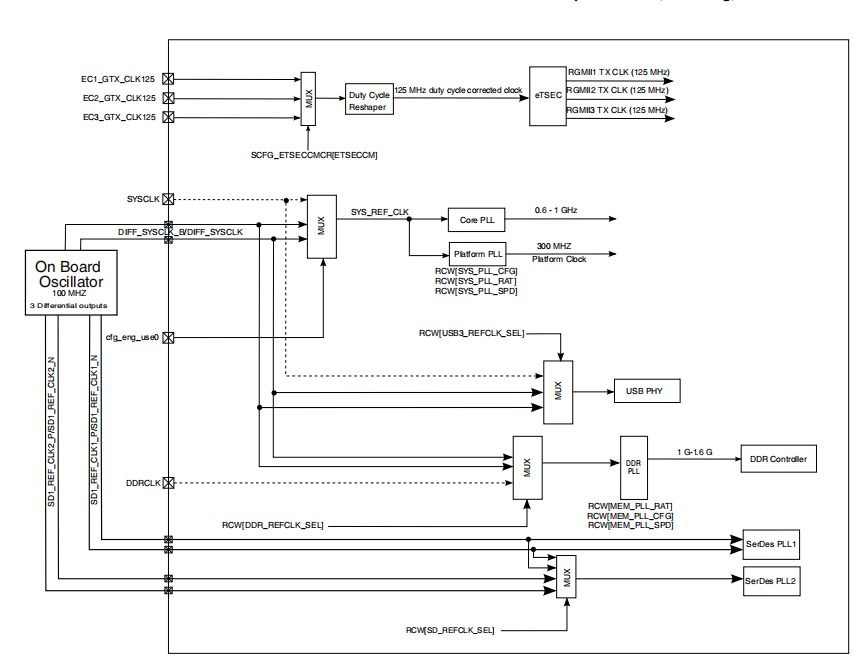

If the SerDes are unused, the SD1_REF_CLK inputs can be connected to GND, however AVDD_SD1_PLL1, AVDD_SD1_PLL2, S1VDD, X1VDD must remain powered. In the RCW configuration the following RCW bits have to be configured:

SRDS_PLL_PD_S1 = 2'b11 (both PLLs configured as powered down)

SRDS_PLL_REF_CLK_SEL_S1 = 2'b00

SRDS_PRTCL_S1=8'hFF (no other values are permitted when both PLLs are powered down)

As you can see in the https://community.nxp.com/thread/430180 LS1021 can boot with that settings. So the LS1020 should boot too.

It is not clear what do you mean as boot fail. Notice if SerDes in use then after completing reset, software should check the SerDesx_PLLnRSTCTL[RST_DONE] field to make sure that each active SerDes PLL on the device has locked. SerDes PLL will not lock if the corresponding reference clock is not provided. May your software fails due to that checking.

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

thanks for your reply。

after PBL load the RCW and PBI,the sinal ASLEEP assert。

this boot failure was related to the PBI command(8940007C 21F47300)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi ,I found the similar problem in community,

but it's no reply:smileysad: