- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- Product Forums

- :

- ColdFire/68K Microcontrollers and Processors

- :

- Re: Best sequence for MCF5484 when initializing SDR SDRAM

Best sequence for MCF5484 when initializing SDR SDRAM

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Best sequence for MCF5484 when initializing SDR SDRAM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I've got an existing design using a MCF5484 that has been working fine for many years. Unfortunately, the Micron SDR SDRAM that we were using is now obsolete. We switched to an ISSI part and now have intermittent problems.

We are using two 256Mb, 4Mx16x4 parts with control and address wired in parallel to provide a 32 bit bus. My colleague has taken scope measurements of the SDRAM signals at power-up which show an attempt to program the MODE register in the SDRAM as the first activity on the bus. The data sheets for both SDRAM parts show that we should NOT be programming this register that early.

One thing that is puzzling to us is that we don't write to the ColdFire register that should program the MODE register until later in the startup sequence. What could cause this? Could it be happening when we program the chip select?

Since this design works with the Micron part and occasionally fails with ISSI, I suspect that the parts are reacting differently to something in the start-up sequence.

What is the best order to program the SDRAM registers?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

> Since this design works with the Micron part and occasionally fails with ISSI,

Don't assume that that difference that you're seeing is the cause of the problems you're having.

If you think there's a problem with the initialisation, you should be able to repeat it. Make the initialisation sequence run twice (or more) and see if the system works after the later sequences.

Concerning the "writing to the mode register" that you're seeing. Does it do this from cold power-up and/or soft reset? We had a problem (detailed as the second one below) where the SDRAM controller generated illegal cycles on cold power-up, but was OK on normal resets.

We've experienced multiple problems with SDRAM startup, in our case on MCF5329.

Most SDRAM on the planet is in PCs and laptops. Their Boots take a long time to start up, and probably don't start using the SDRAM immediately after initialising it. So we found the following was necessary for reliable operation:

/* Do a read from RAM */

/* NOTE! This is a hack until the issue is better understood!

Without this read here, some boards read corrupt values out

of RAM on the first burst read. If the first burst read is

when the code is being executed from RAM then corrupt

instructions are read and an illegal instruction occurs.

*/

That's probably not your problem, but it is worth adding some extra "exercise" of the chips before using them for real.

The second problem was detailed in a post on this forum, which I'll now have to search for ...

MCF5329 (MCF5xxx) + SDR DRAM = lockup, anyone else?

The problem we experienced was that the DDRAM Controller inside the CPU IS NOT INITIALISED with the Reset pin. It seems to wake up in a "random mode" and requires clocks (from the crystal) to be fed into it before it will clock itself out of whatever random state it powered up in to its "normal" state. During that time it can clock illegal commands into the SDRAM. Which can then lock up, jam the bus and do whatever it likes. As long as the power supply to the CPU is below 2.0 to 2.6V the SDRAM controller pins are tri-stated, and you can rely on external pullups or pulldowns (on CK and CKE) to keep the SDRAM chip happy. Then you have to get the EVDD power supply to 3.0V (for the oscillator to start) before it gets to 2.0V (for the pins to come out of tri-state), which is tricky to say the least.

This is compounded with the MCF5329 as the Flash and SDRAM share the same data bus. So when the SDRAM controller send bad signals to the SDRAM, it can then jam the data bus, which prevents the CPU from reading instructions from the Flash, and so it crashes. A recommended fix for this problem is to use the "split data bus" with Flash on one half and RAM on the other, with half the bandwidth available.

I wrote a 41-page report on this problem back in 2010.

You're using a different chip, so its SDRAM controller may not have the same problems.

Here's another instance of the same problem with a different chip from 2007:

https://community.nxp.com/message/26423

The third problem had failures with Micron SDRAM chips, but ISSI ones worked OK. This turned out to be due to the MCF5329's undocumented drive-strength settings. At the default level (which we left it as as the settings weren't listed in the manual, and still aren't) the signals were too "aggressive" and caused overshoot and undershoot. This caused the SDRAMs to lose data. Writing all-zeros to an all-ones address triggered the problem pretty much instantly, with "the number of ones-bits" being the deciding factor. 26 ones didn't fail, but it got progressively worse going from 27 to 32.

MCF5329 with random SDRAM 1k "bit rot" corruptions

I find I've written this sort of response before, so you might like to read these ones:

Troubleshooting DDR2 RAM problems

Does your chip have an undocumented "Duty Cycle Corrector" like the one in the above post had? Turning that off fixed their problem.

Let us know what you find.

Tom

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

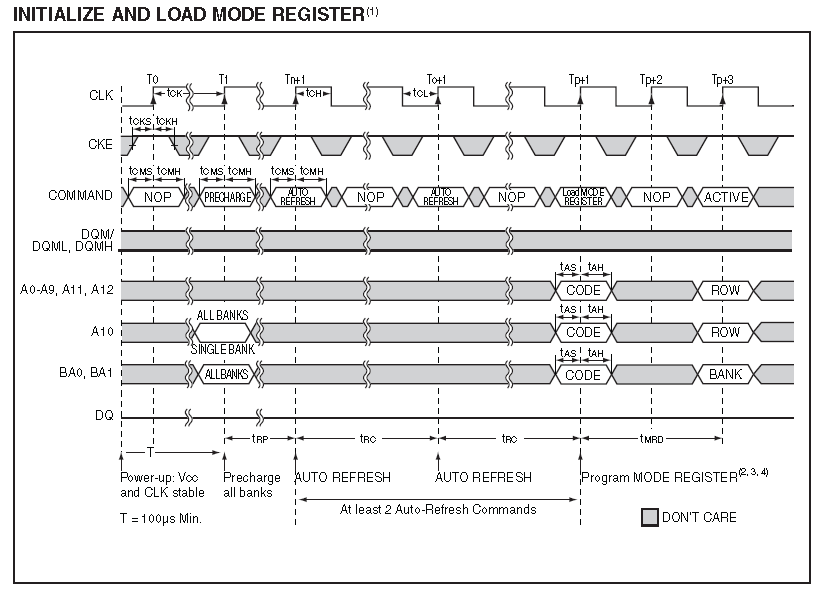

The data sheet for my SDRAM includes the following timing diagram for startup.

According to this, the clock (CLK) needs to be stable prior to starting the 100 us delay. The text description also implies that CLKE needs to be high during this period.

What starts the SDRAM CLK running? And what causes CLKE to go high?

Our initialization sequence is similar to that recommended in the MCF548x RM except that we done enable auto refresh until after we initialize the MODE register. We are also seeing an unexplained attempt to load MODE on our oscilloscope that occurs before the first precharge. What could be causing this?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I had received the case you submit. I will handle it and please follow that case. Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

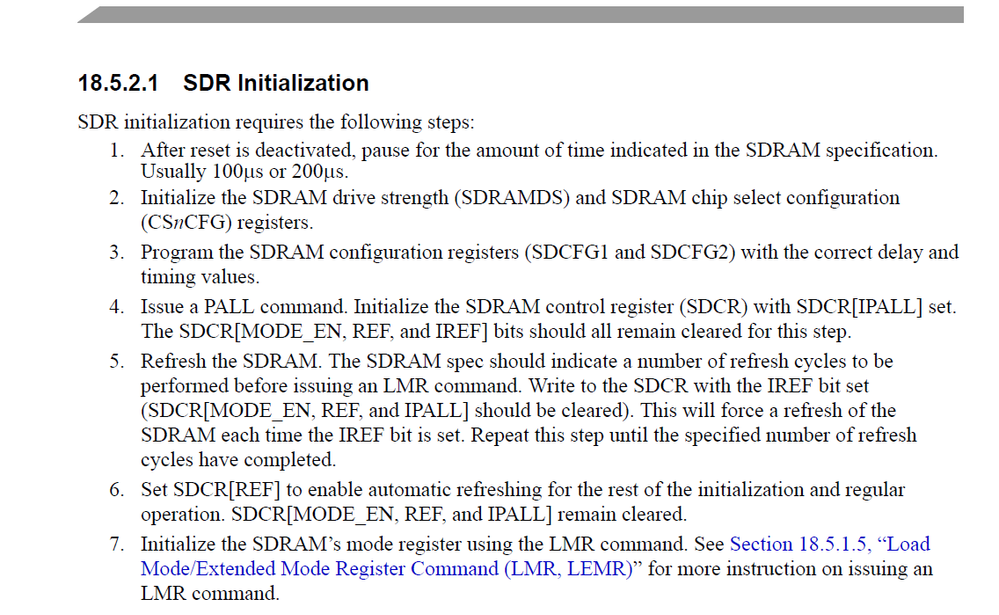

If you look at the reference manual for MCF548x, there list the SDR initialization procedure. From that, it seems that the MODE register really not accessed that early. I do not see your code on system initialization. Anyway, I attached the code we used with MCF548x for you reference.