- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- iMX7 CSI MIPI : Deinterlace/FBUF Stride Configuration

iMX7 CSI MIPI : Deinterlace/FBUF Stride Configuration

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Linux Kernel: v4.9.11

In my on-going battle to get an AD7280M (csi-mipi) working on an i.MX7 I can now capture an image from a PAL camera feed. Stable picture, correct colors, picture is clear....BUT.... I have 2 copies of the image, one on top of the other.

I am guessing that this is due to the ADV7280M sending INTERLACED picture, and I am not set-up for this.

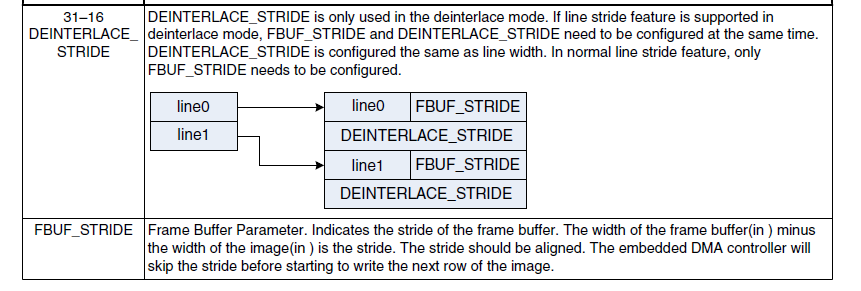

To de-interlace the two images, I have enabled CSI de-interlacing (CSI_CSICR18 bit2) but I don't understand what to set register CSI_CSIFBUF_PARA.

The mx6s_capture.c driver configures FBUF_STRIDE to the image pixel width i.e. 720 for my PAL input of 720x576, but according to the iMX7's manual,

it should be set to Width of Frame Buffer (in double words) - Width of Image (in double words).

This raises the question of how do I find the Width of Frame Buffer ??

I have seen post i.mx6ul CSI receive interlace ccir656 video issue which asks the same question but without any conclusion:

[Please note the iMX7. For other CSI MIPI posts, on the (very) rare occasions I've had a reply from NXP-support-staff, they have quoted advice only relevant to the iMX6 with an IPU which uses a completely different driver framework].

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Yuri,

I have a solution working now for both PROGRESSIVE and INTERLACED from the ADV7280M.

However, I don't agree with your advice of setting FBUF_STRIDE. I have to set FBUF_STRIDE to 0 (zero) for a correct image. If I use 720 (line width) or 1440 (2x line width) the image is incorrect (garbled).

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

FBUF_STRIDE should be set to two lines, since after finished one, say field 0,

line, the buffer point will jump two lines, skipping field 1 line.

The embedded DMA has two parameters for data transfer: start address

(for line) and (line) length. CSI_CSIFBUF_PARA provides them.

Have a great day,

Yuri

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Yuri,

I have a solution working now for both PROGRESSIVE and INTERLACED from the ADV7280M.

However, I don't agree with your advice of setting FBUF_STRIDE. I have to set FBUF_STRIDE to 0 (zero) for a correct image. If I use 720 (line width) or 1440 (2x line width) the image is incorrect (garbled).

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Yuri,

This does not agree with the documentation! Is the documentation therefore wrong??

From what you are saying:

- for progressive (non-interlaced) PAL (720x576), FBUF_STRIDE should be set to 720

- for interlaced PAL (2-fields of 720x288), FBUF_STRIDE should be set to 1440 (2 x 720)

And, I just ignore DEINTERLACE_STRIDE and leave it as 0 ??