- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- CodeWarrior

- :

- CodeWarrior for MCU

- :

- Re: Fixup overflow error in _vect...

Fixup overflow error in _vect...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi All,

When I upgraded from mc9s08dz60 to mc9s08dz96, I got this error:

Fixup overflow in _vect2, to SysTimer_Interrupt type 1, at offset 0xC

Fixup overflow in _vect2, to RFIRQ_Interrupt type 1, at offset 0x12

Fixup overflow in _vect2, to Cpu_Interrupt type 1, at offset 0xE

Fixup overflow in _vect2, to Cpu_Interrupt type 1, at offset 0xA

......

My code was working with mc9s12dz60, how can I fix this?

Thanks!

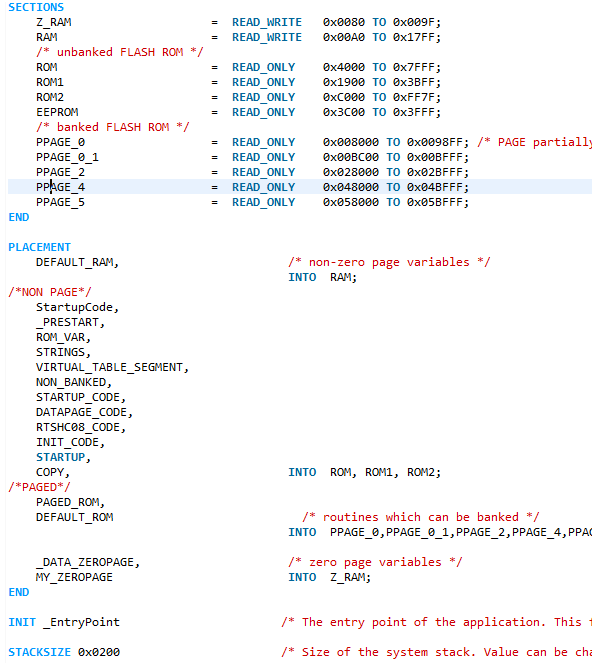

prm file:

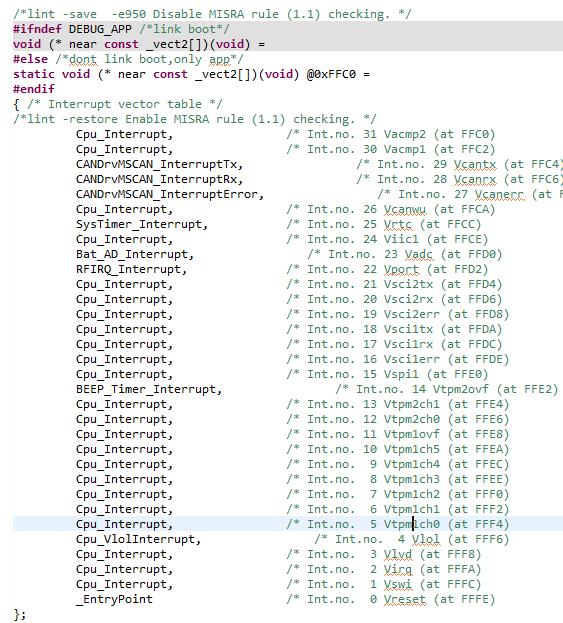

Interrupt vector table:

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Please check where are the ISRs placed into. I assume they are placed in paged/banked memory - DEFAULT_ROM.

I'd recommend you to add an explicit pragma to place the ISR into non-banked memory segment e.g see the snippet below:

#pragma push

#pragma CODE_SEG __NEAR_SEG NON_BANKED

interrupt void SysTimer_Interrupt(void);

#pragma popHope it helps.

S.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Please check where are the ISRs placed into. I assume they are placed in paged/banked memory - DEFAULT_ROM.

I'd recommend you to add an explicit pragma to place the ISR into non-banked memory segment e.g see the snippet below:

#pragma push

#pragma CODE_SEG __NEAR_SEG NON_BANKED

interrupt void SysTimer_Interrupt(void);

#pragma popHope it helps.

S.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Stanislav,

Thanks for your reply, I according to your suggestions tried and solved the problem.

But I don't understand why can't the ISRs are placed in paged/banked memory, My interrupt vector table are placed in a fixed cpu address @0xFFC0.

Best Regards!

Jiaxing Deng

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

This is because of how interrupt vector table is implemented on HCS08/HCs12 architectures.

There are just 16 bits (near) pointer dedicated to each interrupt vector - this is hardwired.

It makes sense since for a long time HC08 cores didn't have more than 64kB of flash memory. To keep backward compatibility it is the same on devices with more 64kB of Flash.

Now on such a devices you need to take special care about where ISR routines are placed so they can be accessed by near 16bit pointer.

Hope it helps.

Stan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jiaxing Deng,

I wonder you have overlap vector table definition in your code.

Please upload your demo project here. I will check.

Have a great day,

Jennie Zhang

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jennie Zhang,

Thanks for your reply.

I'm sorry I can't upload my project, but I solved the problem through @Stanislav Sliva's tips.

Thank you again.