- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors Knowledge Base

- :

- How to locate i.MX6Q pfd issue(ERR006282) without JTAG tools

How to locate i.MX6Q pfd issue(ERR006282) without JTAG tools

- Subscribe to RSS Feed

- Mark as New

- Mark as Read

- Bookmark

- Subscribe

- Printer Friendly Page

- Report Inappropriate Content

How to locate i.MX6Q pfd issue(ERR006282) without JTAG tools

How to locate i.MX6Q pfd issue(ERR006282) without JTAG tools

When a board is brought up and the ddr test by link of "https://community.nxp.com/docs/DOC-96412' hashttps://community.nxp.com/docs/DOC-96412' hashttps://community.freescale.com/docs/DOC-96412' hashttps://community.nxp.com/docs/DOC-96412' has been verified, some of boards will have pfd issue(ERR006282). It is suggested that below method could be used to check the issue.The detail steps are:

As boards may have no jtag port, the internal usdhc4 root clock out needs to be remapped. When “CUP not initialized” issue has been seen and in download mode, DDR test tools can be used with the script to remap clock output.

Please check the attached for test script and the empty the binary. Put the two files to DDR stress test tool folder “DDR_Stress_Tester\binary\”. The attached ddr-stress-test-mx6dq.bin is an empty file. Please backup the original file first. After eMMC boot failed and in download mode, run command “DDR_Stress_Tester.exe -t mx6x -df test.inc” on PC side. There is no clock output on GPIO19. For normal test, please erase the eMMC chip and boot the board. It will also fail to boot and run into download mode. After run “DDR_Stress_Tester.exe -t mx6x -df test.inc” , clock can be measured from GPIO19 if no PDF issue happens.

Below is the details:

The script file.

wait = on

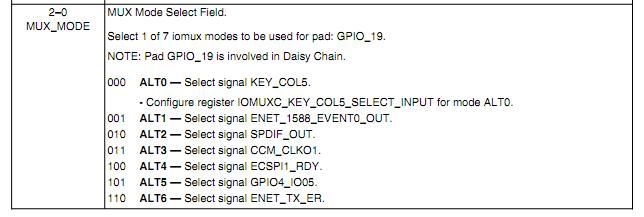

A: Config GPIO19(ENET_ RST_ PHY_B) as CLKO1

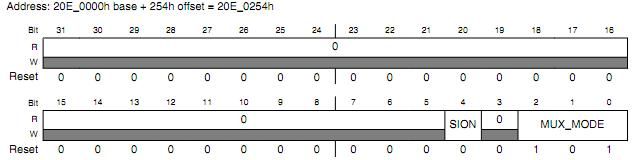

setmem /32 0x020E0254 = 0x3 // Config GPIO19(ENET_ RST_ PHY_B) as CLKO1

On your board, it is R112 for the test point.

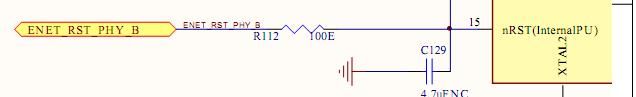

B: enabled, CKO1 output drives cko2 clock, divide by 5, usdhc4_clk_root

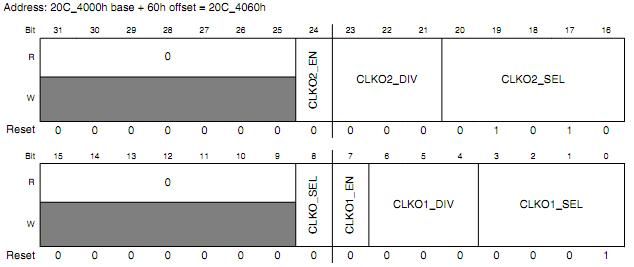

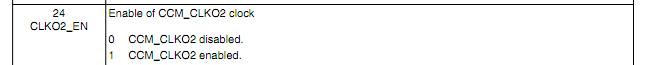

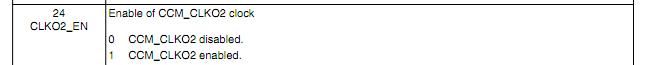

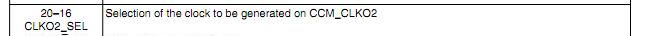

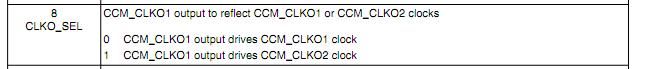

setmem /32 0x020C4060 = 0x01820101 // CKO2 enabled, CKO1 output drives cko2 clock, divide by 5, usdhc4_clk_root

Hex | 0 | 1 | 8 | 2 | 0 | 1 | 0 | 1 | ||||||||||||||||||||||||

Bits | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

Binary | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

And for the normal boot, erase the emmc, and reboot to enter the download mode. There will be no signal output but high voltage on R112. After the script runs, 40Mhz clock will be seen. For the boot fail case, there will be no signal output but high voltage on R112 and 40Mhz clock will be pulled to low.

1: CKO2 enabled

2: divide by 5

3 usdhc4_clk_root

4: CKO1 output drives cko2 clock

5

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

Lily and Johnli,

I made modification on English wording and grammar. Please see if the meanings are accuracy.

Thanks,

Yixing

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

The attached file test.inc is missing for download.

Could you please help upload again?