- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- Topics

- :

- NXP Designs Knowledge Base

- :

- FRWY LS1046A TP CPU Performance Benchmarking Demo

FRWY LS1046A TP CPU Performance Benchmarking Demo

- Subscribe to RSS Feed

- Mark as New

- Mark as Read

- Bookmark

- Subscribe

- Printer Friendly Page

- Report Inappropriate Content

FRWY LS1046A TP CPU Performance Benchmarking Demo

FRWY LS1046A TP CPU Performance Benchmarking Demo

Introduction

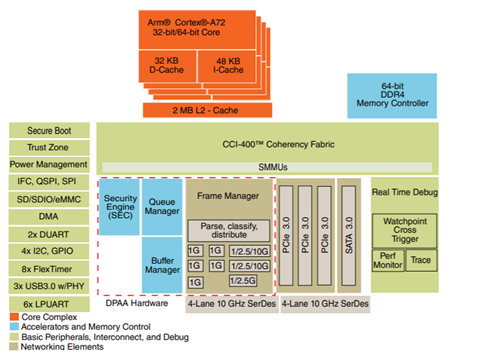

LS1046A has four 32-bit/64-bit Arm® Cortex®-v8 A72 CPUs arranged as a single cluster of four cores. LS1046A shares a single 2 MB L2 with and maximum operation of 1.2 GHz, three PCI Express 3.0 controllers in a 23 mm x 23 mm package.

Overview

The following demo is part of a bundle of examples that shortly will be available in the LSDK. As can be seen in the video, there is a menu for the user to select the desired demo and start testing the different approaches the FRWY LS1046A TPU is capable of executing.

This example intends to show the CPU performance according to CoreMark or Dhrystone metrics. This results in CoreMarks/mW or DMIPS performance running on the LS1046A. The user is able to select the number of cores to use for the test and then the results come out as Performance (Iterations/second) and Watts. This is intended to show the customers the LS1046A capabilities of pure CPU performance despite the oriented application. With a cost lower than 10 dollars per unit, the LS1046A returns 32,000 CoreMarks while consuming an average of 10 W working at 1.2 GHz.

Block Diagram

Video

Products

| NXP Product | Link |

| FRWY LS1046A TP | LS1046A Freeway Board | NXP |