- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- General Purpose Microcontrollers

- :

- LPC Microcontrollers Knowledge Base

- :

- Understanding LPC55S6x Revisions and Tools

Understanding LPC55S6x Revisions and Tools

- Subscribe to RSS Feed

- Mark as New

- Mark as Read

- Bookmark

- Subscribe

- Printer Friendly Page

- Report Inappropriate Content

Understanding LPC55S6x Revisions and Tools

Understanding LPC55S6x Revisions and Tools

At the time of the latest update to this article, the latest silicon revision of the LPC55S6x is revision 1B. Since Nov,2019, all the LPCXpresso55S69 EVK boards marked as Revision A2 or A3 are equipped with revision 1B silicon. Initial production boards that have 0A silicon installed are marked Revision A1.

NXP introduced its new debug session request functionality on silicon revision 1B. For some IDE versions, the method of initiating a debug session is designed for current 1B silicon revisions and will result in an endless loop when used on older revision 0A parts due to the older revision not implementing some aspects of the handshake protocol. The protocol for this debug connection method, including handling of both 0A and later silicon revisions correctly, is included in the latest LPC55S6x/S2x/2x User Manual, section Debug session protocol.

IDE Considerations

MCUXpresso IDE

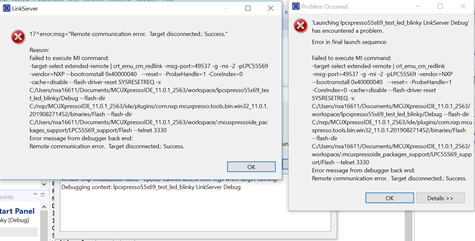

MCUXpresso IDE v11.0.1, incorrectly only supports silicon revision 1B debug session requests and cannot silicon to revision 0A parts in some situations. When connecting LPCXpresso55S69 Revision A1 board, you may have connection error like this:

NXP released an MCUXpresso IDE v11.0.1 LPC55xx Debug Hotfix1 for this issue. Please follow the steps to fix the issue below if you have to use IDE v11.0.1 with silicon revision 0A; however it is recommended to update to the latest version of the IDE instead of taking this approach:

IAR

According to our test:

IAR Embedded Workbench for ARM v8.42 and later can support both silicon revision 1B and 0A production without issue, which can be downloaded from

https://www.iar.com/iar-embedded-workbench/tools-for-arm/arm-cortex-m-edition/

Note: The IAR 8.50.5 changed the CMSIS-DAP debug support for trustzone feature. There is known debug issue with the combination of IAR 8.50.5+SDK2.8.0. Thus our recommendation is:

- Use IAR 8.50.5 with SDK2.8.0

- Use IAR 8.40.2 with SDK 2.7.1

Keil MDK

Both Keil MDK v5.28 and v5.29+ latest LPC55S69 pack v12.01 can support silicon revision 1B without problem but cannot support silicon revision 0A.

LPC55S69 Revision 0A vs. 1B differences summary

|

Silicon Revision |

0A production |

1B production |

|

Board Revision |

A1 |

A2 |

|

Deliver Date |

Before Nov,2019 |

After Nov,2019 |

|

Debug Access handshake |

Supported but not required. Handshake signaling partially supported |

Required |

|

Secure Boot Revision |

SB2.0 |

SB2.1 |

|

Maximum CPU Frequency |

100MHz |

150MHz |

|

IDE revision required |

1. MCUXpresso IDE v11.0.0 and older 2. MCUXpresso IDE v11.0.1 + hotfix1 3. MCUXpresso IDE 11.1 and later |

MCUXpresso IDE v11.0.0 and newer |

|

SDK version |

SDK2.5 and newer are supported; SDK2.6.3 and newer are recommended |

SDK2.6.3 and newer |

LPC55S69 Defect Fix: 0A vs. 1B

|

0A Production |

1B Production |

|

Defect: For PRINCE encrypted region, partial erase cannot be performed |

Fixed |

|

Defect: For PUF based key provisioning, a reset must be performed |

Fixed |

|

Defect: Unprotected sub regions in PRINCE defined regions cannot be used. |

Fixed |

|

Defect: Last page of image is erased when simultaneously programming the signed image and CFPA region |

Fixed |

|

Defect: PHY does not auto-power down in suspend mode |

Fixed |

For more detail, see Errata sheet LPC55S6x which can be downloaded from NXP web site.

Pre-production Silicon:

Note that NO BOARDS WERE EVER SOLD THROUGH DISTRIBUTION WITH PRE-PRODUCTION SILICON. In case you have board marked with Revision 1, 2 ,A, or A1 board with 1B silicon, contact NXP to ask for production replacement.

Get Silicon Revision:

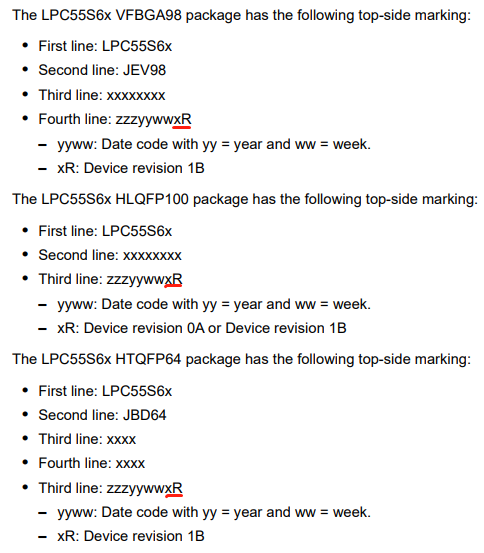

The silicon revision info is marked on the chip and board revision is marked on the board silkscreen. For silicon revision marking information, please consult LPC55S6x Data Sheet section 4. Marking . Below is an example of silicon revision marking information where revision is highlighted in red:

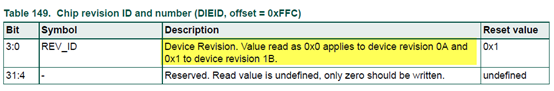

The user application can also get the silicon revision through chip revision ID and number: SYSCON->DIEID:

The English and Chinese version documents are attached.