- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers Knowledge Base

- :

- SWD protocol test on read/write register

SWD protocol test on read/write register

- Subscribe to RSS Feed

- Mark as New

- Mark as Read

- Bookmark

- Subscribe

- Printer Friendly Page

- Report Inappropriate Content

SWD protocol test on read/write register

SWD protocol test on read/write register

The board used: FRDM-KE02

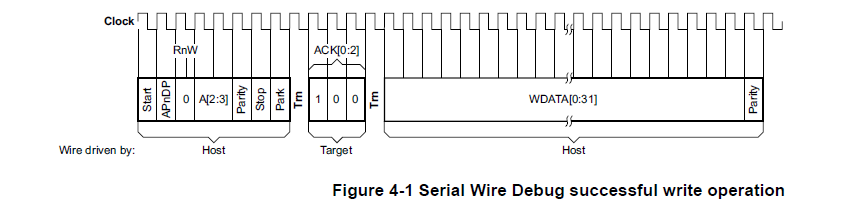

SWD: The ARM Serial Wire Debug interface uses a single bidirectional data connection(SWDIO) and a separate clock (SWDCLK) to transfer data synchronously. An operation on the wire consists of two or three phases:

Packet request The external host debugger issues a request to the DP. The DP is the target of the request.

Acknowledge response The target sends an acknowledge response to the host.

Data transfer phase

First enter into SWD mode: Send at least 50 SWCLKTCK cycles with SWDIOTMS HIGH and 0xE79E. This ensures that the current interface is in its reset state and enable the SWD mode.

uint8_t SWJ_JTAG2SWD(void)

{

uint32_t i;

SWDIO_SET();

for(i = 0; i < 56; i++)

{

SW_CLOCK_CYCLE();

}

SWJ_SendData(0xE79E);//SWJ_SendData(0xB76D);以后遇到再加

for(i = 0; i < 56; i++)

{

SW_CLOCK_CYCLE();

}

SWDIO_CLR();

for(i = 0; i < 16; i++)

{

SW_CLOCK_CYCLE();

}

return 0;

}

Then write DP/AP register. A successful write operation is as below:

DP Register:

Address Read Write

0x00 IDCODE ABORT

0x04 CTRL/STAT CTRL/STAT

0x08 RESEND SELECT

0x0C RDBUFF N/A

Address Read Write

0x00 CSW CSW

0x04 TAR TAR

0x08 N/A N/A

0x0C DRW DRW

0xFC IDR N/A

Read IDCODE:

uint8_t SWJ_ReadDP(uint8_t adr, uint32_t *val)

{

uint32_t tmp_in;

uint8_t ack;

uint8_t err;

tmp_in = SWD_REG_DP | SWD_REG_R | SWD_REG_ADR(adr);

ack = SWD_Transfer(tmp_in, val);

(ack == DAP_TRANSFER_OK) ? (err = 0) : (err = 1);

return err;

}

uint8_t SWJ_ReadAP(uint32_t adr, uint32_t *val)

{

uint8_t tmp_in, ack, err;

uint32_t apsel = adr & APSEL;

uint32_t bank_sel = adr & APBANKSEL;

if(SWJ_WriteDP(DP_SELECT, apsel | bank_sel))

{

return 1;

}

tmp_in = SWD_REG_AP | SWD_REG_R | SWD_REG_ADR(adr);

/* first dummy read */

ack = SWD_Transfer(tmp_in, val);

ack = SWD_Transfer(tmp_in, val);

(ack == DAP_TRANSFER_OK) ? (err = 0) : (err = 1);

return err;

}